文章目录

工欲善其事,必先利其器。

本节博客,废话可能比较多,偏软文,但主要是为了给大家介绍这些工具的重要性,还是请大家耐心看完,对你IC设计很有帮助的。

!!!一定要看完!!!

一、简介

可不要小看了这一节,为了更好的进行Verilog开发,提升我们的效率,我们首先需要掌握最基本的开发工具,包括但不限于(只列举部分常见工具):

-

编辑器

- GVIM、VIM(编辑器之神)

- Emacs(神之编辑器)

- VSCode

- Sublime

- Notepad++

- …

-

仿真工具

- ModelSim

- NC-Launch

- iVerilog

- …

-

波形查看(Debug)

- Debussy(Verdi)

- …

-

逻辑综合

- Design compiler

- …

-

画时序图

- TimeGen

- TimingDesigner

- …

-

后端

- ICC

- ICCII

- …

-

其他

- Vivado

- QuartusII

- …

-

…

软件千奇百怪,各式各样,不同公司、不同学校用的都各不相同。我们在此不会对所有软件进行讲解,只会为大家推荐我认为比较常用的一些工具。这些工具是我的恩师教给我的,在数字IC入门上基本上也是必备的,绝对不会太偏,大家放心学。而且老话说得好,技多不压身,祝大家学习快乐hhh。

以下推荐都是针对Windows平台。

二、编辑器

对于编辑器,我极力推荐VIM/GVIM。

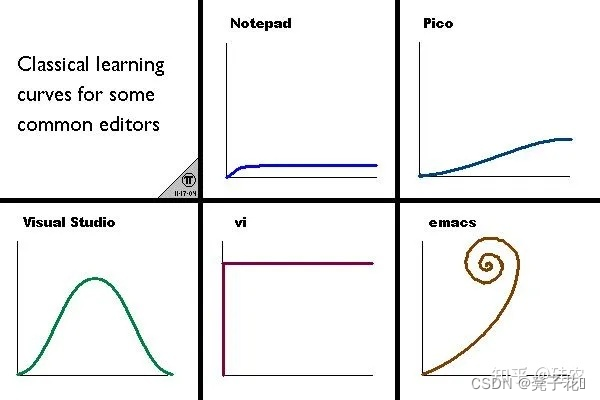

话说这个世界上只有三种编辑器,VIM, Emacs 和 其他编辑器,其中Vim被称作编辑器之神,Emacs被称其神的编辑器,当然,其他编辑器永远只能是其他编辑器。

以上来自:地表最强开源gVim编写Verilog插件.

(一)VIM/GVIM

VIM!编辑器之神!

在使用VIM之前,我一直用的VSCode,VSCode对于新手及其友好,但当你写代码写多的时候,你就会发现,啊!好像效率也不是很高啊,这个时候你就会想起网上大家都推荐的VIM,从瞎**按,到行云流水,你会逐渐爱上这个编辑器,也就慢慢明白了为什么大家都在推荐这个。

作为文本编辑器,VIM的速度和效率是其它文本编辑器难以望其项背的。作为一个数字ICer,工程开发大部分都应该是在Linux系统上完成的,而vim是远程登录终端上唯一可用的编辑器。

所以你如果想在数字IC这条道路上继续修行,我极力推荐你花费一些时间学习一下VIM。

相信大部分同学平时都是在Windows下进行开发程序的,而GVIM是VIM下的Windows版本,是一个GUI程序。GVIM有丰富的插件,其自定义程度极高,可通过修改配置文件实现我们想要的功能。总之,熟悉GVIM后,会颠覆我们对传统文本编辑器的认知,你会一次一次地被折服。

GVIM/VIM的使用命令及其的多,我用了很久,也只能说是学到了凤毛麟角,而对于初学者,并不需要掌握太多,只需掌握一些基本命令,具体请查看:gvim【一】【安装和基本使用】

此外,对于Verilog,GVIM有一个非常方便的功能,类似于起别名。通过这个功能,你可以设置常用的一些模板,可以大大提升你的编程效率。具体使用请查看:gvim【二】【ab命令快速制作verilog模板】

当然你也可以定制自己的GVIM,使其变得更加方便使用,GVIM具体配置请查看:gvim【三】【_vimrc配置】

GVIM在基本的Verilog编程中只需掌握以上三篇文章中提到的技能即可,后续想学习拓展的命令,需要什么搜什么。至于VSCode的使用,相信大家基本都了解,就不具体讲解了。Emacs我也不会哈哈哈。

(二)编程流程

让我猜一猜,是不是目前很多童鞋编写Verilog程序,都是先点一下Vivado,然后等个十几秒,然后开始新建工程,新建文件,开始编程。等待Vivado打开的过程中,我们可能早就打开了手机,刷刷小破站,看看微信女神是不是回你了,然后已经毫无学习的想法。。。。

嗯,被我猜中的童鞋不要怕,因为我一开始也是这么一个流程(ಥ_ಥ) 。大家注意哦,并没有说这种方式不好,只不过这种方法对于特定的工程来说,似乎并不是最优解。

看了我上面为大家分享的编辑器的那篇文章的同学,相信都知道GVIM有一个Verilog模板,可以大大减少我们不必要的工作量。当你在点Vivado的时候,我已经新建好了.v文件,然后输入MKmb(我自己起的模板别名),敲回车,一个模块模板就建好了。整个过程不超过3s(没错,3s真男人哈哈哈),同时如果你已经构思好你模块的思路,那么就可以直接编程。编辑好端口,直接列操作,输入输出搞定。具体可以查看gvim【二】【ab命令快速制作verilog模板】中的演示。

可以看出,使用这种编辑器就已经可以提升一些效率了,所以建议大家有时间一定要学一下GVIM。

三、仿真工具

编完代码后,肯定就是去进行仿真啦。使用Vivado的同学动动小手,点点按钮,轻轻松松完成编译,然后开始仿真,添加波形。我也很喜欢这种方式哈哈哈,但是有一些问题,首先就是Vivado编译速度问题(可能是我的刻板印象,总感觉Vivado编译时间会相对长一点,当然Vivado可以选择使用ModelSim进行编译),然后就是查看波形,我个人感觉Vivado在查看波形的时候是比较不方便的:当你需要添加一些其他信号的时候,Vivado默认不显示新添加的信号波形,所以你需要重新run一遍,懂的都懂,当你仿真时间比较久时,这是非常浪费时间的。

此外,事实上业界在进行IC设计时,除了需要使用Xilinx的板子和IP,其他情况是很少使用Vivado的(我导师说的,我不太了解业界,如果说错了,请轻喷hhh)。一个原因是Vivado集成功能越来越多,打开一次费时太久;再一个是Vivado的编译和仿真问题,业界还是对Modelsim、NClaunch等工具的认可度更高。

所以说了这么多,就一个中心思想:大家可以使用一些业界经常用的工具,非必要情况下,不使用Vivado,来提升你的效率。当然,这都是我个人看法,如有其他意见,我虚心接受。

仿真工具我常用的是ModelSim,NClaunch也有接触过一些,但由于NClaunch是Linux系统上用的比较多,而且破姐版本比较少,所以这里讲解ModelSim的使用。

ModelSim有两种开发方式,一种是通过图形界面,和Vivado一样,也是添加源文件,然后编译,仿真等等。嗯,如果只是这么简单的操作,那我就没有必要给大家介绍啦。另一种是即将为大家介绍的脚本化的方法,可以解放你的双手,不用点那么多按钮,直接一行命令,编译仿真一气呵成(✪ω✪)。

有些童鞋看到脚本两字就开始害怕了,内心忐忑:啊 ~ 人家怕怕 ~ 脚本好可怕 ~ 我不会那些命令 ~ 好多啊 ~ 我记不住 ~,咳咳,有点sao了…,但我告诉大家,我其实也记不住那么多命令,所以你弄一个GVIM模板就行了,或者把一个通用文件保存下来,下次使用的时候直接复制过来,这不就解决了嘛。

ModelSim的脚本化方法请查看:Modelsim的tcl命令

大家一定要看上面这个文章,真的可以大大提升你的效率!

仿真就讲这么多,当你用熟了之后,你就会发现Vivado,真的慢。。。

四、波形查看/Debug

ModelSim可以查看波形,Vivado也可以查看波形,那么为什么还要单独开一节讲解波形查看呢?

代码调试的多的同学会发现一个问题,Verilog和C语言、C++等软件语言不同,软件语言是可以调试的,遇到bug不要慌,先Debug一下,一行一行查看代码中间结果,找到问题所在。

但Verilog仿真时遇到错误是没办法一行一行去调试的,为啥呢,因为Verilog HDL,全称为Verilog Hardware Description Language,是一种硬件描述语言,硬件在实际执行的时候,并不是一行一行执行的,而是并行的。所以去一行一行调试非常不现实,但我们还是有方法可以Debug我们的Verilog代码,那就是使用Debussy(可能其他软件也可以,但我只会Debussy)。Debussy用于debug查看波形更为方便,能在源代码、原理图和波形三者之间进行切换。

具体使用方法请查看:ModelSim+Debussy联调

如果你想要在数字IC道路上越走越远,请仔细学习上面的文章。

五、逻辑综合

逻辑综合不用多说了,除了Vivado之外,常用的是Design Compiler,这个工具使用起来也是脚本化的方法多一些,而且对于初学者来说理解比较困难,请查看:Synopsys逻辑综合及DesignCompiler的使用

六、画时序图

有些时候大家是需要写一些报告,做一些汇报的,那我们可不可以自己手动画一些好看的波形图呢,答案是肯定的。也有相应的软件可以使用,用的比较多的是TimeGen和TimingDesigner,使用方法和软件获取请查看:画时序图软件——TimeGen和TimingDesigner免费下载

七、后端

有关后端工具的使用不是我们本系列博客的重点,所以这里不作太多介绍,有想了解的同学请查看:

八、编程规范

本来想集中讲一下Verilog的一些编程规范的,但是考虑到这样讲太空洞,看完也可能记不住说了个啥,所以这里先不讲解了,放到后面实现代码时遇到什么问题再具体进行讲解U•ェ•*U 。

在网上看到一篇讲的比较好一点的,大家可以先学习一下:(数字 IC 设计)0.2 编码风格

脚下留心

如果你想在数字IC道路上越走越远,光有这些知识储备是不够的,尤其是有些同学只学了Verilog,对Verilog非常感兴趣,然后就经常找很多Verilog的东西做。其实随着高层次综合语言(High Level Synthesis,HLS)的发展,Verilog势必会被取代,就像汇编语言一样最终成为底层语言(个人看法,应该只是时间问题)。所以希望大家尽量扩展自己的知识面,努力向国内外大神看齐,条件允许的条件下多学习一些先进的东西,“中国芯”就靠你们了。其他需要学习的知识可以参考:数字IC设计,学完verilog语法,还需要学习什么?

好的,本节就先讲到这里,如果你有收获且乐意的话,麻烦点个赞哦,收藏也可以哇( ̄▽ ̄)~*

博客结构安排

本系列博客共分为5篇:

第一篇对一些处理器基础知识进行简单讲解,并讲清楚实验要求。

第二篇从指令、寄存器、汇编器的角度对设计处理器所需要的基础知识进行较为详细的讲解,并对实验所需汇编程序进行了分析。

第三篇讲解数字IC设计所需要的一些工具以及使用方法,并讲解了一些编程规范。

第四篇主要是针对单周期CPU的基础理论和模块设计进行讲解,在讲Verilog实现的时候,顺带讲了很多编程规范。

本系列其他博客

- 一个简单LEGv8处理器的Verilog实现【一】【实验简介】

- 一个简单LEGv8处理器的Verilog实现【二】【基础知识与实验分析】

- 一个简单LEGv8处理器的Verilog实现【三】【工具使用和编程规范】

- 一个简单LEGv8处理器的Verilog实现【四】【单周期实现基础知识及模块设计讲解】

源码下载

参考资料

- 《MK.Computer.Organization.and.Design.The.Hardware.Software.Interface.ARM.Edition》

参考资料下载

链接:https://pan.baidu.com/s/1dtpFTsJ5fdEmnPDyX66U1Q

提取码:b26b

4011

4011

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?