数字逻辑综合工具-DC-05

——环境约束

环境设置通常包含以下几个方面:

1、 Input drivers和transition times(设置驱动能力、转换时间,而不是一个理想信号)

2、 Capacitive output loads(设置要驱动的电容负载)

3、 PVT(一般选worst case)

4、 内部寄生RC(线负载模型)

输入驱动:

为什么要加输入驱动?

一般来说要从工艺库里面挑一个合适的单元去激励输入端口。如果不加驱动单元,DC就会认为输入的跳变是理想的,如果指定了驱动单元,输入就会有一个斜率,从而内部逻辑的延时会更准确(传播延时跟输入信号的transition time是有关系的)。

为了保证芯片能正常工作,一般会选择最坏情况的SS去做综合。

为输出的管脚建模:

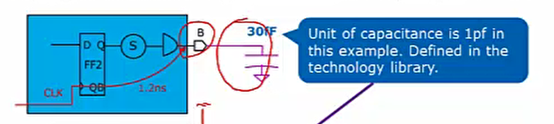

set_load [expr 30.0/1000] [get_ports B]

单位是在工艺库里给出的,通过list_lib看用的哪个工艺库, report_lib把lib的信息打出来

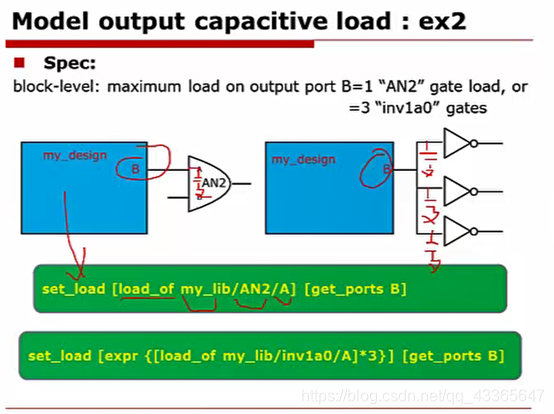

set_load [load_of my_lib/AN2/A] [get_ports B]

这边的my_lib是库,AN2是库单元,A是pin脚(是pin脚而不是port,port是跟design对应的,而pin是跟cell对应的)

含义就是:把这个库单元的这个引脚的电容拿出来,加载到B输出端口上

set_load [expr {[load_of my_lib/inv1a0/A]*3}] [get_ports B]

如果有多个fanout,可以用expr计算

【transition time 的影响:】

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

442

442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?