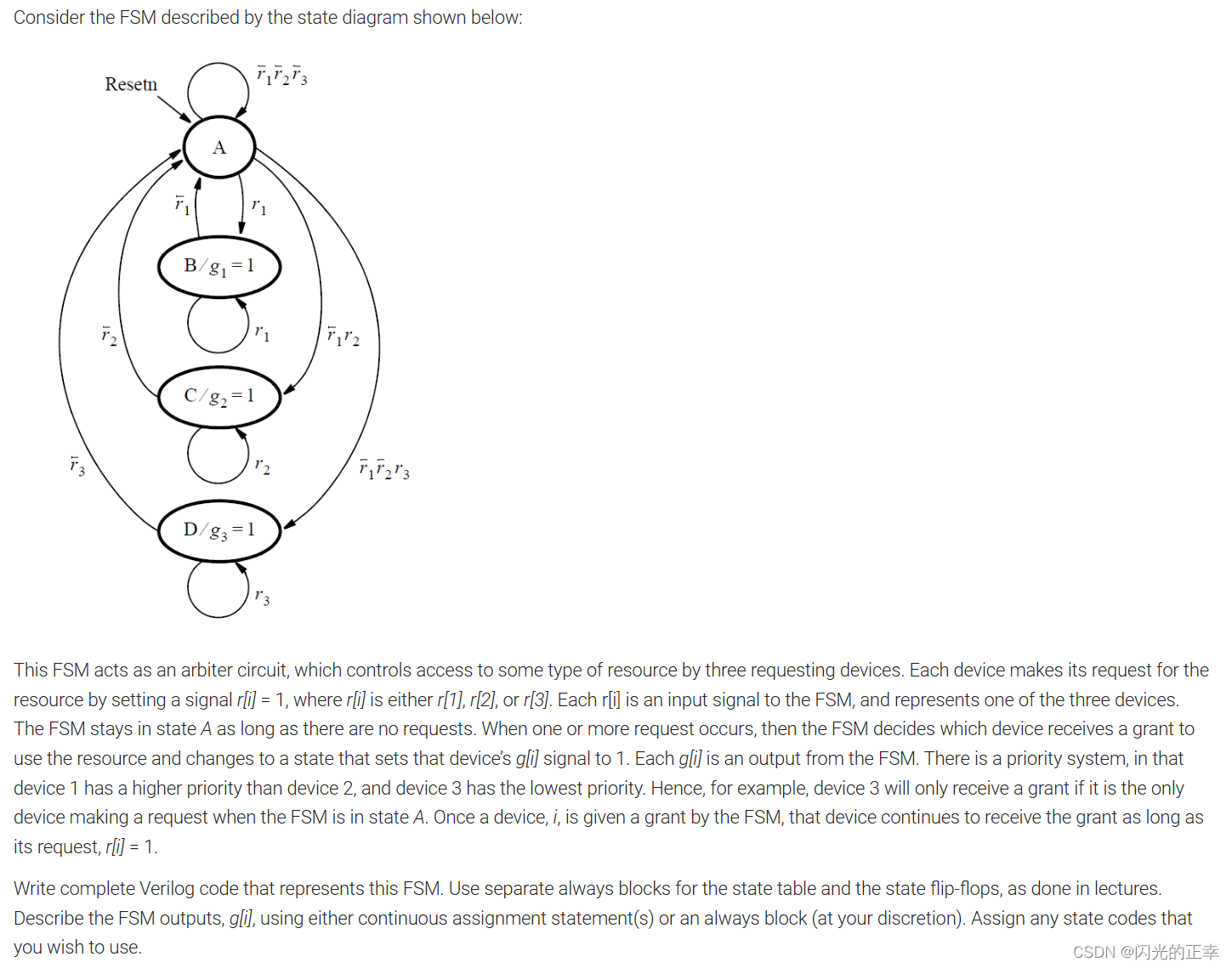

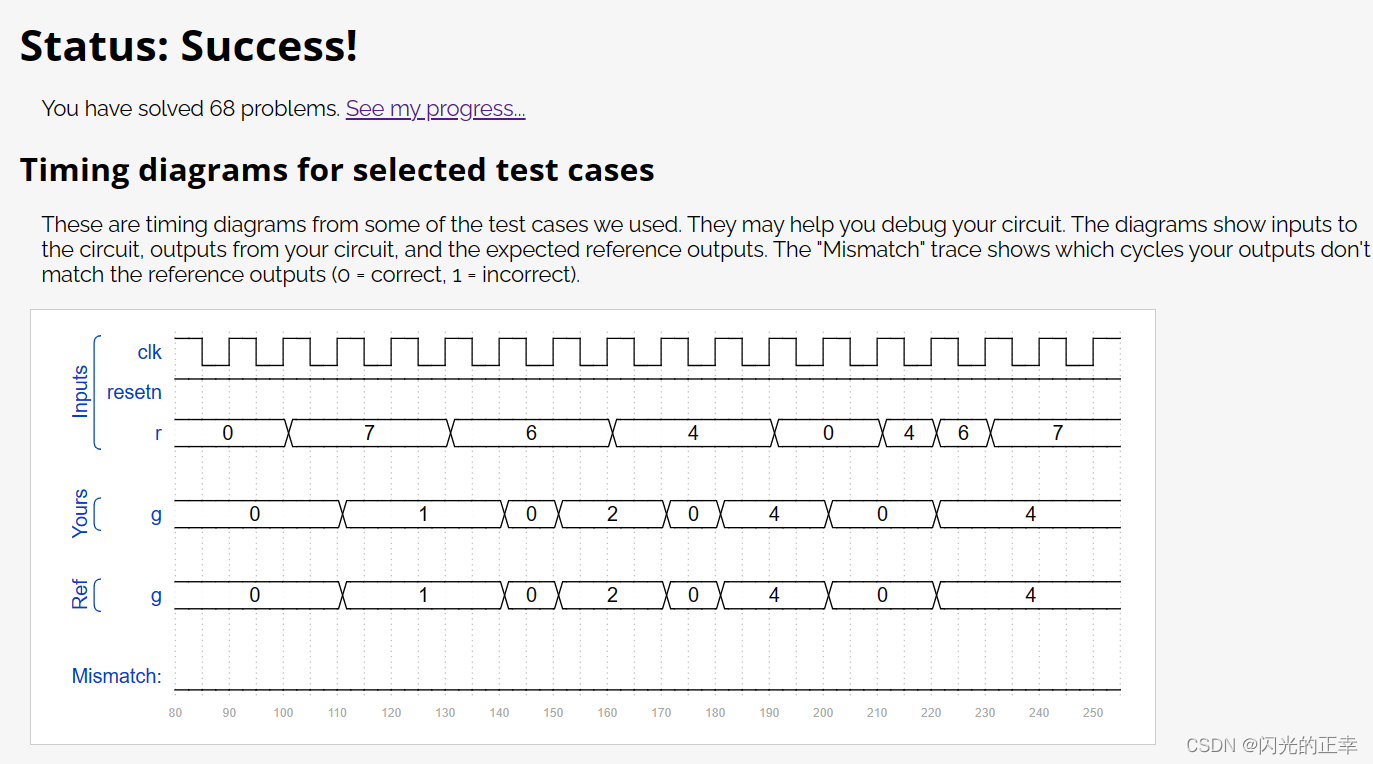

1、这个题一次成功,理清思路,尽管r1有优先级,但是当在C、D状态时。就不看r1的值了

完整代码如下:

module top_module (

input clk,

input resetn, // active-low synchronous reset

input [3:1] r, // request

output [3:1] g // grant

);

reg [2:0]state,next_state;

parameter A=0,B=1,C=2,D=4;

always@(*)begin

case(state)

A:begin

if(r==3'b100)

next_state=D;

else if(r==3'b010||r==3'b110)

next_state=C;

else if(r==3'b000)

next_state=A;

else

next_state=B;

end

B:begin

if(r[1]==1)

next_state=B;

else

next_state=A;

end

C:begin

if(r[2]==1)

next_state=C;

else

next_state=A;

end

D:begin

if(r[3]==1)

next_state=D;

else

next_state=A;

end

default: next_state=A;

endcase

end

always@(posedge clk)begin

if(!resetn)

state<=A;

else

state<=next_state;

end

always@(*)begin

case(state)

A:g=3'b000;

B:g=3'b001;

C:g=3'b010;

D:g=3'b100;

default:g=3'b000;

endcase

end

endmodule

769

769

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?