2.1.2 选择 VHDL 还是 Verilog

VerilogHDL和 VHDL都是用于逻辑设计的硬件描述语言,两者各有优劣,也各有相当多的拥护者,并且都已成为IEEE标准。VHDL于1987年成为IEEE标准,Verilog HDL 则在1995年才正式成为IEEE标准。之所以 VHDL比 Verilog HDL早成为IEEE 标准,这是因为 VHDL是美国军方组织开发的,而Verilog HDL 则是从一个普通民间公司的私有财产转化而来的。

VHDL语言由美国军方所推出,最早通过国际电子工程师学会(IEEE)的标准,在北美及欧洲应用非常普遍。而 VerilogHDL语言则由Gateway 公司提出,这家公司辗转被美国益华科技(Cadence)所并购,并得到美国新思科技(Synopsys)的支持。在得到这两大EDA(Electronic Design Automation,电子设计自动化)公司的支持后,也随后通过了IEEE 标准在美国、日本及中国台湾地区使用非常普遍。

从语言本身的复杂性及易学性来看,VerilogHDL是一种更加容易掌握的硬件描述语言只要有C语言的编程基础,通过二十学时的学习,再加上一段时间的实际操作,可在二至三个月内掌握这种设计技术。而掌握 VHDL设计技术就比较困难,这是因为VHDL不很直观,需要有 Ada编程基础,且代码风格相对较为烦琐。从易学性的角度来看,似乎 Verilog HDL稍占上风。但辩证法告诉我们,事物的特性总是相对的。VHDL的不直观及代码的烦琐,是因为 VHDL语法更加严谨。VerilogHDL语法宽松,因其宽松导致描述具体设计时更容易产生问题,且对于同一个设计,在应用不同EDA工具实现时,可能出现不同的实现结果,给程序交流、复用带来麻烦。国外电子专业很多会在本科阶段教授VHDL,在研究生阶段教授 Verilog HDL。

目前的 Verilog HDL和 VHDL,版本在行为级抽象建模的覆盖范围方面也有所不同。般认为 VerilogHDL在系统级抽象方面比 VHDL略差一些,而在门级开关电路描述方面比VHDL强得多。Verilog在其门级描述的底层,也就是晶体管开关级的描述方面更有优势,即使是 VHDL的设计环境,在底层实质上也会由 Verilog HDL描述的器件库所支持。VerilogHDL较为适合系统级、算法级、RTL级、门级和电路开关级的设计,而对于特大型(千万门级以上)的系统级设计,VHDL更为适合。

对两种语言的特点进行简单比较之后,似乎仍然难以得到明确的答案,如何选择仍然是一个颇为复杂的问题。当遇到这种情况的时候,如果一定要选择的话,也只好采用中国古老的占卜方法了。“向空中扔一个硬币,正面代表 VHDL,反面代表 Verilog HDL。”记得上学的时候,一位风趣的老师曾经教给我们这种做选择题的方法。

其实两种语言的差别并不大,它们的描述能力也是类似的。掌握其中一种语言以后,可以通过短期的学习,较快地学会另一种语言。选择何种语言主要还是看周围人群的使用习惯,这样可以方便日后的学习交流。当然,如果您是集成电路(ASIC)设计人员,则必须掌握 Verilog HDL,因为在IC设计领域,90%以上的公司都是采用 VerilogHDL进行IC设计的;对于PLD/FPGA设计者而言,两种语言可以自由选择。而对有志于成为可编程器件设计的高手来讲,熟练掌握两种语言仅是必须打好的基本功而已。

2.2VHDL 语言基础

学习 HDL语言(包括 VHDL和 Verilog HDL)之前,首先需要明确每条 HDL语句所适合的两种用途:仿真建模以及逻辑综合。HDL语言的一个重要应用在于建立精确的电路仿真模型,比如说可以通过 HDL语言来精确描述晶体管的输入输出信号关系,进而仿真诸如RISC CPU 等复杂的微处器芯片]。这一类HDL语句只能进行仿真建模,不能综合成具体的逻辑电路;HDL语言的另一个应用就是逻辑综合,即直接用HDL语句描述具体逻辑电路,且这些语句也可以直接综合成逻辑门、存储器、加减法器等具体的电路。当然,大部分可以进行逻辑综合的 HDL语句也可以应用于电路的仿真建模。

VHDL语言是一个成熟完整的硬件语言体系,掌握所有的语句并不是一件容易的事情,但是,与C、VC++等语言相比,VHDL语言相对简单得多。更为重要的是,在具体进行工程设计时,最常使用到的 VHDL语句只有几十种而已。这种现象可以套用著名的“二八原则”来解释。比如说,一个单位20%的工作由80%的员工来完成,一个企业20%的客户占整个营业额的80%。同样,在VHDL语言中,最常用的语句还不足所有语句中的20%。本章接下来就对这些使用最为频繁、最为常用的用于逻辑综合的VHDL语句进行介绍。本书工程实例中所使用的仿真语句很少,相关仿真语句将在具体的仿真实例中进行讨论。

2.2.1程序结构

1983年,美国国防部资助开发VHDL硬件描述语言的最初目的在于方便各厂家交流甚高速集成电路设计,后来该语言得到了计算机业界的广泛支持而迅速发展并得到广泛应用1985年,VHDL语言的7.2版发布。1987年5月,结束了VHDL语言7.2版的修正,并发布了语言参考手册。1987年7月,IEEE将修正后的VHDL语言作为标准。1988年至1992年,VHDL根据用户的建议进行了少量修改并于1993年通过。因此VHDL语言有1987版和 1993版两个版本,不过两种版本差别不大,1993版与1987版兼容,且在1987版的基础上稍有补充而已。ISE中编写的代码支持1993版本。

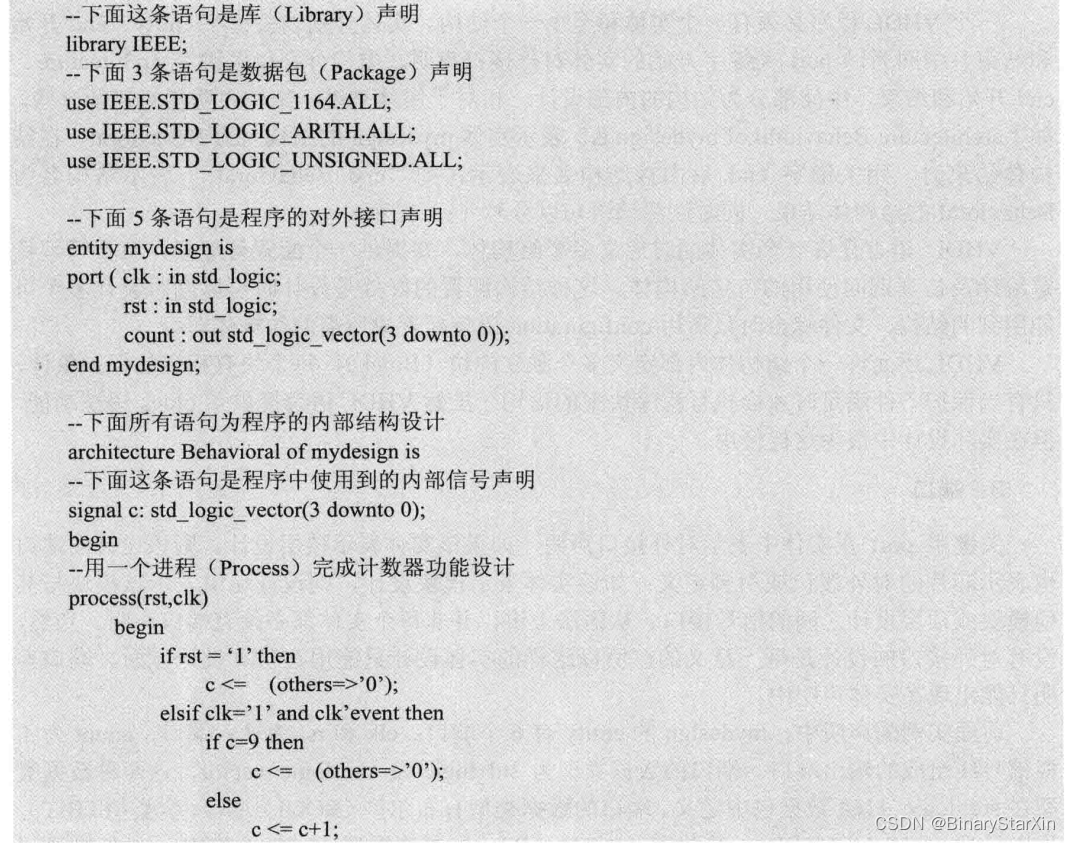

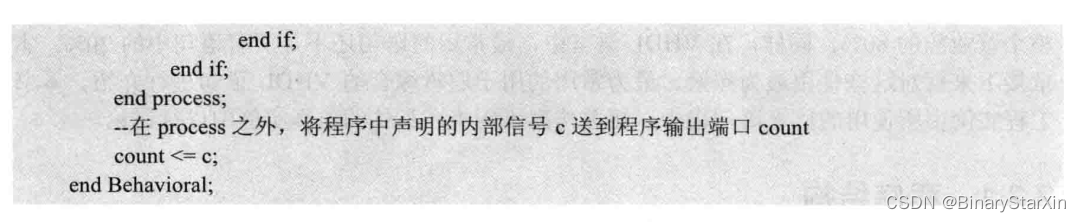

下面是一个完整的 VHDL 程序,程序功能为带异步复位的十进制计数器。VHDL程序主要包括库(Library)及程序包(Package)声明、实体(Entity)及对外接口声明、结构体(Architecture)声明、属性配置等部分,其中Entity与Architecture 是每个 VHDL 程序必须包括的内容,其他部分则依据具体设计而定。

1.库与程序包

1.库与程序包

程序开始为library声明。library是程序所需要参考到的对象集合文件,如声明的对象、调用的函数、过程等,这好比 C++语言中的include 语句所包含的头文件一样。与 C++语言不同的是,在 VHDL中除声明library 外还需要使用use语句指定该library 中具体的程序包,如“uSe IEEE.STD LOGIC UNSIGNED.ALL”。也就是说,一个library中有多个 package,可以用use 语句指定需要使用到的具体package。程序中可以使用ISE软件自带的library,如 STD、IEEE、SYNOPSYS等,也可以使用程序员自己设计编译的library。ISE 环境一般将用户设计编译的library放在当前工程目录下的名为work的library中。我们只需设计package 中的内容,当在ISE中设计好一个package 文件后,对程序进行编译,编译成功后自动将库文件存放在名为work的library中,其他程序文件即可直接调用。

2:实体与结构

一个 VHDL程序必须有一个实体和至少一个结构。实体分别以关键字 entity、end 开始和结束,中间为以 port 关键字开始的实体对外接口声明。结构分别以关键字 architecture、end开始和结束,中间部分为结构的内部设计。相对于实体来讲,结构声明相对复杂一些如“architecture Behavioral ofmydesignis”表示实体 mydesign的结构名为 Behavioral。在结构体结束时,用关键字end后面接结构名来表示,如“endBehavioral;”表示结构名为Behavioral的结构体结束,同时注意该语句以分号(;)结束。

VHDL 语言允许一个实体同时定义多个结构体,并提供一个配置管理器,负责管理特定编译及仿真期间使用的特定结构体。这种结构配置的好处是设计时可以同时设计多个可能用到的结构,文件综合时只需用confguration语句配置成所需的结构体即可。

VHDL还允许一个结构体内部定义多个独立的块(Block),每个块有相应的保护条件,只有当保护条件满足时才会执行程序块中的语句。虽然VHDL语言提供了block 语法功能,,但在实际设计中很少这样使用。

3.端口

关键字port 在实体中表示对外接口声明,如果该实体表示顶层设计,则该设计的端口也表示芯片的对外接口或引脚定义;如该实体表示模块设计,则设计端口表示该模块与其他模块或顶层设计之间的信号接口。从语法上讲,并非每个实体都必须有端口声明。当然,没有对外接口的设计是毫无意义的,所以这样的实体设计只能用在仿真设计方面。端口声明只能出现在实体声明中。

前面实例的声明中,mydesign的entity有6个端口:clk和rst为输入端口,count为4根信号线组成的输出端口。端口的数据类型为stdlogic及stdlogic_vector,这两种数据类型在 std logic 1164数据包中定义。端口的数据类型有布尔型(BOOLEAN)、位类型(BIT)、位向量型(BIT VECTOR)、整数型(INTEGER)、标准逻辑型(STDLOGIC)及标准逻辑向量型(STDLOGIC VECTOR)6种类型;端口模式主要有输入(IN)、输出(OUT)、缓冲(BUFFER)及输入/输出(INOUT)4种。

4.内部结构设计

内部结构设计,即程序的实现部分,包括内部信号声明及代码编辑两部分。architecture与begin 之间为内部声明区,可声明设计内部需用到的信号、常量及组件。内部信号指设计内部产生的中间信号,用于信号之间的连接:常量则指设计体中所用到的固定值;组件指设计实体声明,该实体好比一片IC,用户只关心IC的对外接口及功能,不必关心其内部实现过程。在 begin与end之间就是我们所要编写代码的地方了。VHDL语句可分为两种:写在 process之内的语句和写在 process之外的语句。如果把 process 之内的语句当成一个语句体,process之外的每条语句均可当成一个语句体,则结构体设计中的每个语句体均是并行执行的,各语句体之间的先后顺序可以任意排列。例如,下面两段程序的代码顺序完全颠倒,但程序执行、综合、实现均没有任何差别:

c<=a and b;

f<=d-5;

f<=d-5:

c<=a and b;

d<= c+e;

通常,把写在 process之外的语句所形成的电路叫做组合逻辑电路,把写在process之内的语句所形成的电路叫做时序逻辑电路。写在process之外的语句不需要任何触发信号,而写在 process之内的语句则需要触发信号,即只有当某个信号状态发生变化时,或某个信号出现预期的状态时才会触发 process之内的语句执行。

2.2.2 数据类型

数据类型是已命名的一组值,对象的数据类型定义了该对象可以具有的值和可以对该对象进行的运算。VHDL 语言是一种类型很强的语言,不同类型之间的对象通常不能相互赋值或运算,如下面的语句是不合法的。

Signal stdvec: std logic vector(3 downto 0):=10;

VHDL 语言本身定义了一些基本的数据类型,如标量类型、复合类型、文件类型等,但在具体设计时,我们极少使用VHDL的基本数据类型,大多是使用在基本数据类型基础上重新定义好的各种数据类型。这些重新定义的数据类型大多已在封装好的程序包中定义,只要在程序文件中声明相应的程序包后即可直接使用。接下来只对几种最常用的数据类型进行介绍。

1.数值数据类型(numeric type)

定义数值数据类型的语法为

type类型名isrange(取值范围);

VHDL语言在标准程序包standard中预定义了两种枚举数据类型--INTEGER、REAL.以及INTEGER的两种子类型--NATURAL、POSITIVE。这几种数据类型的定义如下。

type INTEGER is range -2147483647 to 2147483647:type REAL is range -1.7014111e+308 to 1.7014111e+308:subtype NATURAL is INTEGER range 0 to INTEGER'HIGH:subtype POSITIVE is INTEGER range 1 to INTEGER'HIGH;

VHDL语言通过是否带小数点来区分INTEGER(整数)与REAL(实数)数据类型,比如“10.0”为 REAL数据,“10”为INTEGER 数据。FPGA 做实数运算相当麻烦,逻辑综合的程序设计中也不支持实数类型的操作,只可以在仿真测试文件中使用。NATURAL为自然数类型,POSITIVE为正整数类型,这两种数据类型均是INTEGER的子类型。

2.数组数据类型

数组是指由相同数据类型的数据组合在一起而形成的数据类型,VHDL语言在标准程序包 standard 中预定义好了两种数组数据类型 STRING 和 BIT VECTOR。

type STRING is array (POSITIVE range >)of CHARACTER;type BIT VECTOR is array (NATURAL range <>) of BIT;

STRING是指由多个CHARACTER组成的数组类型,BITVECTOR是指由多个BIT数据组成的数组类型,也叫做量或位矢量。尖括号(<>)表示无范围限制,因此STRING的下标范围为正整数(不能为0),BITVECTOR的下标范围为自然数(可以为0)。如果定义数组类型时指明了下标为无限制,则在声明该类型数据时必须指明下标范围。下面是数组应用例子。

Variable name: string(3 downto 0):=“Mike”;

Variable number: bit vector(0 to 7):=x“'f’;Signal count: bit vector(7 downto 0):

我们也可以定义自己的数组数据类型,如type BUSARRAY is array (7 downto 0) of BIT:type COUNTARRAY is array (0 to 7) of BIT;

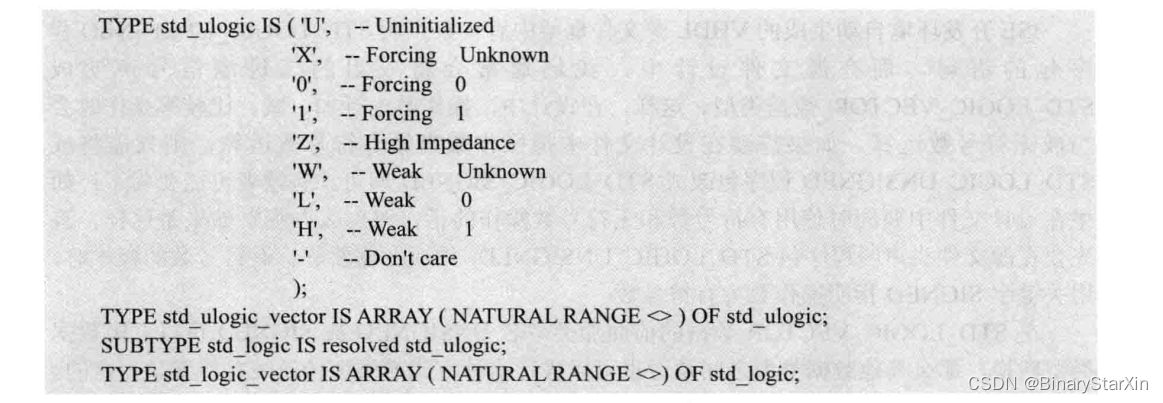

3.STD LOGIC 1164 定义的数据类型

前面说过,虽然 VHDL有多种基本的数据类型,用户也可以自定义各种类型的数据但在实际设计中一般是直接应用软件程序包中已定义好的数据类型。在ISE开发环境中,自动创建的 VHDL源文件头均会有以下几条库及程序包声明语句。

library IEEE:

uSe IEEE.STD LOGIC 1164.ALL;

use IEEE.STD LOGIC ARITH.ALL;

use IEEE.STD LOGIC UNSIGNED.ALL:

上面几条程序包声明语句中的程序包源文件可在ISE安装目录“/vhdl/src/ieee”路径下找到。STDLOGIC ARITH和STDLOGIC UNSIGNED程序包的内容在后面讨论。我们在设计中用得最广泛的数据类型是在STDLOGIC1164程序包中定义的数据类型STD LOGIC 及其数组形式STDLOGIC VECTOR。现在来看看STDLOGIC 1164程序包中是如何来定义这两种数据类型的。

读者可能会感到奇怪,STDLOGIC数据类型仅是STDULOGIC的一个子类型,在定义该类型时有一个关键字 RESOLVED。RESOLVED是程序包中定义的一个函数,我们不必去过多关注 RESOLVED 的细节,只需知道 STD LOGIC类型的信号因为有RESOLVED函数的作用,可以由两个以上的信号来驱动。除此之外,STDLOGIC的定与STDULOGIC完全相同,STDLOGIC VECTOR是STDLOGIC的数组形式。从STDULOGIC 数据类型的定义来看,它是一种有9种值的枚举数据类型,每种值都代表着规定的含义,如X表示未知状态,U表示没有初始化,Z表示高阻状态。在这9种状态值中,我们只需记住1、0、Z这 3种状态分别代表数字电路中的1、0及高阻状态即可,其他状态值通常只在仿真建模时使用与 VHDL标准程序包中定义的二值数据 BIT相比,STD LOGIC的值明显丰富了许多事实上STDLOGIC所定义的值可以完全表示数字电路中的信号逻辑。同时,加上IEEE库中提供的适合 STDLOGIC数据类型的各种运算、操作符功能及函数支持,在VHDL设计中几平仅声明STDLOGIC及STD LOGIC VECTOR这两种数据类型即可以完成全部设计。更形象一点来讲,在进行VHDL设计时,可以将每BIT的STDLOGIC类型数据当成一条实际的信号线来理解,而数字逻辑电路设计不过是各种数字信号之间的运算、控制等操作。

774

774

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?