本文转载自IamSarah博友的原创文章!

最近在看《硬件架构的艺术》这本书,本篇博文也是来自书中的内容。随着工艺的进步,低功耗设计显得越来越重要了。作为一个数字前端设计师,我们就来看看如何在RTL级别减低功耗。实质上在大规模ASIC设计中,当RTL级设计完成的时候,整个系统至少80%的功耗就已经确定。后端流程没有办法修复微架构,而微架构和RTL代码风格对于动态和静态功耗有极大的影响。下面就说说在RTL级别可以从哪几个方面降低功耗。

- 状态机的编码和解码

在各种状态机的编码中,格雷码是最适合低功耗设计的。因为它在状态转换过程中每次只有一个触发器变化,因此格雷码编码的状态机也消除了依赖于状态组合等式中存在毛刺的风险。图中是二进制编码和格雷码编码的比较。

- 二进制数表示方法

在大多数的应用中都是用补码表示有符号数的,但是原码与补码切换过程中,很多位都发生变化,与之相比,有符号数的变化较少,如图所示0,1的补码和有符号数表示。选用哪种表示方法,还是应该看具体的应用场合。

- 门控时钟

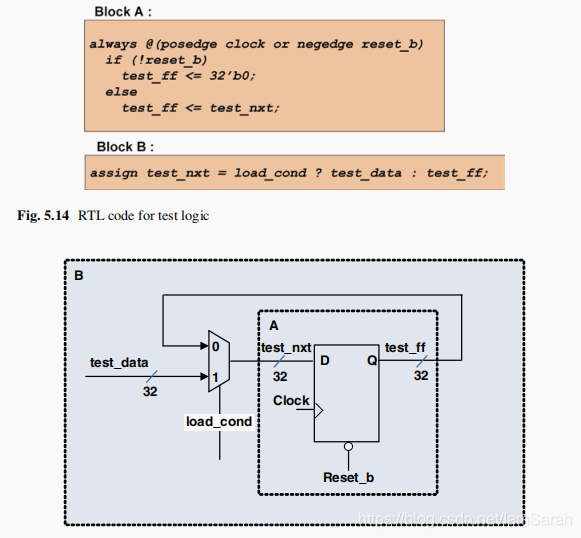

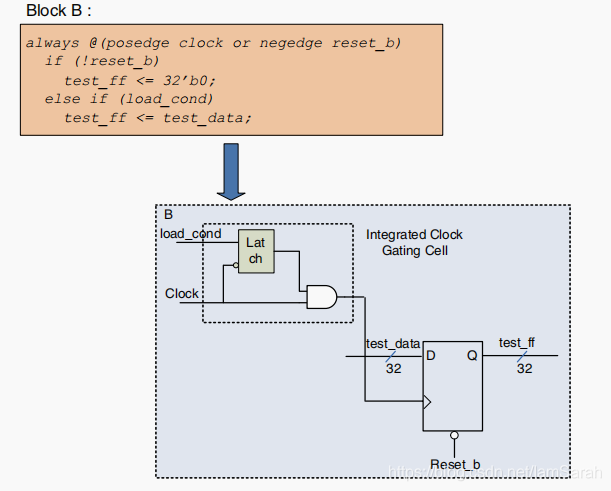

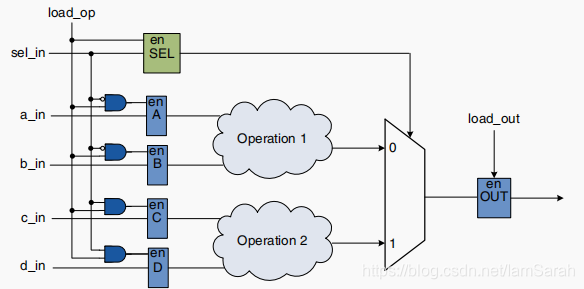

之前的博文中也有详细的介绍过门控时钟,这里主要从编码角度来对门控时钟进行说明。编码过程中应当考虑一下后端工具是否可以在环境设置的加入门控时钟。这里主要是举例说明,先看如下的RTL代码以及逻辑实现:

这种写法,综合的结果是32个mux2,但如果换成如下的描述方式,某些后端工具就有可能会识别出来load_cond为32个寄存器共享,则通过一个门控时钟来替换32个mux2,如下:

这种门控信号和数据通路重组的方法在降低功耗中都应该考虑。

- 独热码多路器

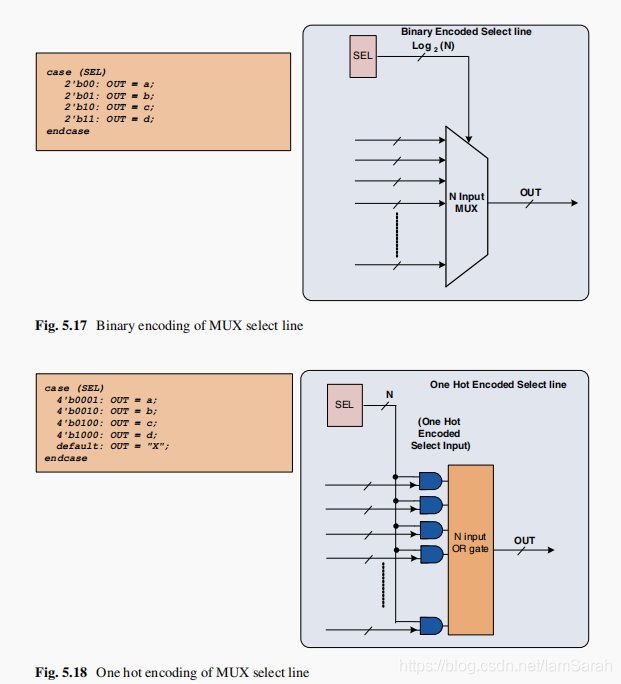

对于多路器的实现可以通过case语句,if语句和状态机都可以实现,常用的多路器是使用二进制编码,mux的输入如果是多位总线的话,就会产生明显的开关过成,因此会产生功耗。

但如果对case条件进行独热编码的话,其输出就会更快更稳定,且在初期就能够将未选中的总线掩藏掉,实现低功耗效果。一般数字电路设计中都存在mux,因此避免或者掩藏掉伪转换的发生器可以有效地降低功耗。

这两种编码及实现方式如下图所示:

- 除掉多余的转换

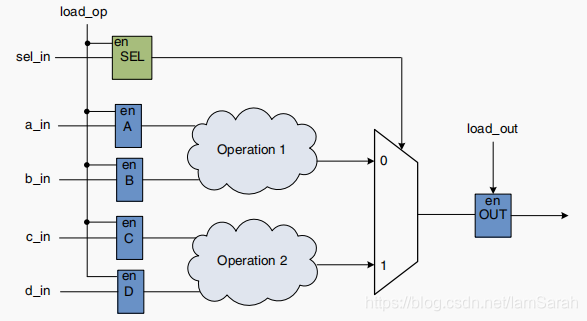

在没有设置默认状态的情况下,总线数据常常会发生没有意义的转换。如果转换之后的数据没有被采样,那么它就是多余的,将

这样的转换去掉可以显著降低功耗。如下所示:

该设计会读入所有的输入信号,但是最终的输出只会用一个,因此通过一个与门去掉多余的转换,这样就可以节省一部分功耗,如下所示。

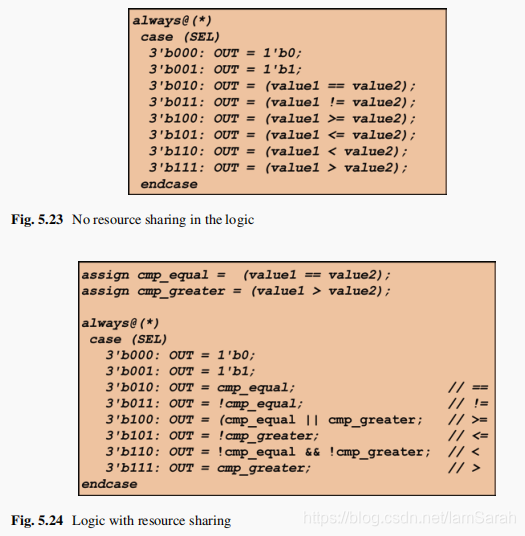

- 资源共享

设计较多算术云端的设计中,避免相应的运算逻辑在多个位置重复出现,使用重复逻辑会增大面积增大功耗,如下图所示:

- 使用行波计数器来降低功耗

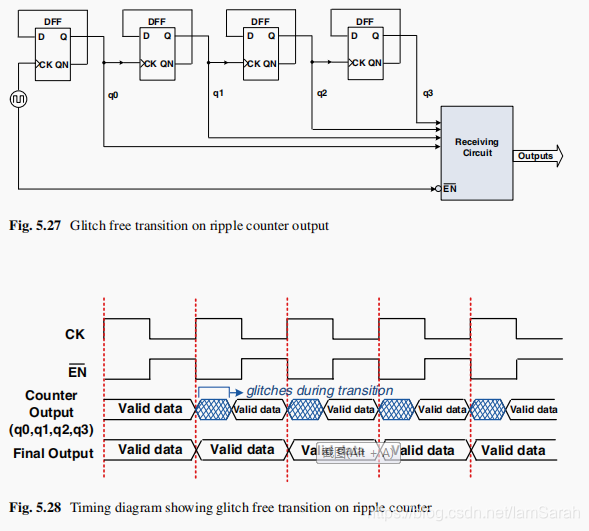

行波计数器可以用来降低功耗,但是因为因为每个寄存器都有传播延迟,因此高的有效位相比低的有效位会更晚发生变化。在时钟行进的过程过,计数器可能会因为毛刺产生不正确的值,在最高有效位变化的时候,会产生最坏的影响。例如四位的计数器,当从0111变为1000的时候会短暂的出现0111,0110,0100,0000,1000。行波计数器对于STA是一个巨大的挑战,因为行波计数器中每个阶段都产生了一个新的时钟域,这就需要STA工具处理更多的时钟域,从而消耗更多的时间。

对于行波计数器使用低有效使能信号,可以使其不再产生毛刺。计数器的电路数正沿触发,当计数器的信号切换稳定的时候在时钟的低电平期间再进行读数,这样就能保证读到的数据是稳定的。但这里时钟的高电平持续的时间至少要与计数器的最大行波周期同样长,这样才能避免行波过程还在进行中,而时钟信号已经开启接收电路。这种改进方法如下图所示:

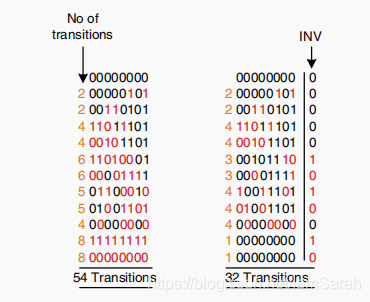

- 总线翻转

在当前数据和下一个数据之间的汉明距离(汉明距离指的是两个数中不相同位的数量)大于N/2的时,将下一个数据取反后再传输,以减少总线上出现转换的位数量,即总线反转编码。这种技术对于减少大容量总线上的转换次数很有效。这样在传输数据的时候,需要添加一个额外的控制位,用来表示传输的数据是否已经反转。如下是经过总线反转后的例子,转换总量从54变成32.

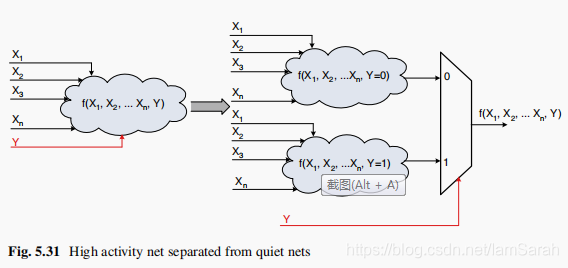

- 高活跃度网络

将活跃度较高的网络和活跃度较低的网络区分开来,然后将其置于逻辑云中较深的位置。如图x1...xn的变化频率较低,Y是高活跃度网络,因此将逻辑云分成两部分,一个是Y=0,一个是Y=1,通常两份新的逻辑云的规模会有所减小。

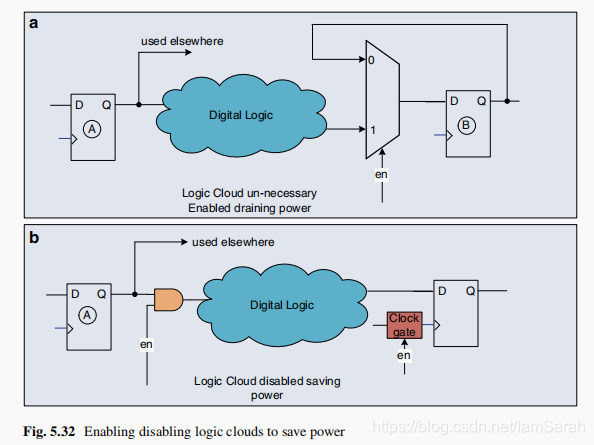

- 启用和禁用逻辑云

在操作大规模逻辑云计算的时候,往往在需要的时候才将其打开,下图中触发器B有使能信号但是触发器A并没有关闭,因为设计中其他地方用到输出,所以是的整个逻辑云启用浪费了能量。一种改进方法是将使能信号移到逻辑云前面,在不需要逻辑云的时候禁用他它,如下所示:

2779

2779

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?