DMA:direct memory assess 直接内存访问,不在cpu干预的模式下完成数据的交互,节省cpu资源

DMACR:DMA控制寄存器

DMASR:DMA状态寄存器

在Xilinx的产品中有硬核DMA和软核DMA之分,如ZYNQ系列的板卡中包含PS模块即arm,是存在硬核DMA的,硬核DMA的传输速度不如PL端FPGA上的IP核即软核DMA

DMA IP使用详见PG021手册

DMA两种基础模式

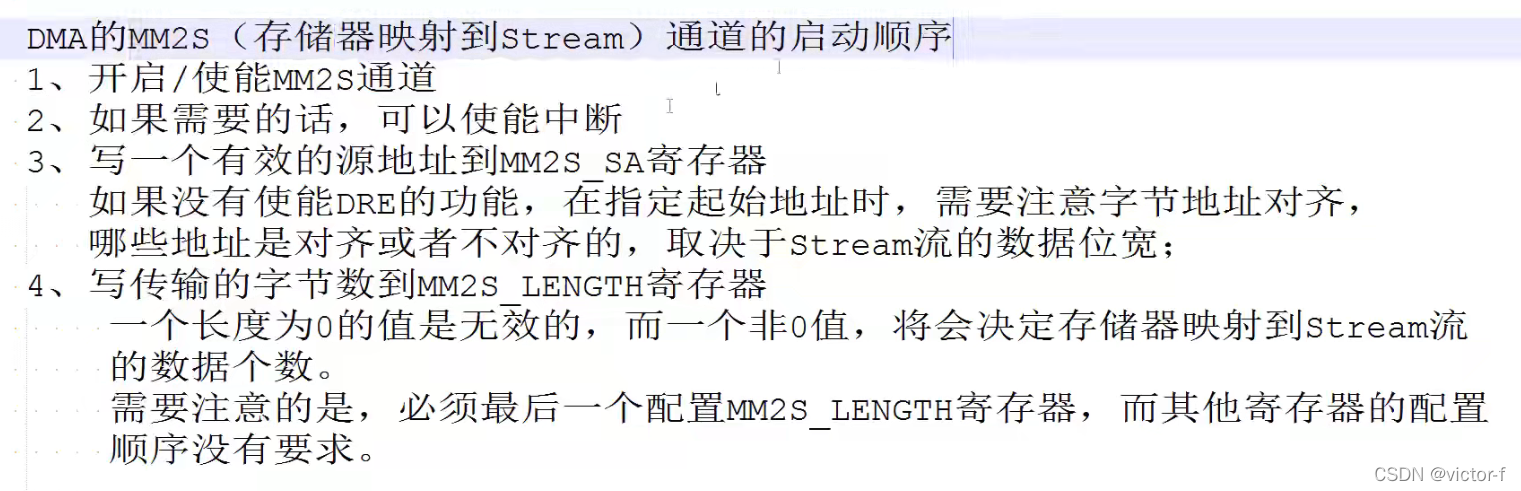

1、SG disable,简单模式,由cpu配置相应寄存器即可完成传输,

优点:操作简单,消耗FPGA资源较少

缺点:确定了起始地址后,数据只能连续的读写,若想在新的区域读写则需要重新配置,开始新的传输

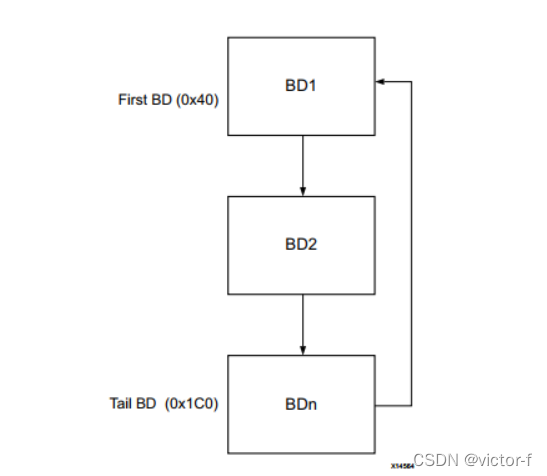

2、SG enable ,将传输的基本参数(起始地址、传输长度等)存储在内存中,这些参数被称为BD(Buffer Descriptor),在工作时,通过SG接口加载和更新BD中的状态

优点:操作复杂

缺点:确定了起始地址后,数据只能连续的读写,若想在新的区域读写则需要重新配置

进阶模式——cyclic dma mode

SG模式的升级应用

2970

2970

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?