目录

设计一个1秒钟的计数器。

一、逻辑设计

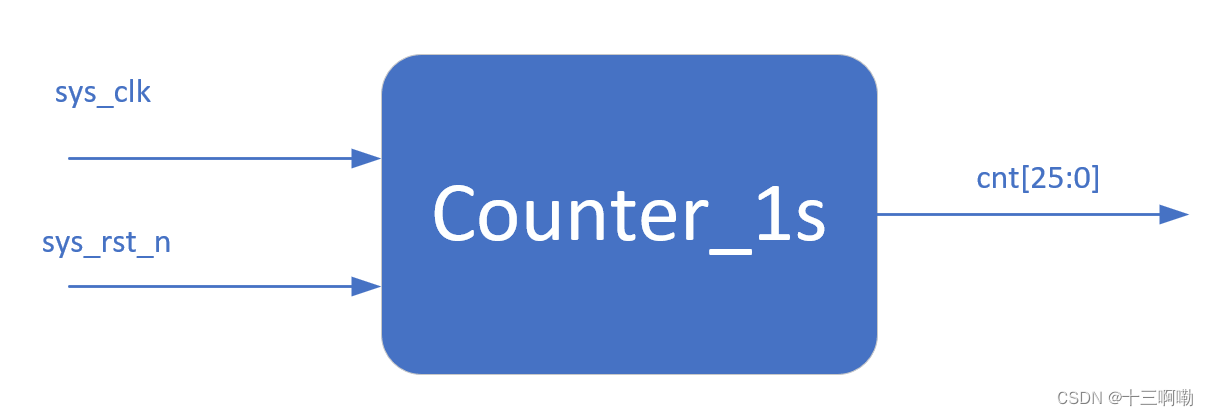

1.端口设计

模块的输入端口包含系统时钟sys_clk、复位信号sys_rst_n;输出端口包含26bit的计数器信号cnt[25:0]。

FPGA芯片型号选取XC7A35tfgg484-2,板载的晶振是50Mhz,我们计数的时钟就是50MHz,换算成时间为[1/(50*10^6)Hz]s=0.000_000_02s,即50MHz频率的时钟一个周期的时间为0.000_000_02s,1秒钟需要50_000_000个脉冲周期,所以我们的计数器需要在50MHz的时钟下计50_000_000次,50000000用二进制表示为0010 1111 1010 1111 0000 1000 0000,所以计数器信号cnt位数设置为26。

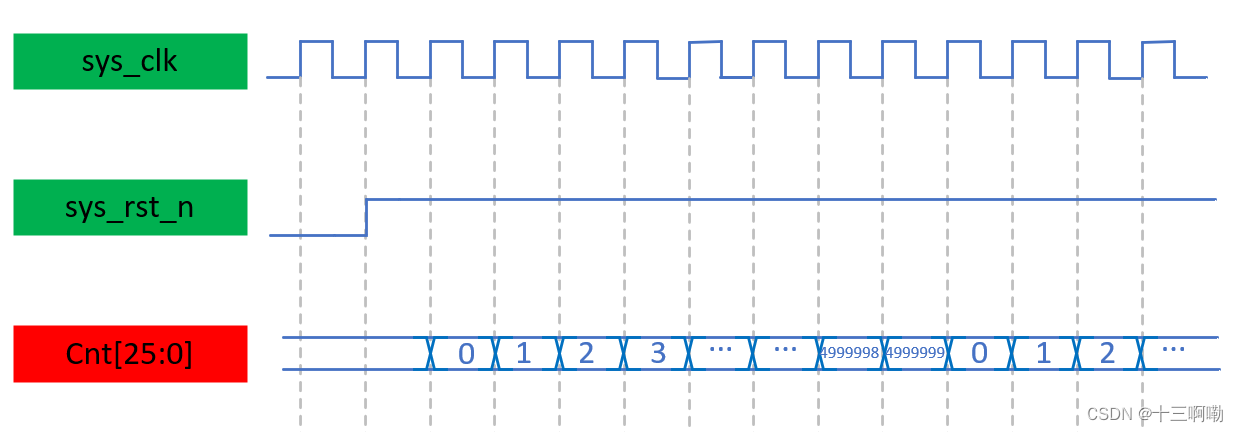

2.波形图绘制

每个时钟上升沿之后,在每个时钟周期递增计数,计数器的值加1,cnt循环从0计数到49_999_999,达到最大值时就会从零开始清零重新累加。

二、程序设计

根据波形图使用Verilog编写计数器(counter_1s.v)代码

1.计数器代码

代码如下:

//1s计数器

module counter_1s(

input sys_clk, // 系统时钟信号

input sys_rst_n, // 系统复位信号

output reg [25:0] cnt // 计数器输出,使用寄存器类型

);

localparam COUNT_MAX = 50000000; // 计数器最大值,50_000_000

always @(posedge sys_clk or negedge sys_rst_n) begin

if (~sys_rst_n) begin

cnt <= 26'd0; // 复位时计数器清零

end

else if (cnt == COUNT_MAX - 1) begin

cnt <= 26'd0; // 计数到达最大值时复位

end

else begin

cnt <= cnt + 26'd1; // 每个时钟周期计数加1

end

end

endmodule

2.仿真代码

代码如下:

`timescale 1ns / 1ns

module tb_counter_1s();

// 定义输入端口

reg sys_clk; // 系统时钟信号

reg sys_rst_n; // 系统复位信号(低电平有效)

// 定义输出端口

wire [25:0] cnt; // 计数器值输出端口

// 初始化模块

initial begin

sys_clk = 1; // 初始时钟信号为高电平

sys_rst_n = 1'b0; // 初始复位信号为低电平

#201 // 延迟201个时间单位

sys_rst_n = 1'b1; // 将复位信号置为高电平,使计数器开始计数

end

// 时钟信号反转模拟

always #10 sys_clk = ~sys_clk;

// 实例化计数器模块

counter_1s counter_1s_inst(

.sys_clk(sys_clk), // 传递时钟信号

.sys_rst_n(sys_rst_n), // 传递复位信号

.cnt(cnt) // 传递计数器输出

);

endmodule

3.仿真结果

仿真波形与我们绘制的波形图一致

490

490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?