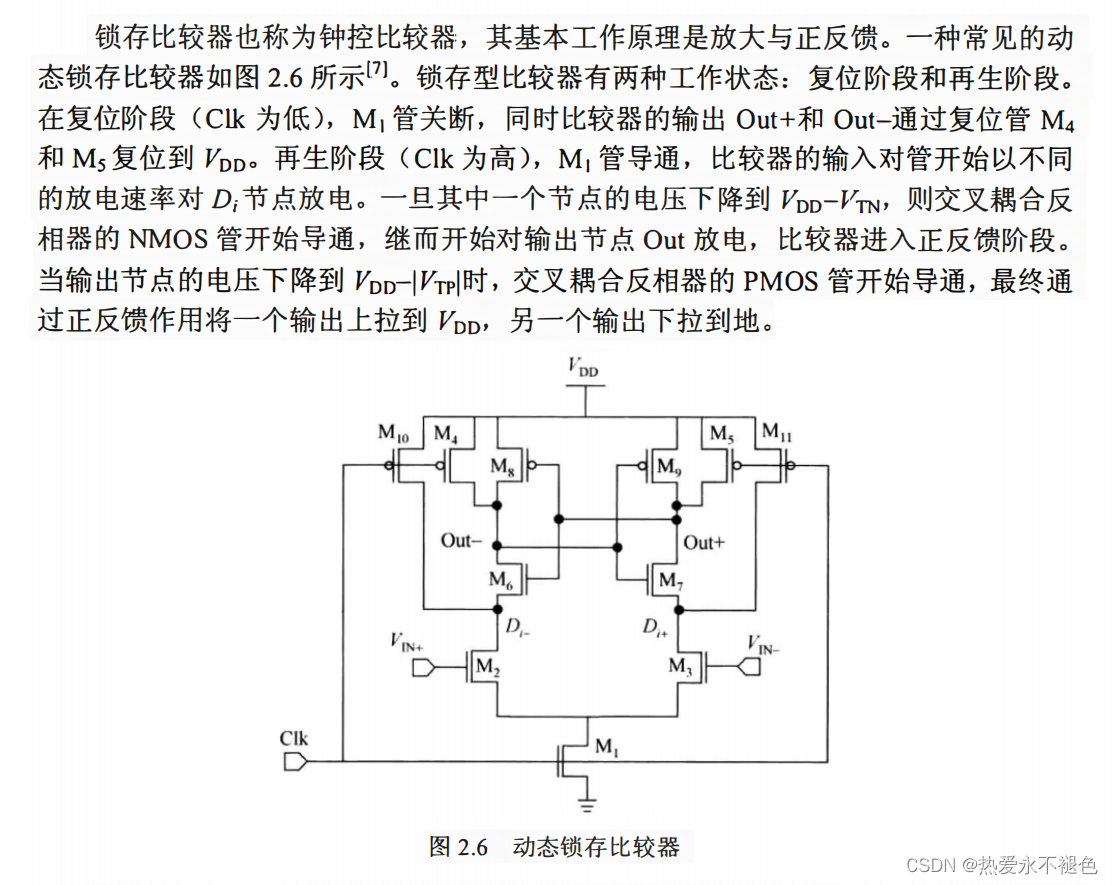

在做180nm工艺下SAR-ADC过程中对书上比较器内容的正反馈过程不是很清晰,于是用仿真来进行理解,个人理解,欢迎批评指正。

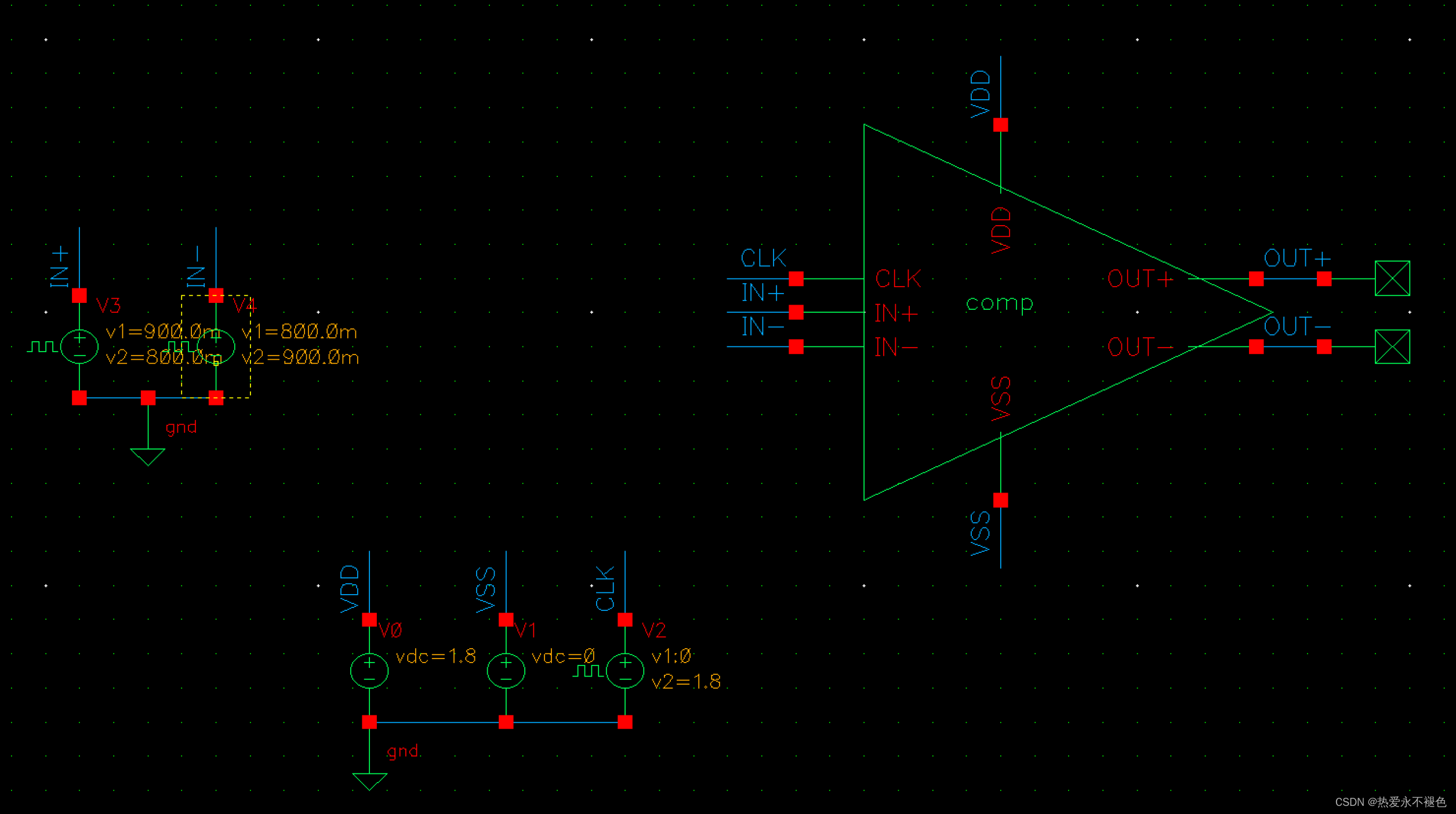

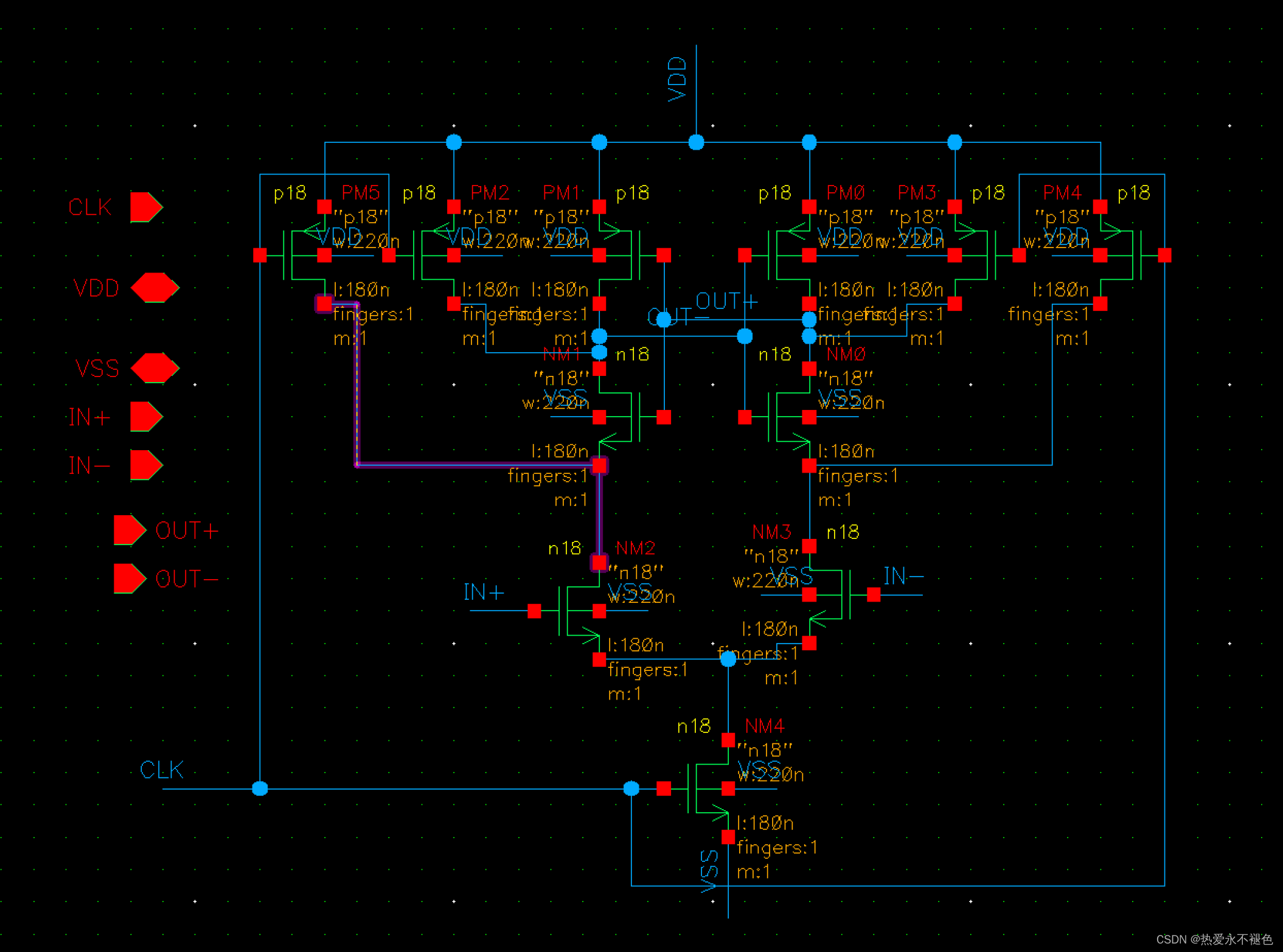

原理图如下:

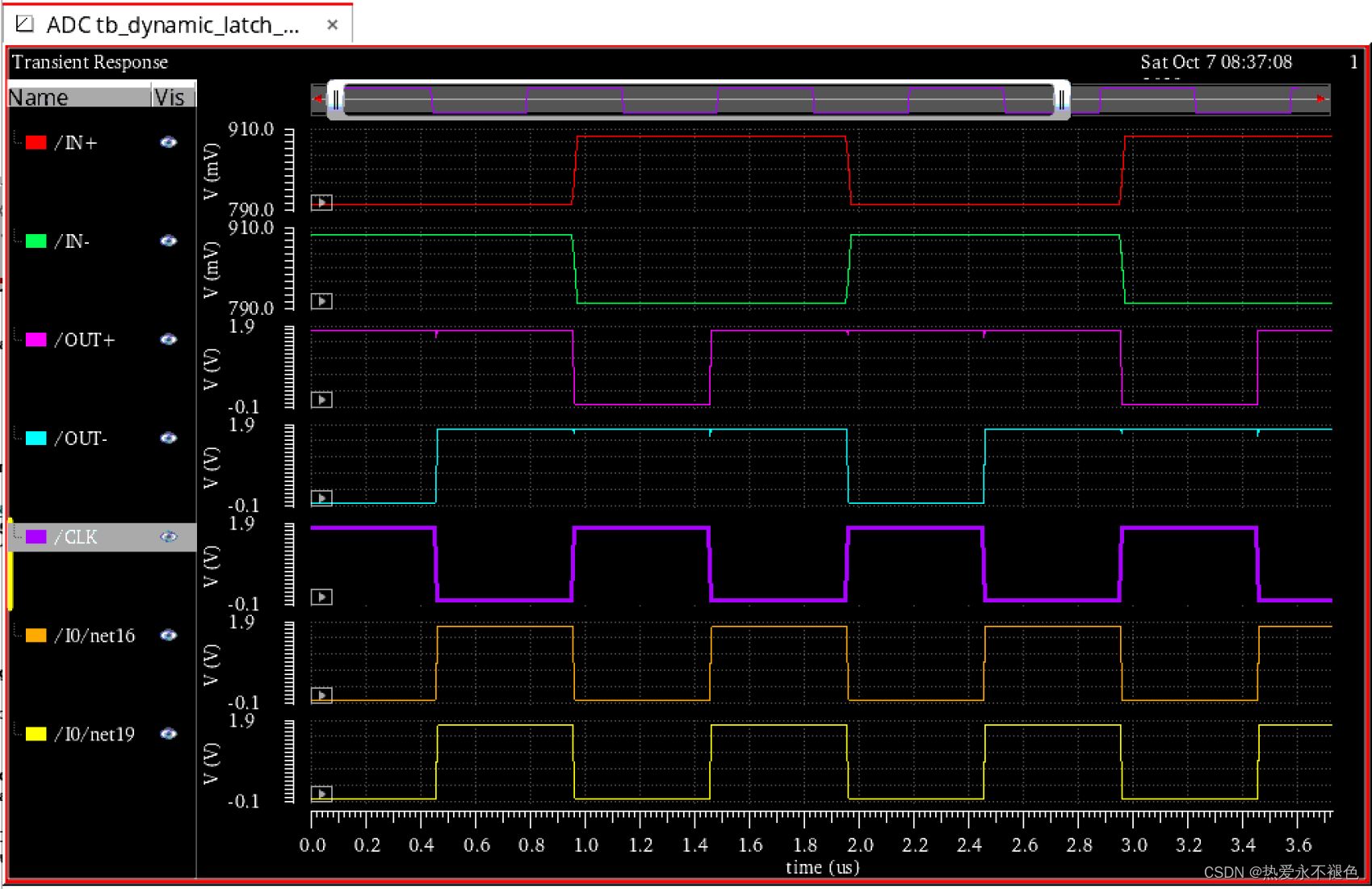

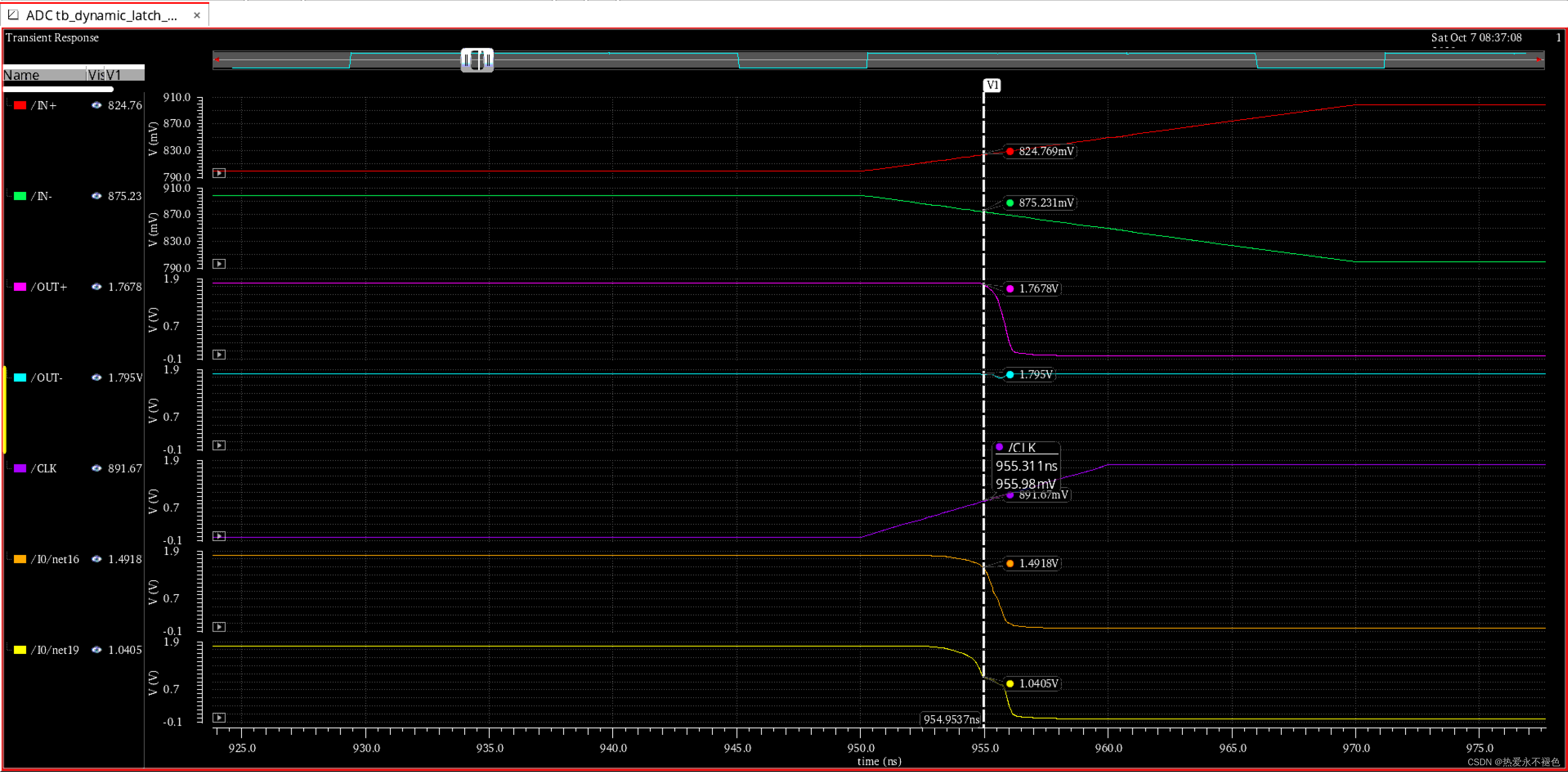

瞬态仿真如下结果:

下图可以明显看出来

1.在clk低电平时候M1关断,M4M5M11M10均导通为VDD高电平1.8V(net16对应D-,net19对应D+);

2.在clk高电平时候OUT+和OUT-总是一个高电平一个低电平;

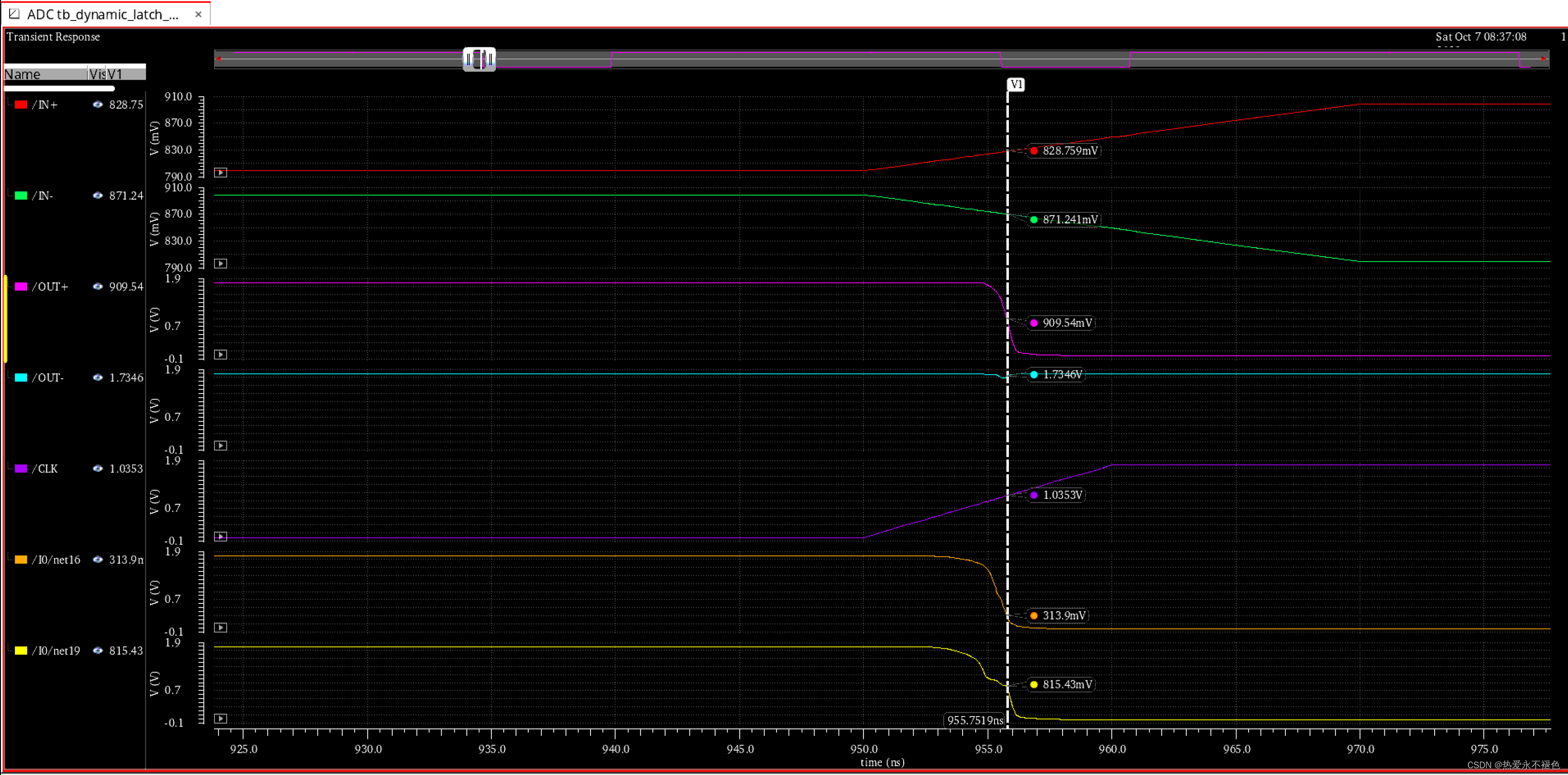

那到底是如何交叉耦合正反馈的,接下来选择放大细节来说明:对比下面两个图

1、可以看到OUT-有一个向下的小包(先减小后增大);

2、由于VN-大于VN+,所以放电速率不同而且D+电压下降更快,M7两端电压差先达到Vthn导通,之后分析交叉耦合反相器时候只看G端,可以发现OUT+正反馈下降很快,M8达到Vthn导通条件之后,M8的PMOS导通,之后OUT-不再下降而是上升恢复到VDD,作用到M7-M9组成的反相器,OUT+为VSS;

993

993

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?