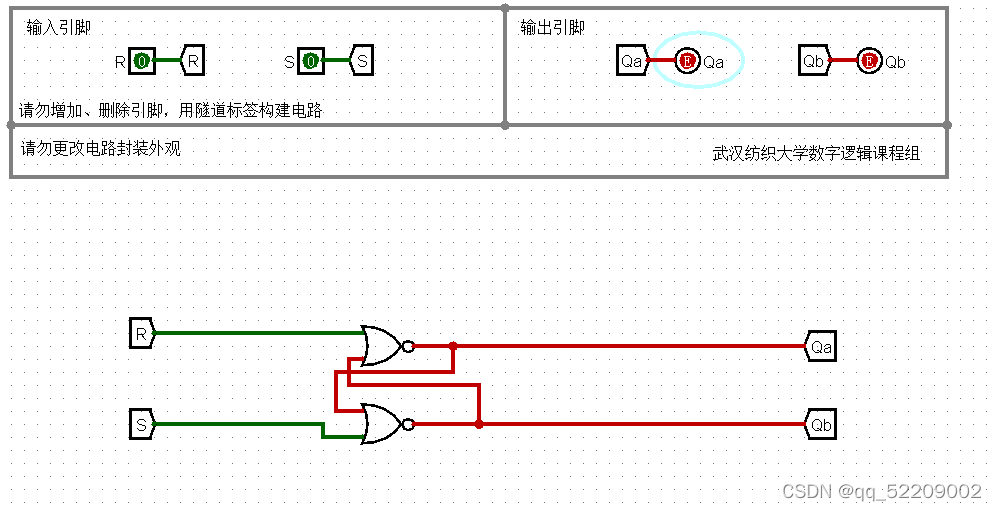

第1关:基本SR锁存器的设计

任务描述

本关任务:在Logisim中,构建由两个或非门构成的基本SR锁存器。

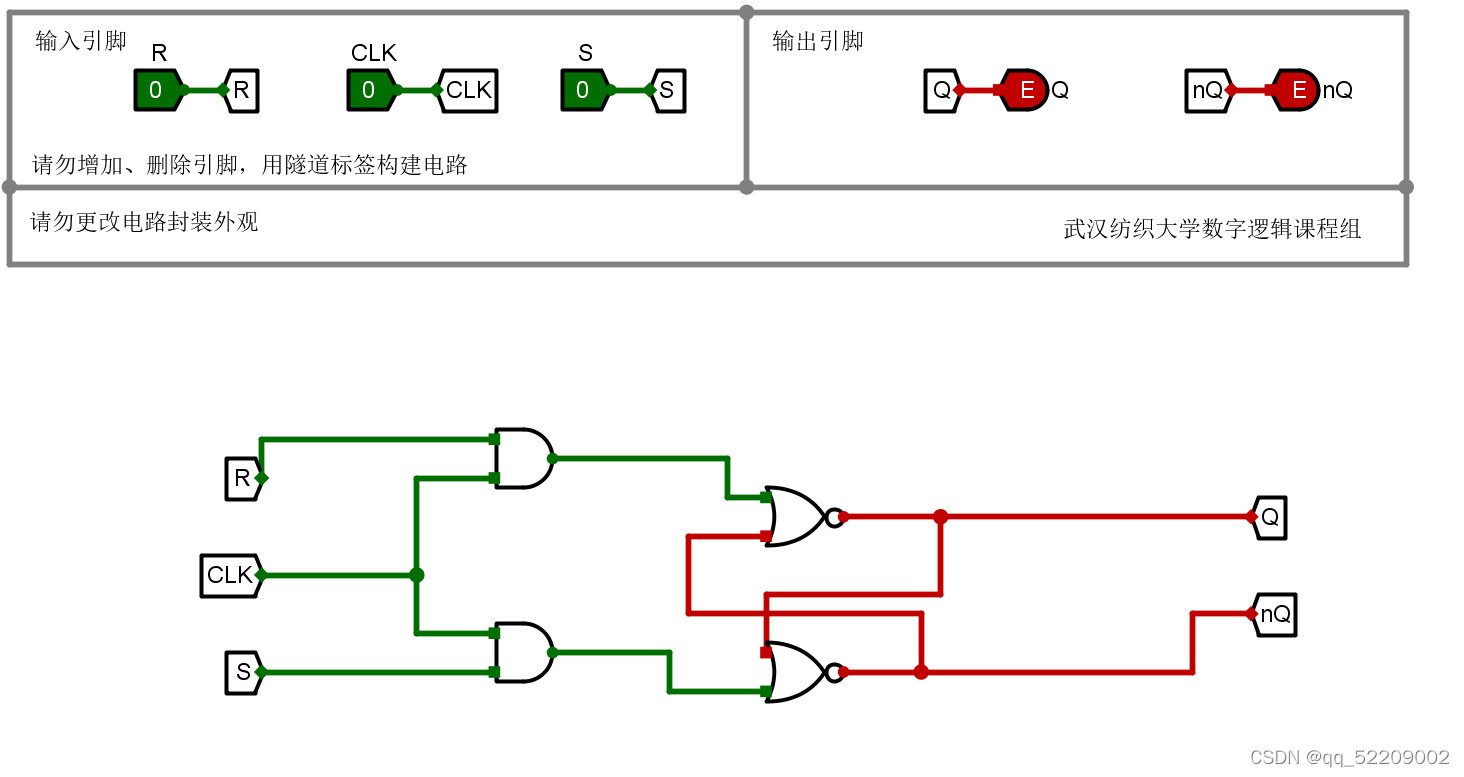

第2关:门控SR锁存器的设计

任务描述

本关任务:在Logisim中,在基本锁存器的基础上构建门控SR锁存器。

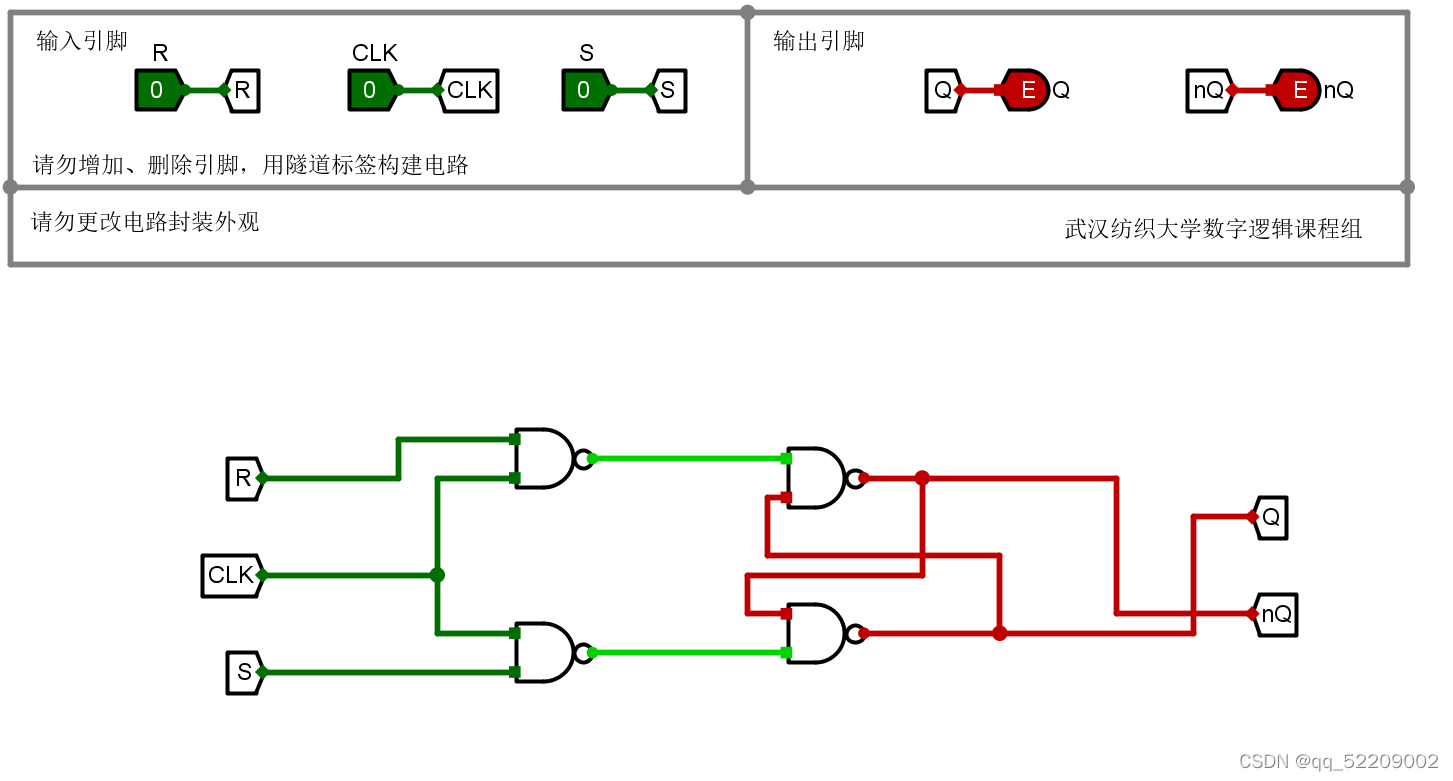

第3关:与非门构成的门控SR锁存器的设计

任务描述

本关任务:在Logisim中,用四个与非门构建门控SR锁存器。

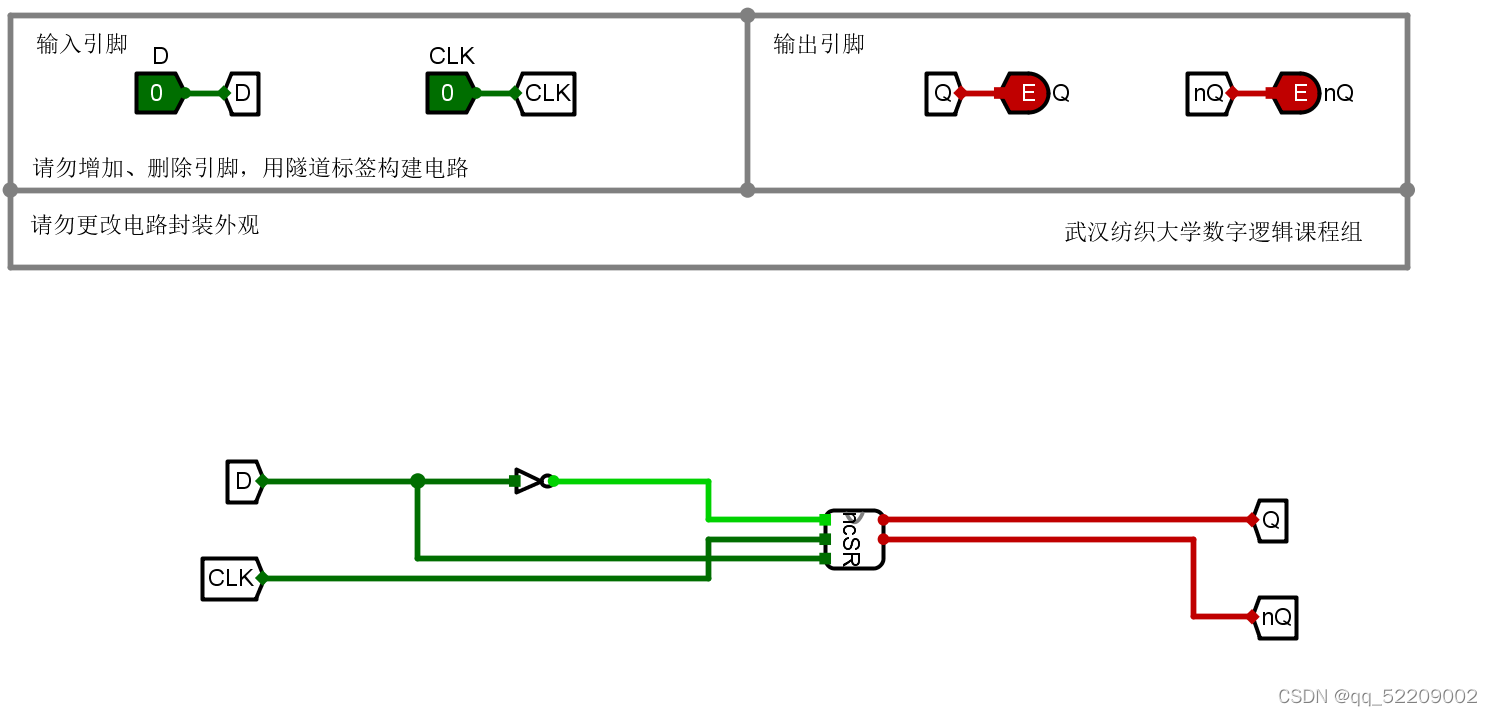

第4关:门控D锁存器的设计

任务描述

本关任务:在Logisim中,用四个与非门构建门控D锁存器。

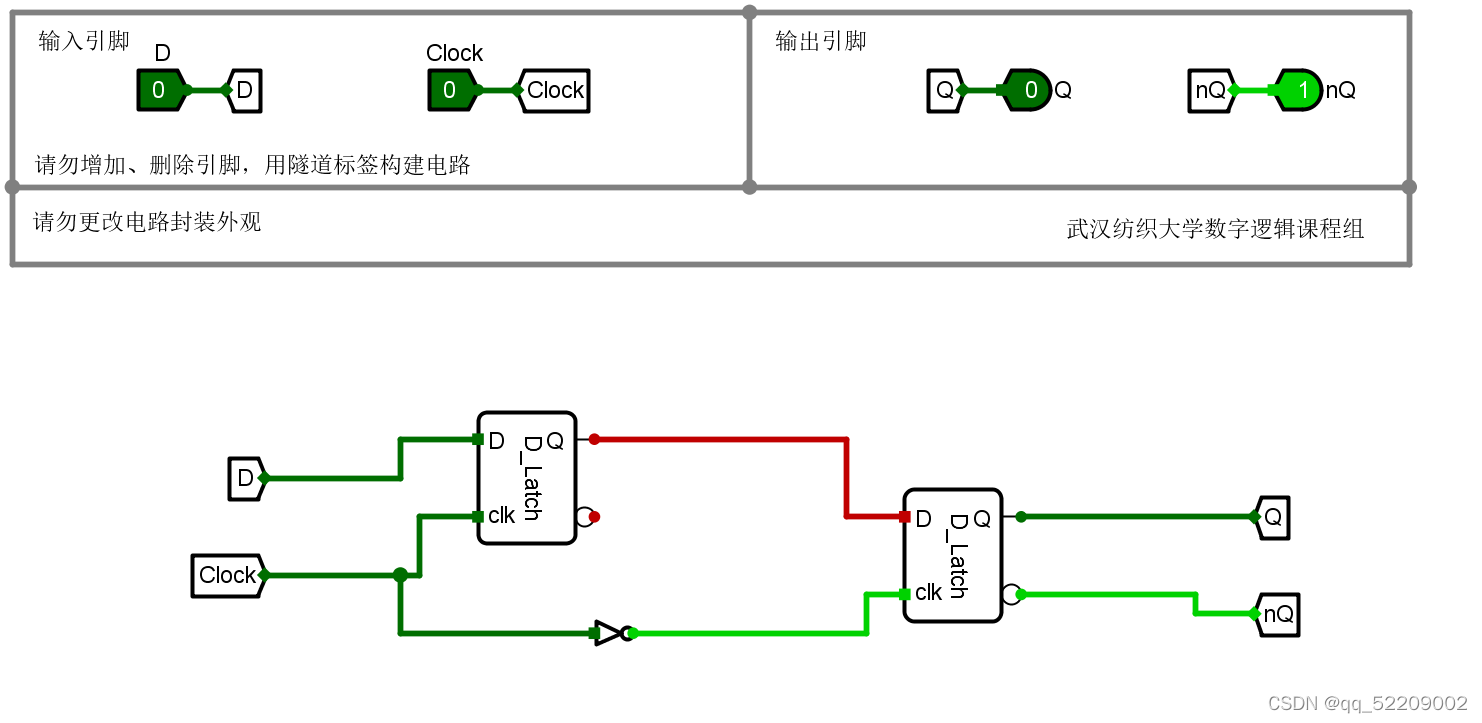

第5关:主从D触发器的设计

任务描述

本关任务:在Logisim中,用两个D锁存器级联构建主从式D触发器,要求下降沿触发。

第6关:T触发器的设计

任务描述

本关任务:在Logisim中,在D触发器的基础上构建T触发器,要求时钟上升沿触发

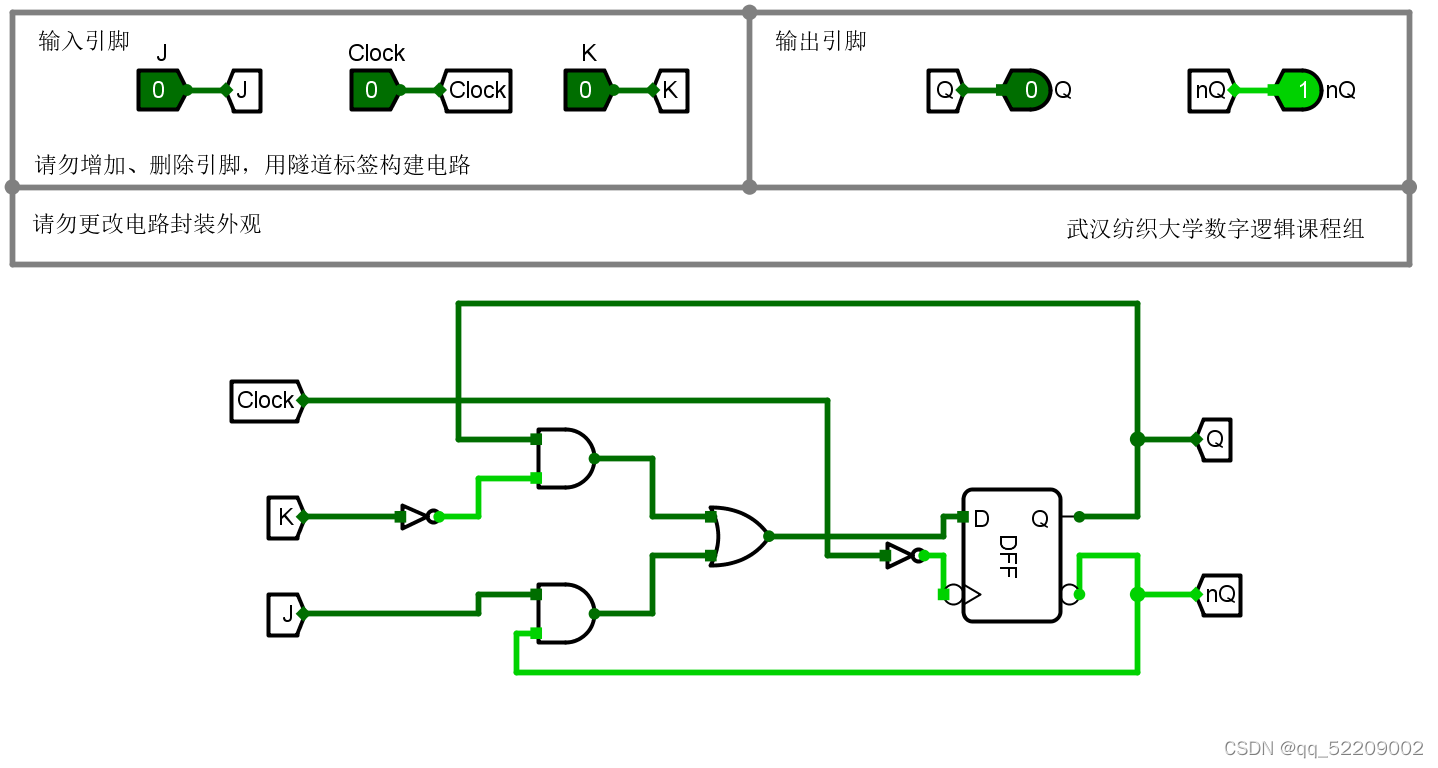

第7关:JK触发器的设计

任务描述

本关任务:在Logisim中,在D触发器的基础上构建JK触发器,要求时钟上升沿触发。

在这一系列任务中,你将使用Logisim软件逐步构建数字逻辑电路,从基本的SR锁存器开始,然后构建门控SR锁存器,进一步用与非门实现门控SR和D锁存器。最后,你将通过级联D锁存器创建主从D触发器,并基于D触发器构建T和JK触发器,所有设计都要求在时钟边沿触发。

在这一系列任务中,你将使用Logisim软件逐步构建数字逻辑电路,从基本的SR锁存器开始,然后构建门控SR锁存器,进一步用与非门实现门控SR和D锁存器。最后,你将通过级联D锁存器创建主从D触发器,并基于D触发器构建T和JK触发器,所有设计都要求在时钟边沿触发。

1709

1709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?