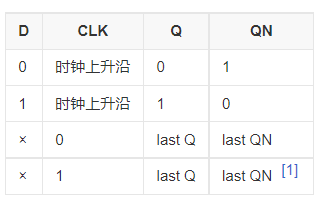

一、D触发器原理

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

- 功能表

- 方程

- 时序图

二、D触发器的设计

-

新建项目

-

点击next

- 选择芯片系列与类型

- next

- finish

- 添加文件

- 添加器件

- 4个nand2与非门,2个not非门,2个输入,2个输出

- 保存

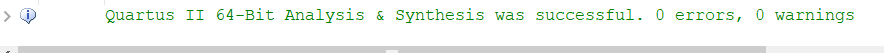

- 编译,显示没错误继续

- 查看模拟电路

如图

- 新建波形文件

- 添加信号

- 设置信号

- 运行查看仿真波形

三、调用D触发器并仿真

- 新建项目同上,直接跳到添加D触发器

- 添加信号输入输出

- 保存文件

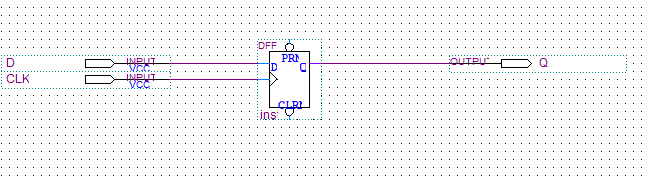

- 查看虚拟电路

- 查看仿真波形验证

四、用Verilog语言实现D触发器

- 新建工程同上,直接跳到添加Verilog文件

代码

module dtrigger(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//我们用正的时钟沿做它的敏感信号

begin

Q <= D;//上升沿有效的时候,把d捕获到q

end

endmodule

- 保存文件

- 查看电路

- 查看仿真波形

五、总结

三种方法作比较显然verilog语言编写比较简单,但是拖动器件更加直观可以看到D触发器的工作原理。

1140

1140

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?