Quratus简单入门

1、在 Quartus中自己用门电路设计一个D触发器,并进行仿真,时序波形验证

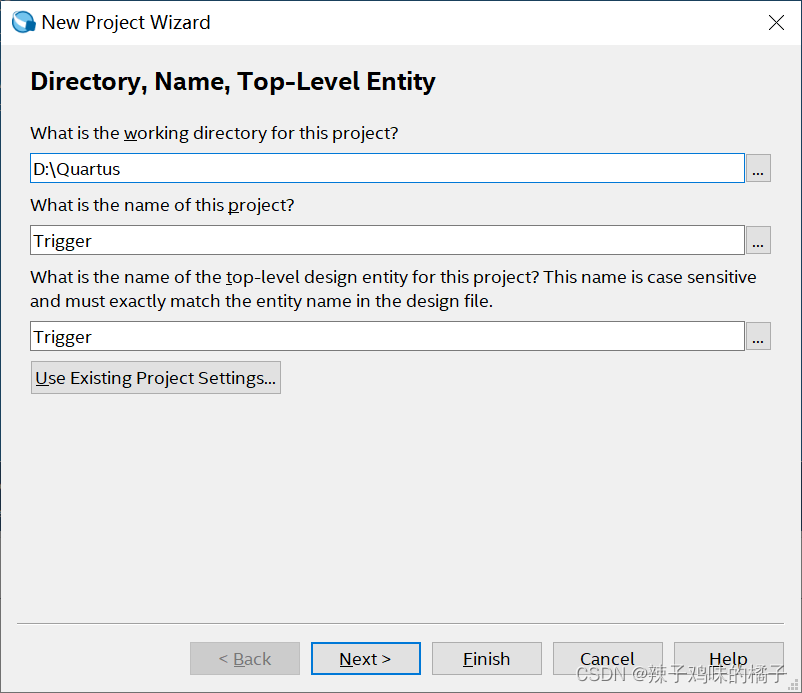

(1)创建项目

选择项目路径

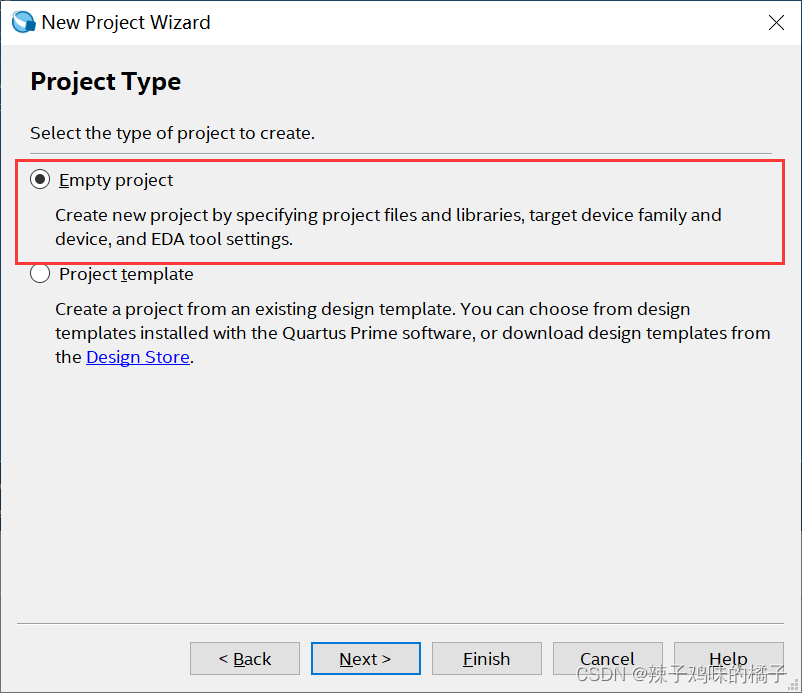

选择项目类型,这里选择空项目

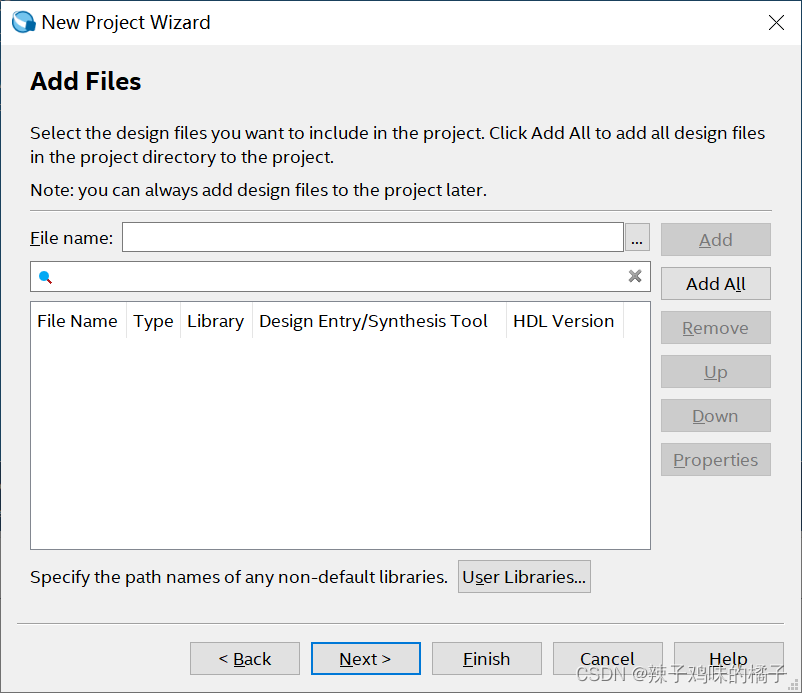

添加文件,这里跳过

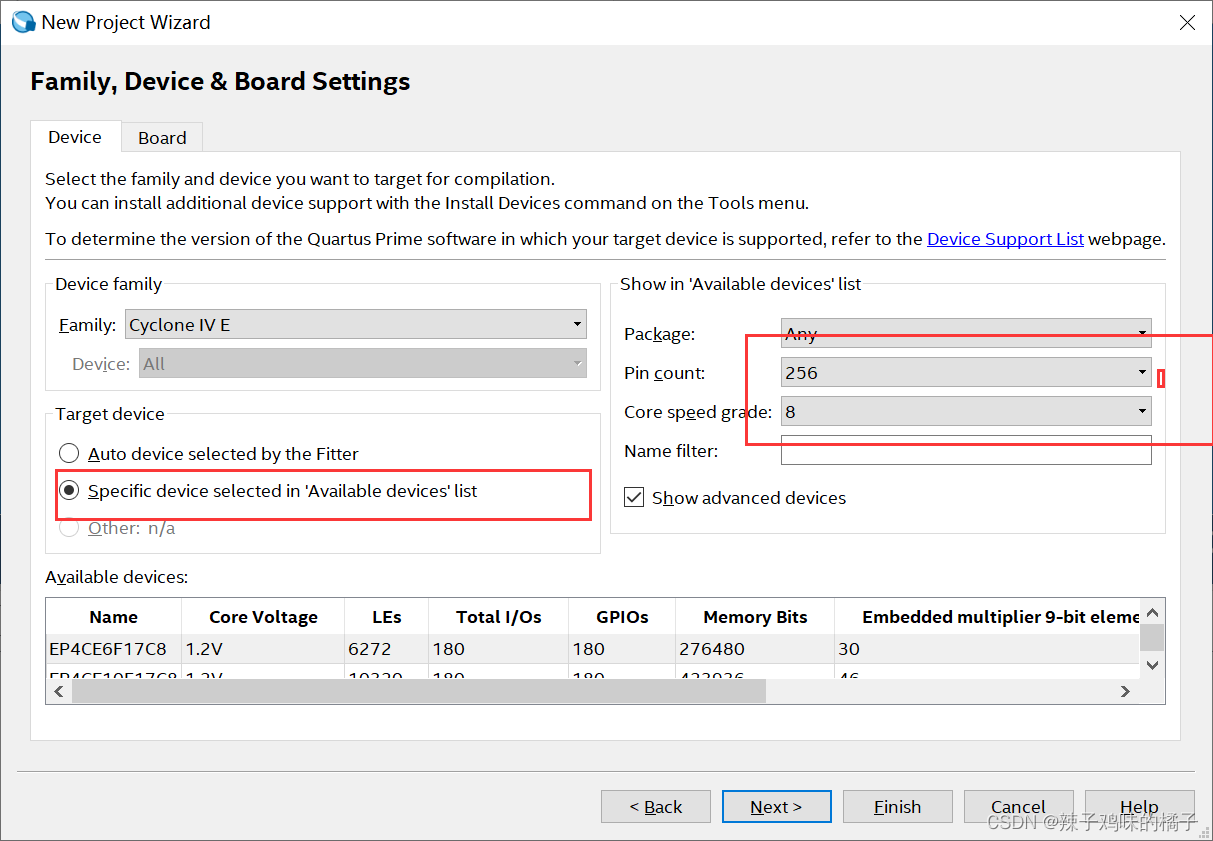

设置项目

点击finish完成项目

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Rq7DyIiT-1668397575354)(C:\Users\HP\AppData\Local\Temp\1668397544960.png)]](https://i-blog.csdnimg.cn/blog_migrate/8e14e45a542124675535b18d370e4335.png)

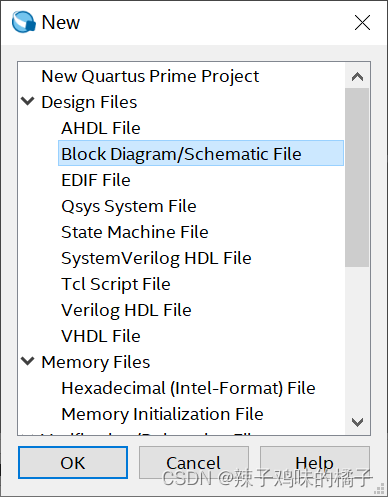

(2)创建波形文件

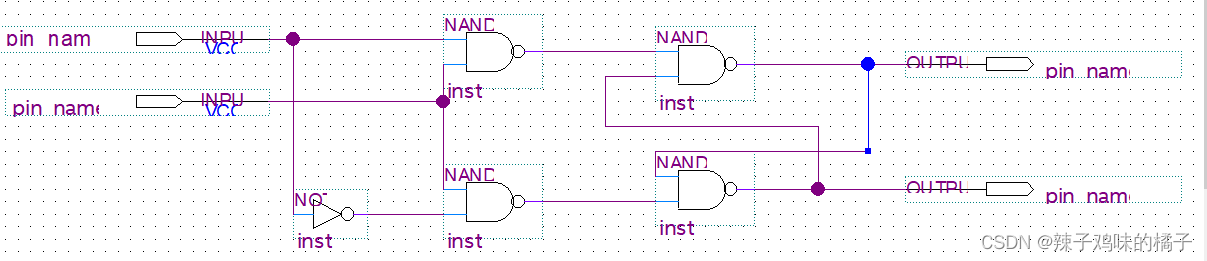

通过工具栏的工具创建出如下电路

创建之后进行保存

启动分析与综合,编译原理图文件·如果有编译错误,修改原理图,直到没有错误。也要检查警告信息,看是否连线连接正确。

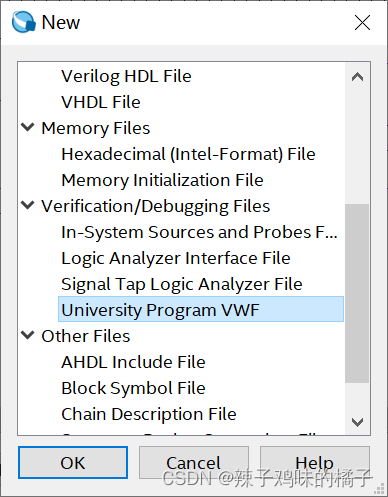

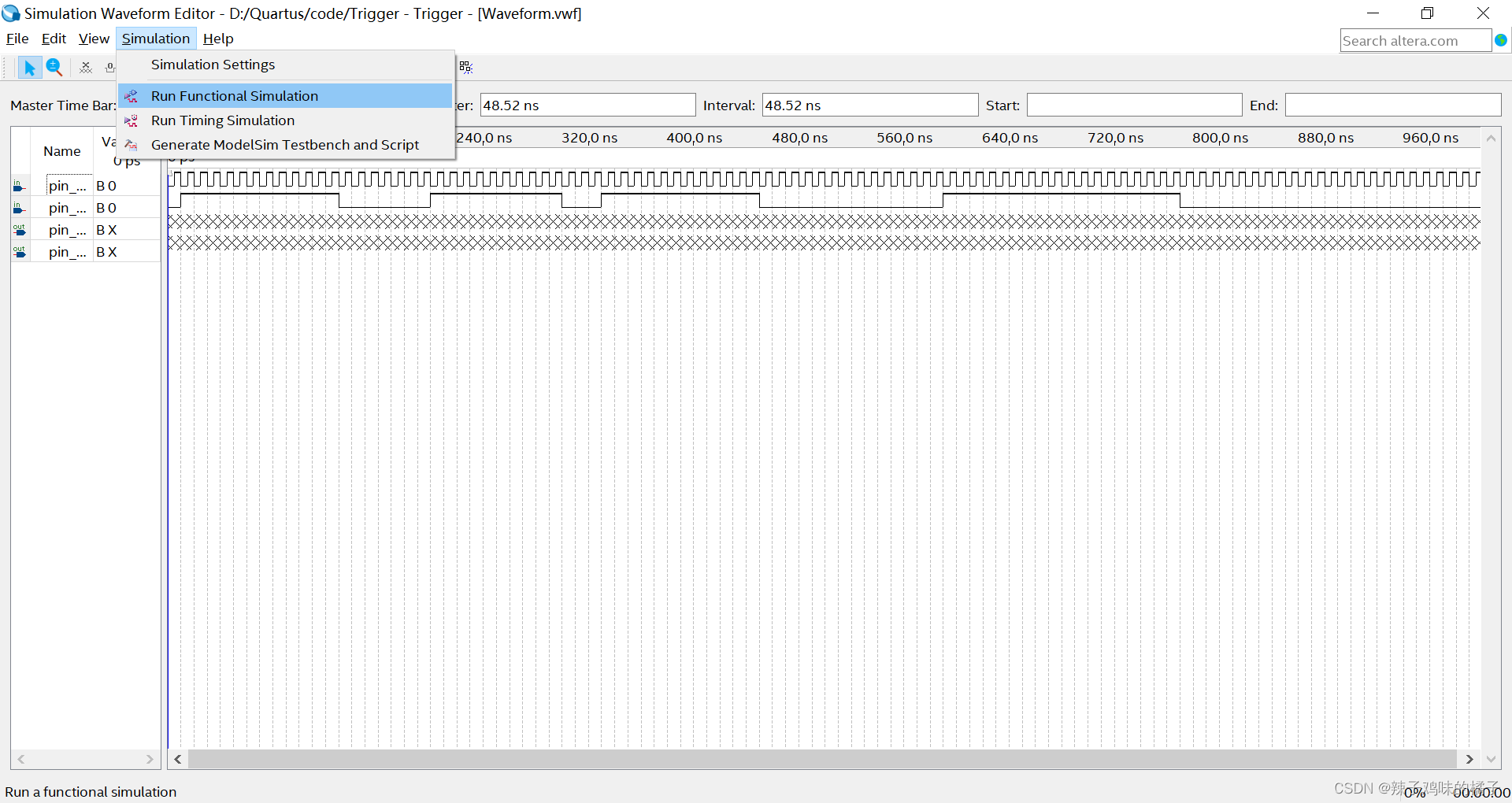

创建vwm格式波形文件,输入激励源

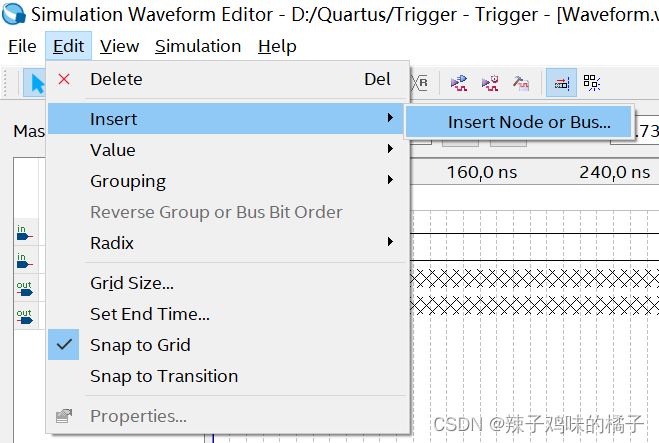

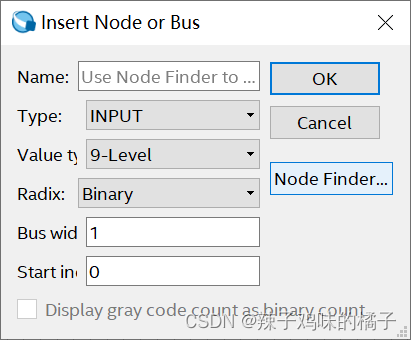

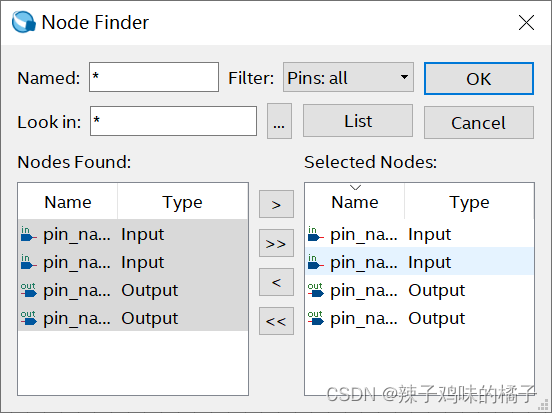

点击node finder

点击list后将所有输入导入

随后一直点击ok关闭页面即可

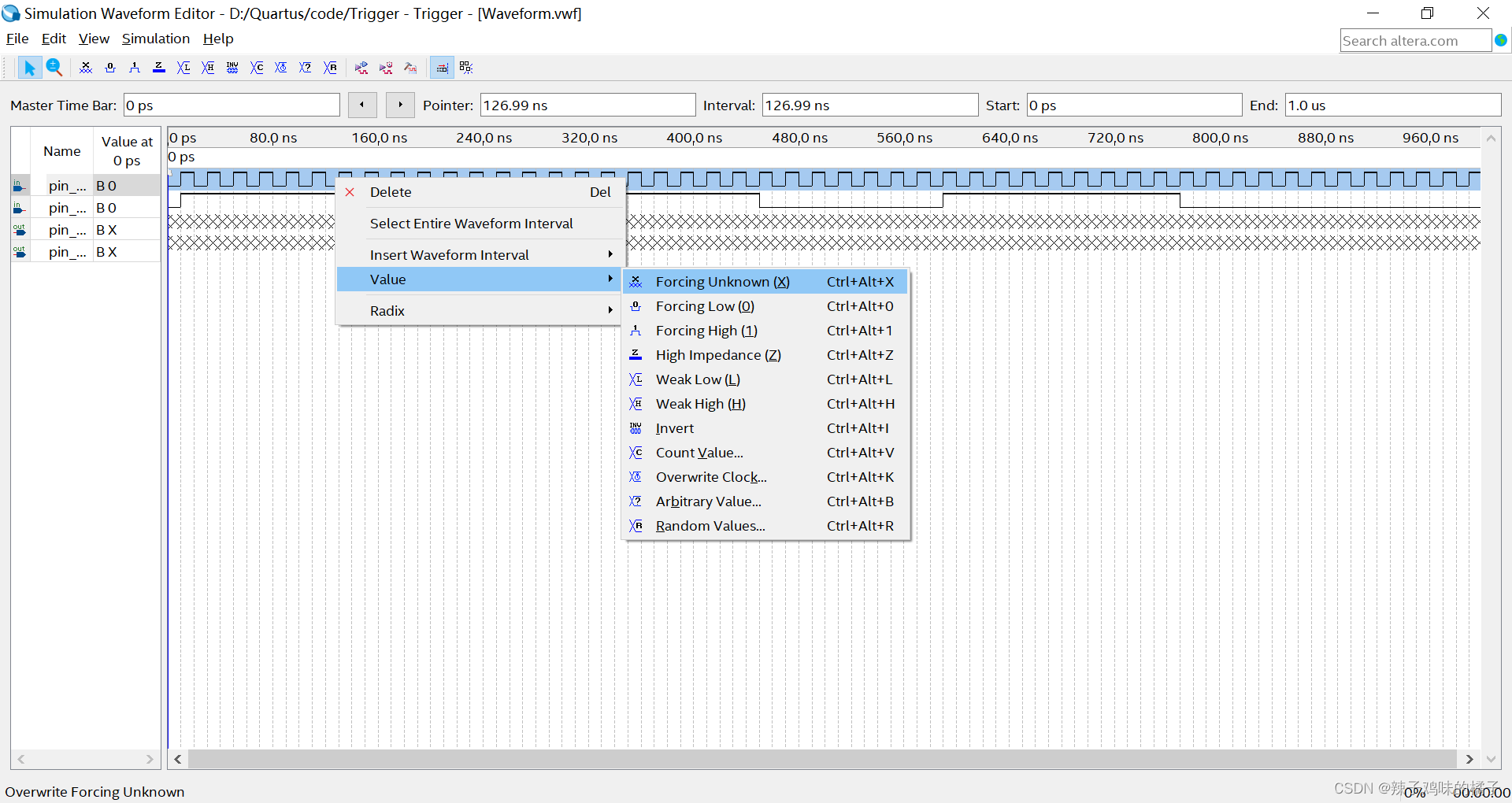

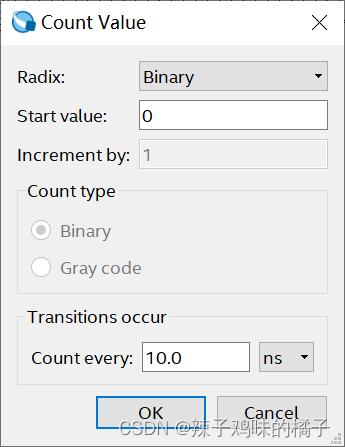

随后编辑信号进行仿真功能

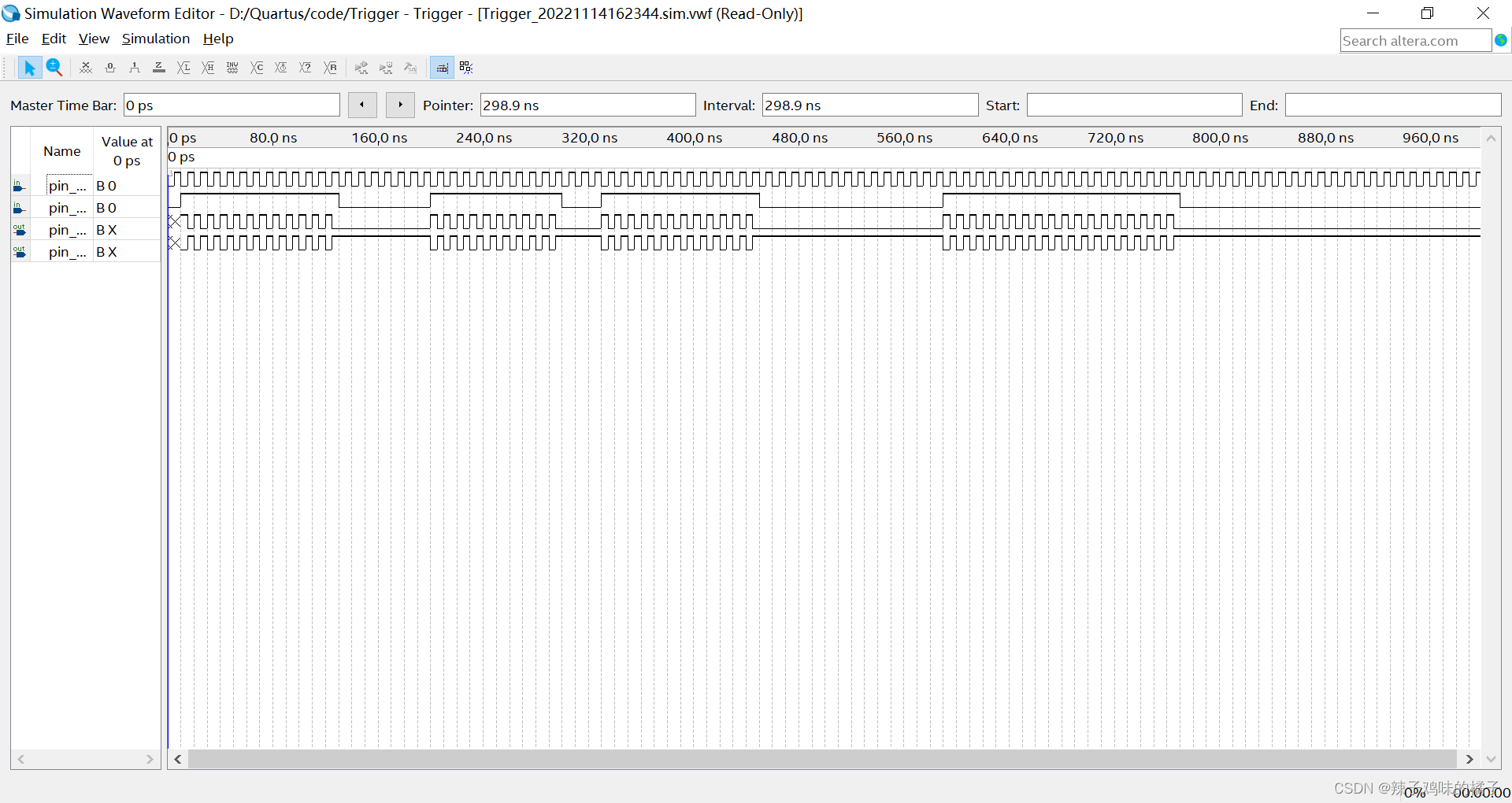

点击仿真,随后得出运行结果

2、在 Quartus 中直接调用一个D触发器电路,进行仿真,时序波形验证,与1做比较

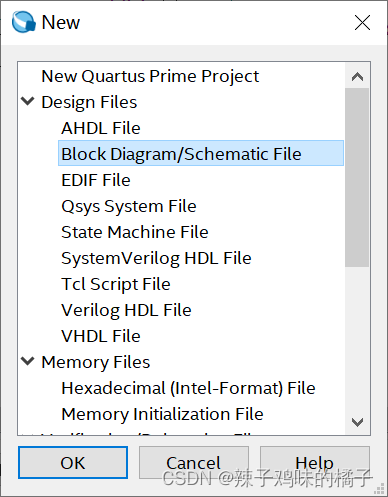

新建一个bdf文件具体操作与上面相同

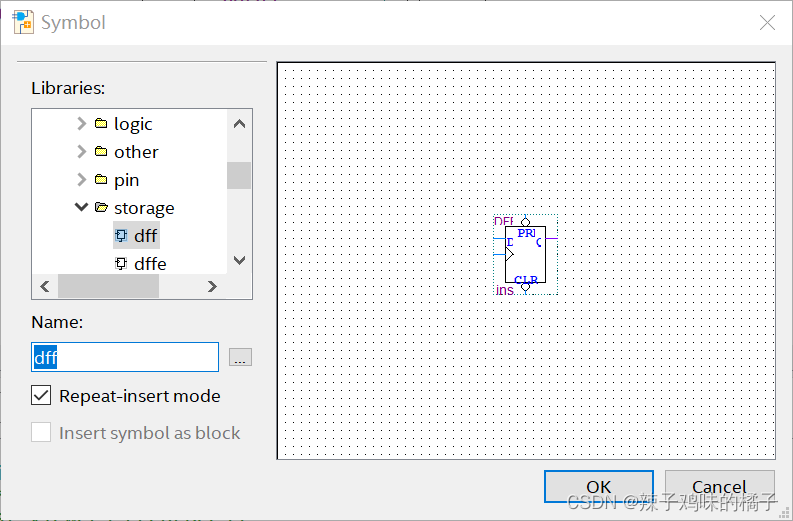

搜索dff找到触发器

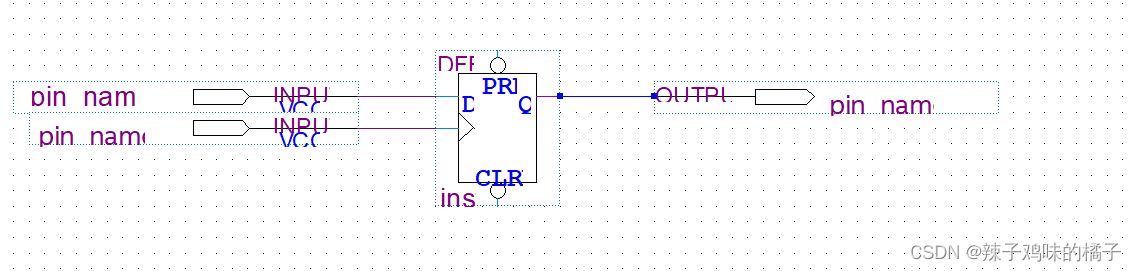

连接电路如下图

生成电路图

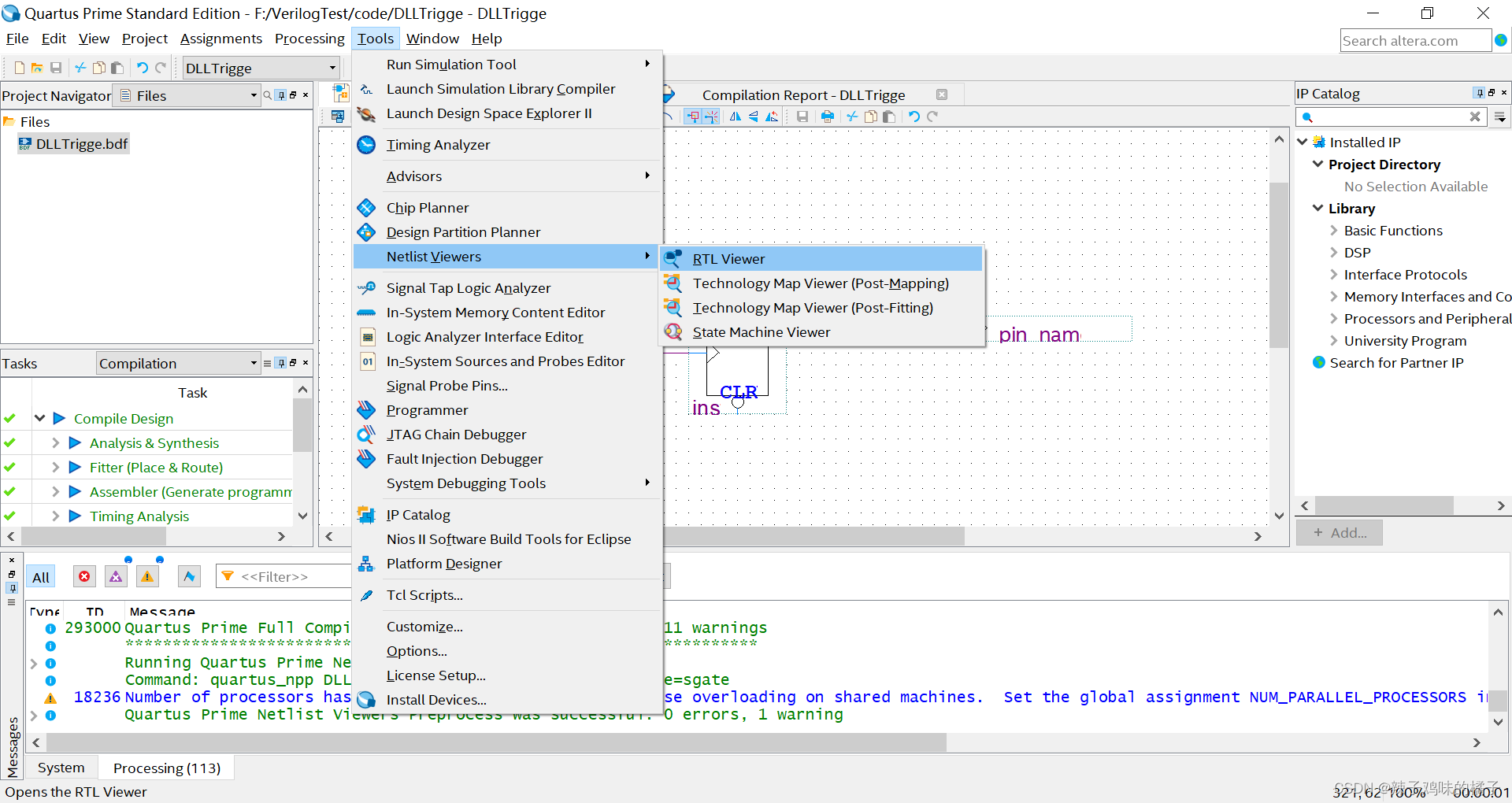

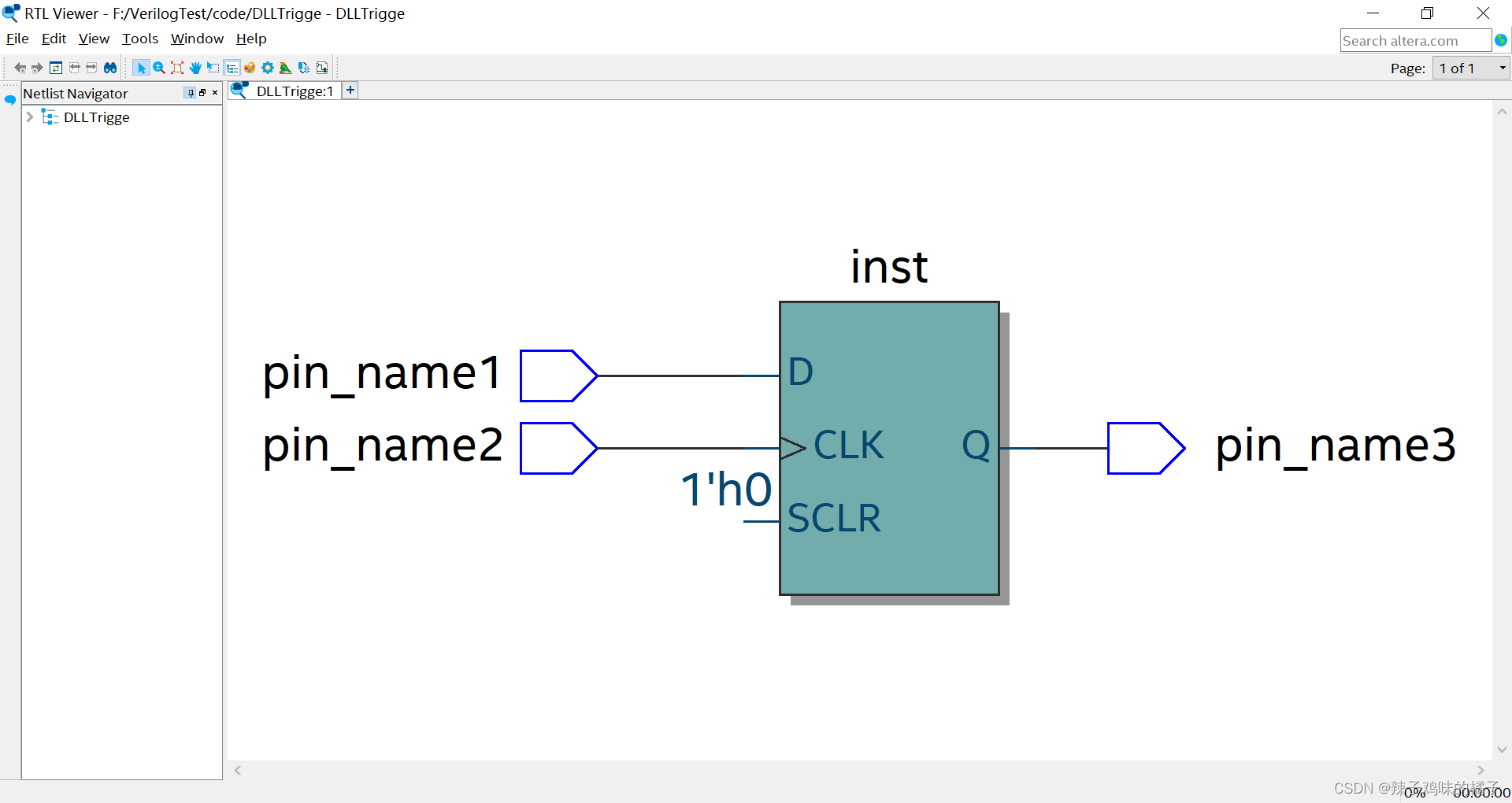

可以查看电路如下所示

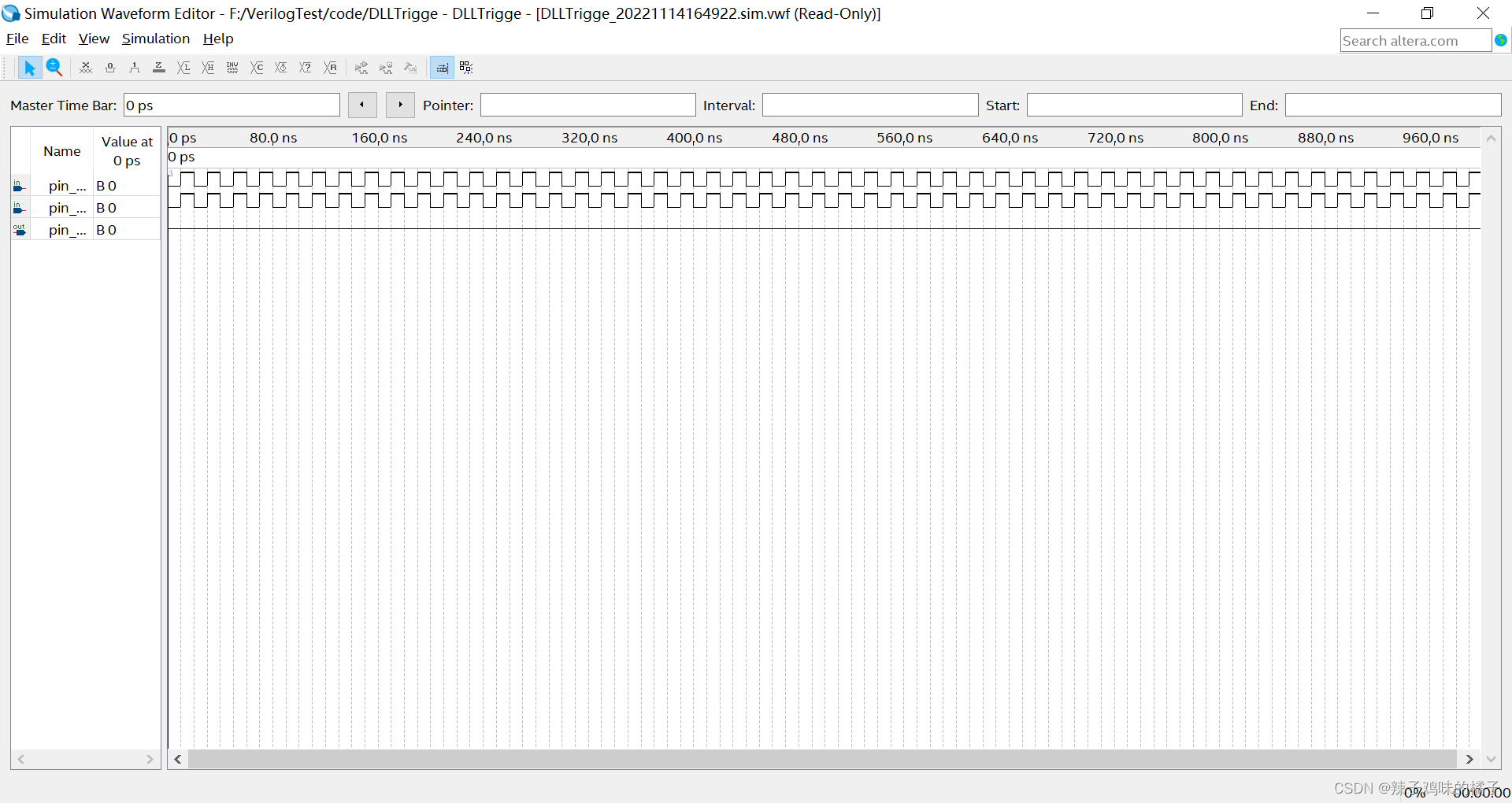

仿真运行d触发器得到结果

3、使用verilog语言书写一个d触发器

源码:

//测试代码

`timescale 1ns / 1ns

module dwave(D,CLK,Q);

input D;

input CLK;

output Q;

reg Q;

always @ (posedge CLK)//正的时钟沿做敏感信号

begin

Q<=D;//上升沿有效时,把D捕获到Q

end

endmodule

module dwave_tb;

reg CLK,D;

wire Q;

dwave u1(.D(D),.CLK(CLK),.Q(Q));

initial

begin

CLK = 1;

D <= 0;

forever

begin

#60 D <= 1;//人为生成毛刺

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;//维持16ns的低电平,然后让它做周期性的循环

end

end

always #20 CLK <= ~CLK;//半周期为20ns,全周期为40ns的一个信号

endmodule

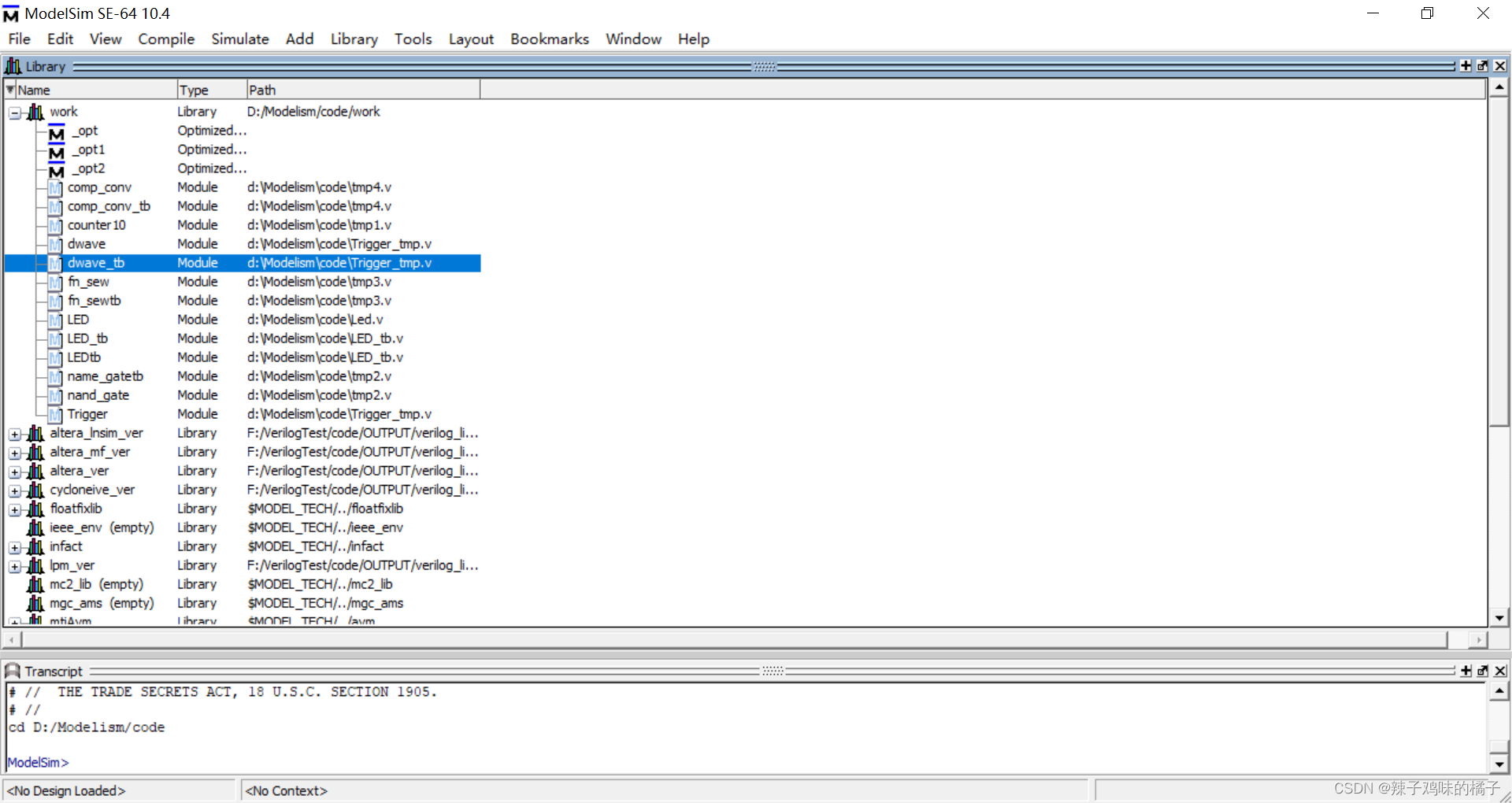

打开modelsim进行仿真

找到文件目录

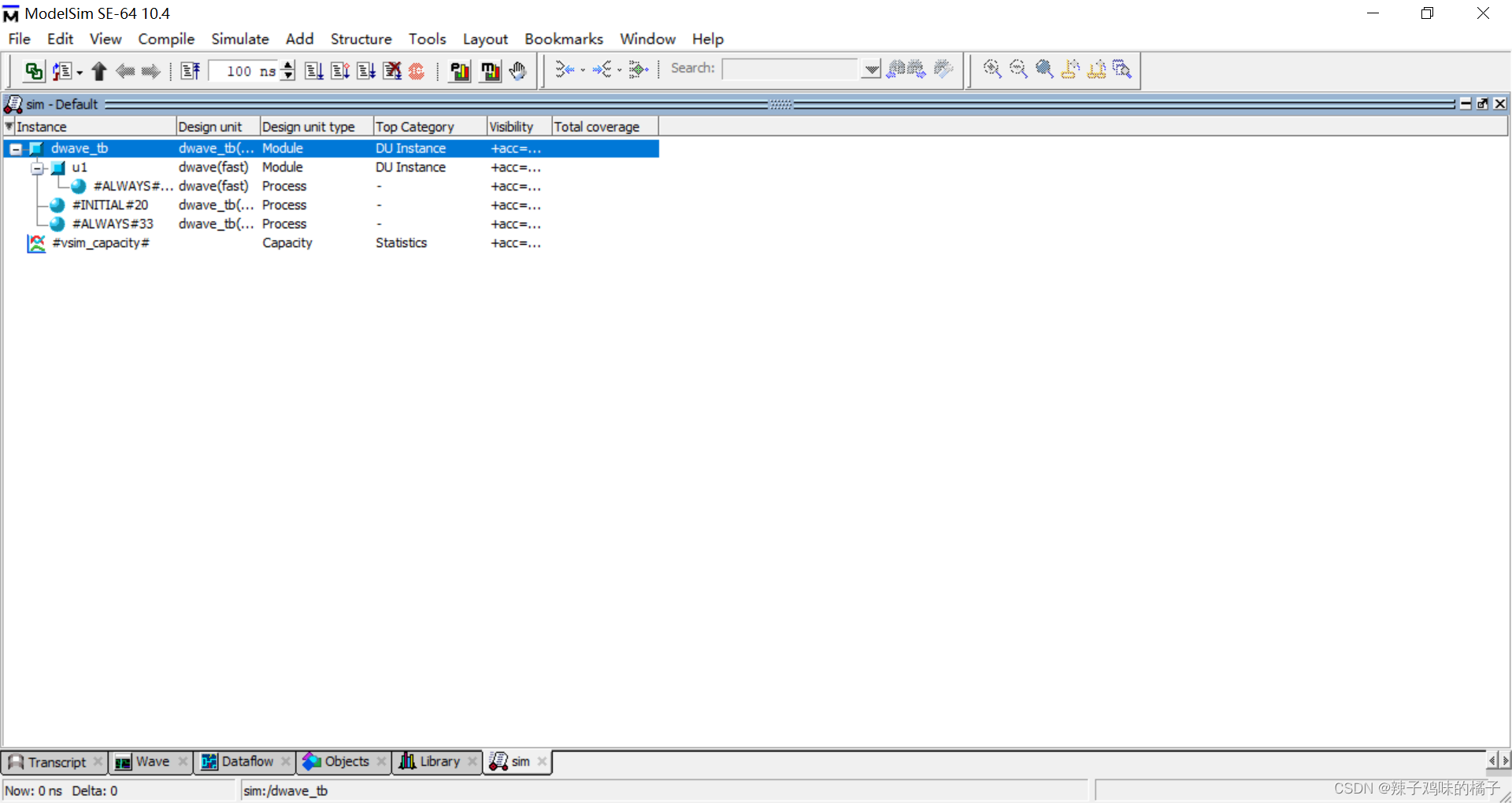

找到对应的moudle,右键点击slimuate进行仿真

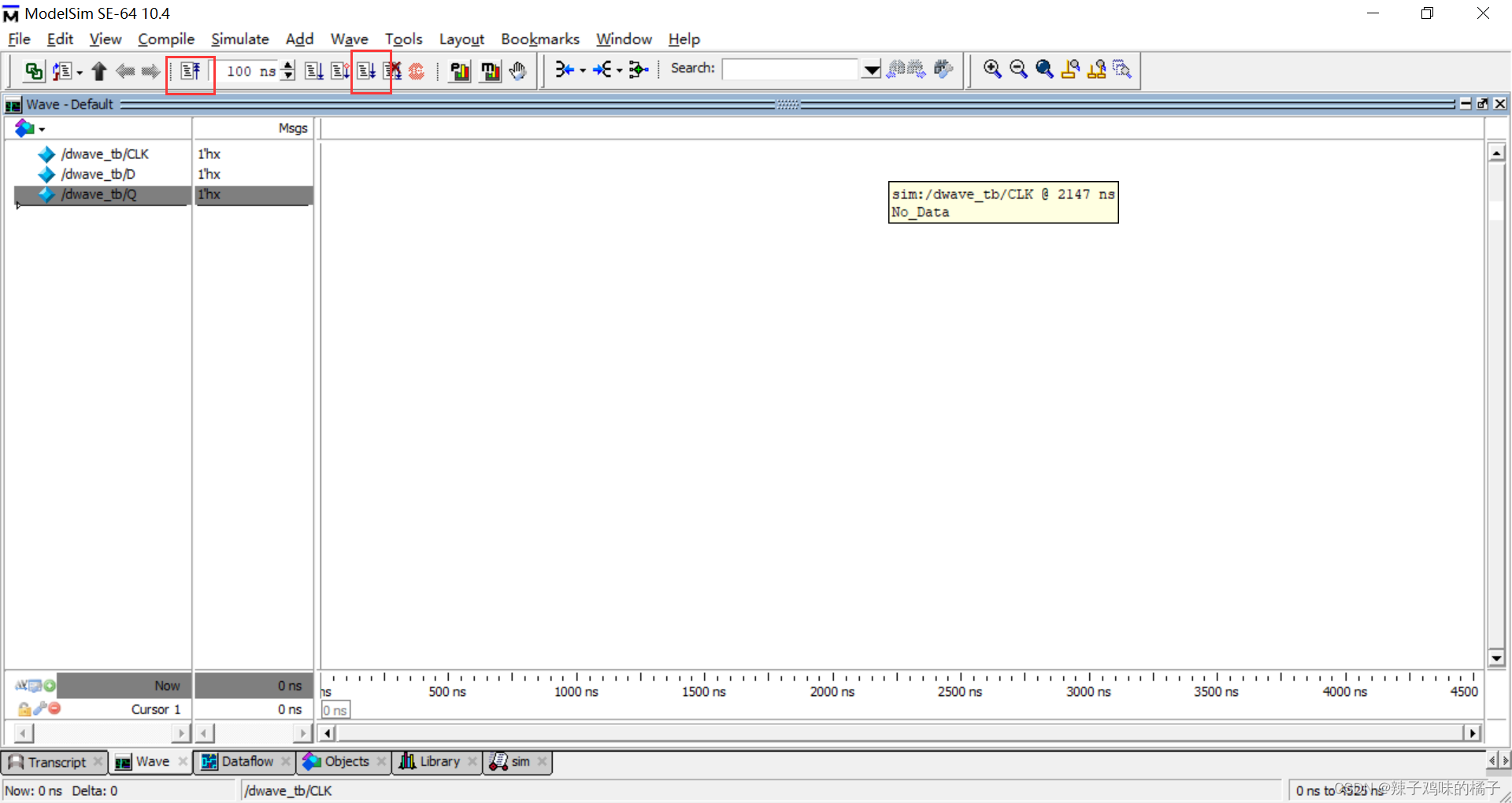

右键找到add wave添加到wave中

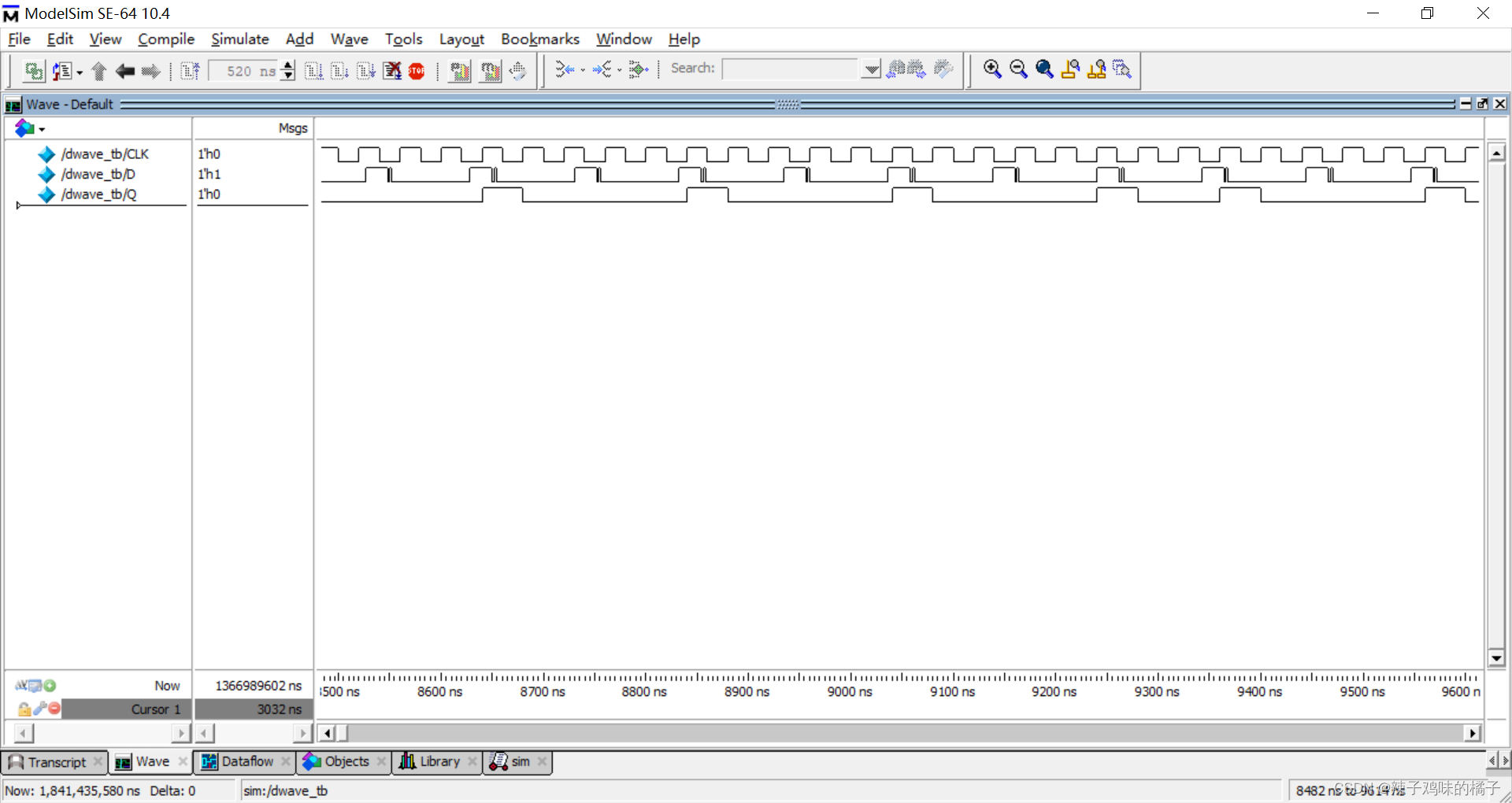

按照图中进行点击,查看运行结果

4、总结

对于verliog语言和quartus使用刚刚初学,还有很多路要走,对于许多语法特性还不能掌握,希望后面能得到改正

3158

3158

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?