简单cpu Mu0,8051兼容cpu

MU0是一个用Verilog设计的处理器,它是一个8051兼容的CPU。

8051微控制器是一个8位的CPU,意味着它一次可以处理8位(1字节)的数据。

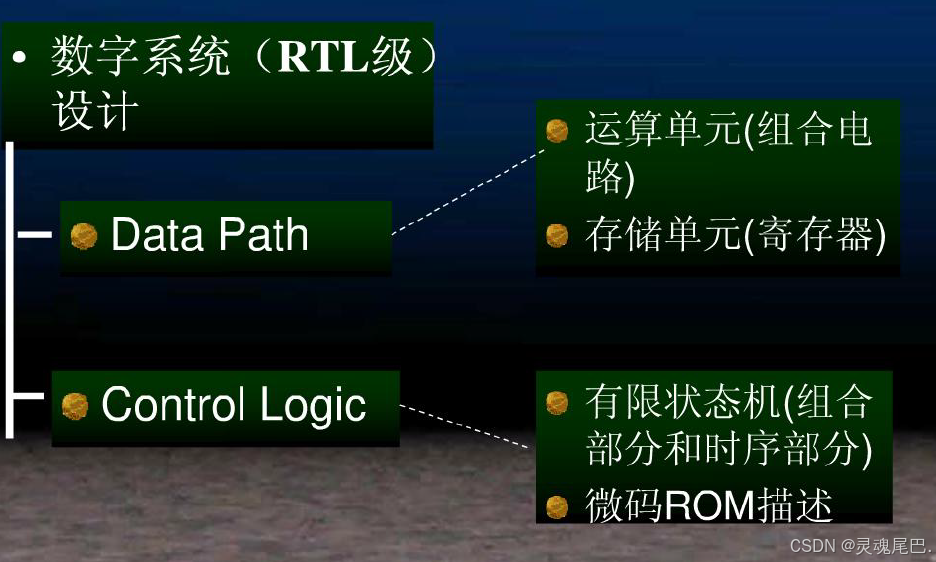

运算单元,存储单元,有限状态机

微码是一系列低级的机器语言指令,用于控制处理器的硬件操作。

微码(Microcode):微码是用简单的硬件操作来模拟当时无法用技术直接实现的复杂指令。它是一种软件技术,用于实现硬件设计,通常存储在处理器的ROM中,实现了一系列底层硬件操作。

微码的主要作用是将机器指令与相关的电路实现分离,这样一来机器指令可以更自由地进行设计与修改,而不用考虑到实际的电路架构。使用微指令架构可以在降低电路复杂度的同时,建构出复杂的多步骤机器指令

- RAM:用于需要频繁读写的场景,如运行中的程序和临时数据存储。

- ROM:用于存储不经常改变的系统级软件,如启动程序、固件更新等。

-

RAM(Random Access Memory):随机存取存储器,是一种可以快速存取数据的存储设备,允许按任意顺序访问存储器中的任何位置。

-

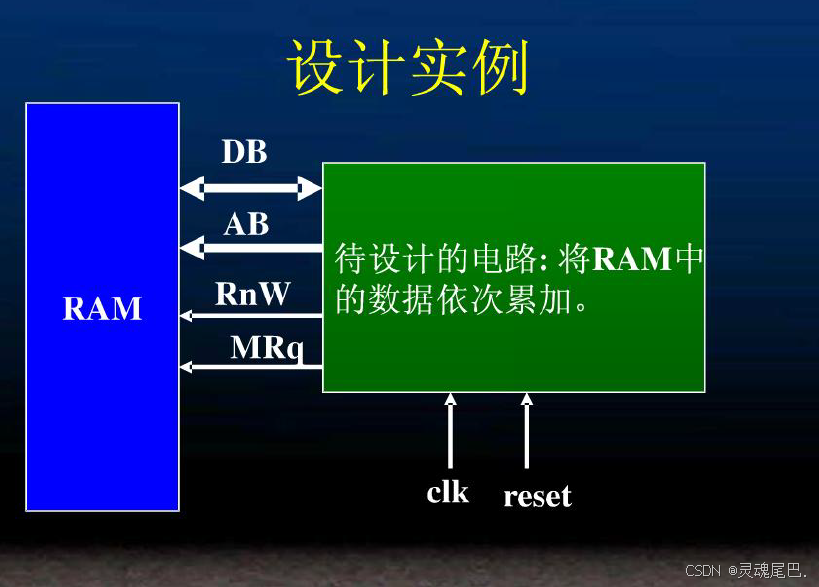

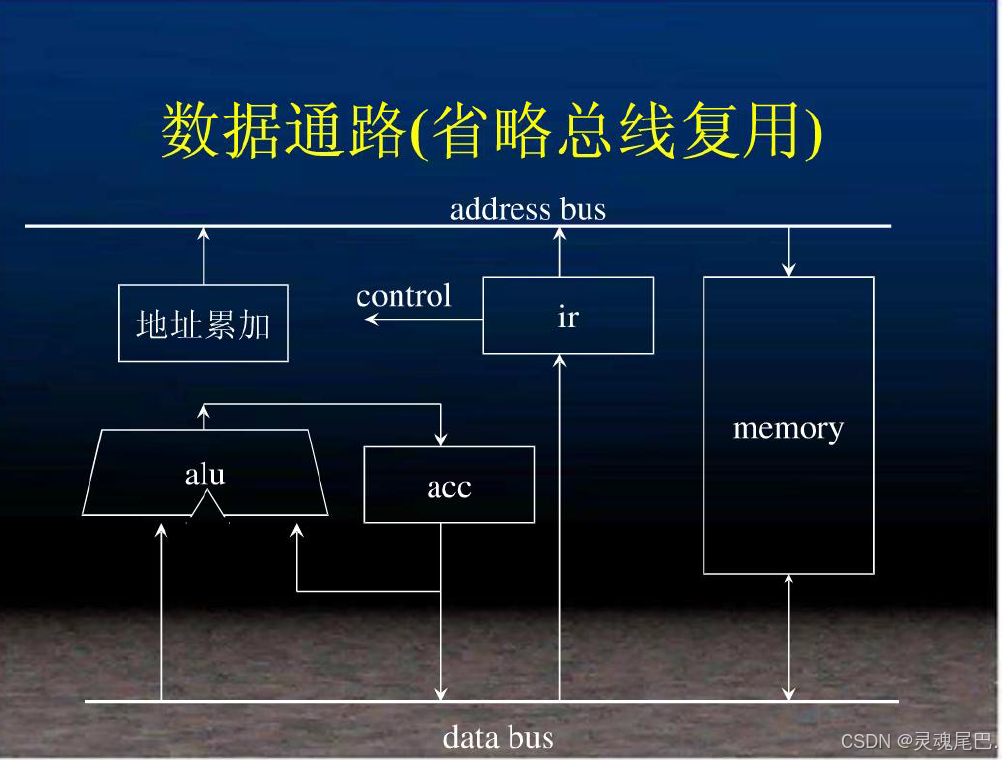

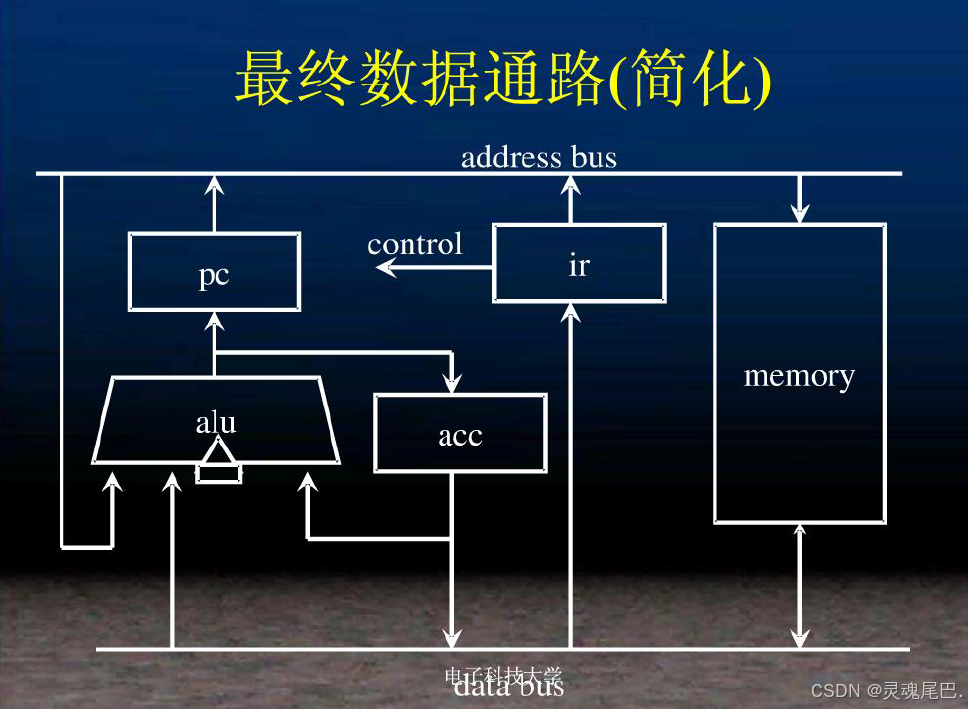

DB:data bus

-

AB:这可能代表地址总线(Address Bus),用于指定RAM中数据将要被读取或写入的地址。

-

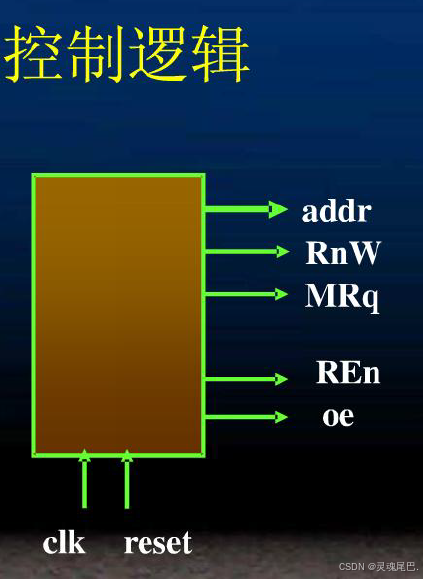

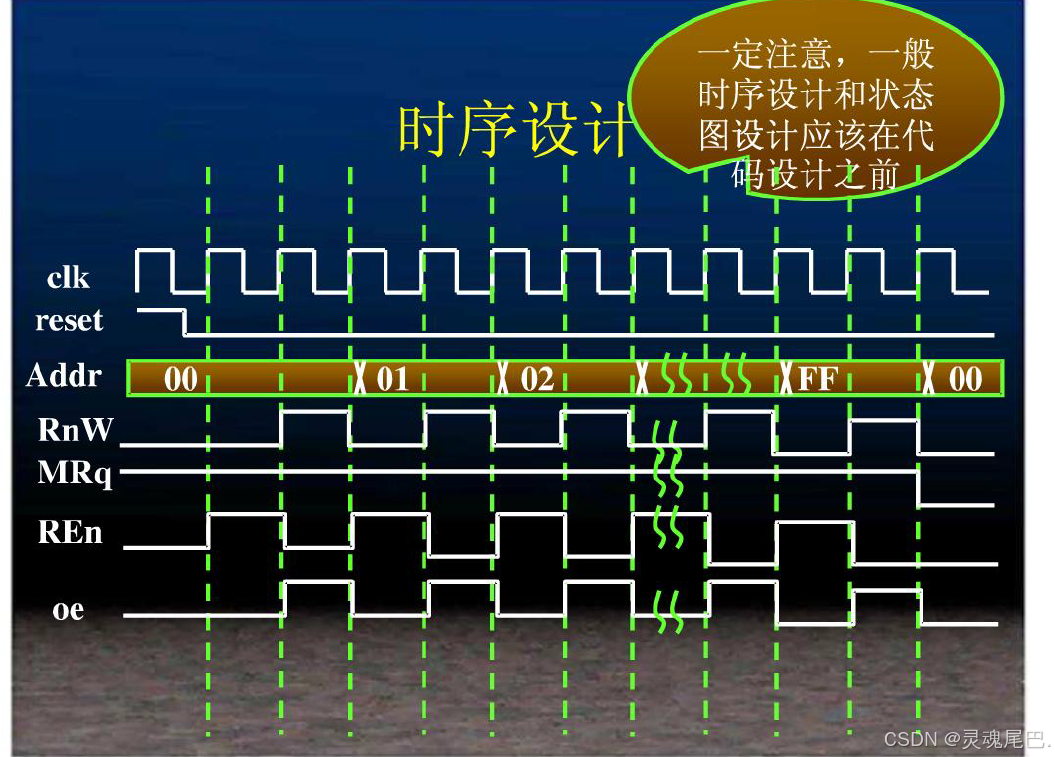

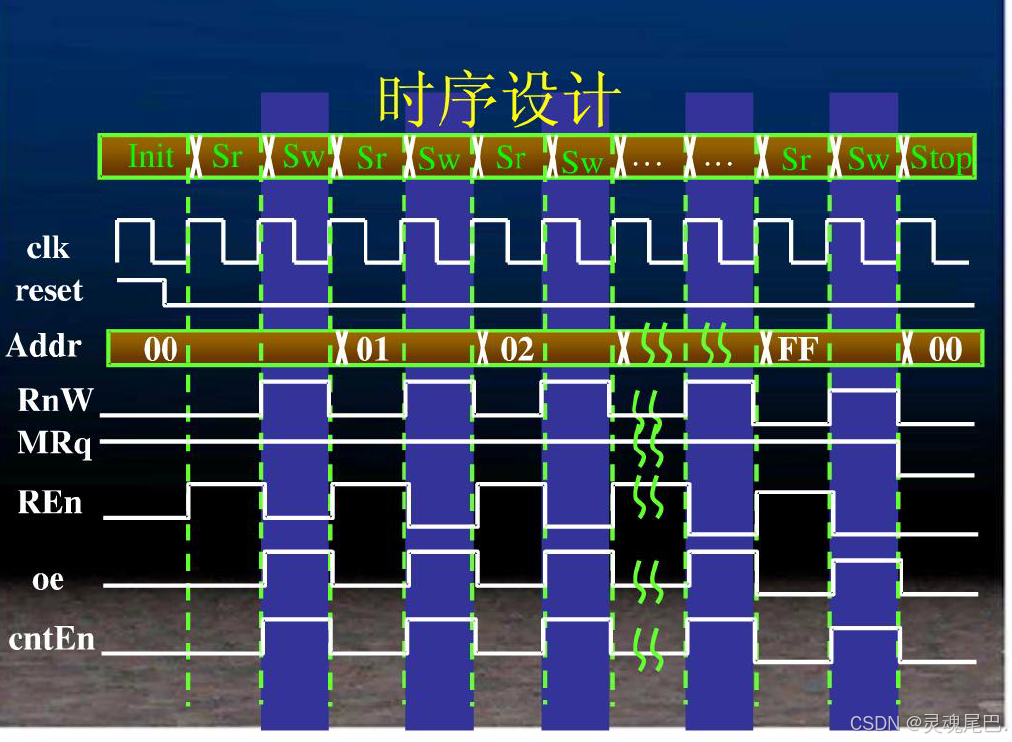

RnW(Read/Write):这是一个控制信号,用于指示操作是读操作(Read)还是写操作(Write)。当RnW信号为低电平时,通常表示写操作;为高电平时,表示读操作。

-

MRq:这可能是一个请求信号(Memory Request),用于指示一个内存访问请求。在某些系统中,MRq信号可能用于告诉内存控制器一个访问请求即将到来。

这意味着电路需要能够从RAM中读取数据,执行累加操作,并将结果写回RAM。

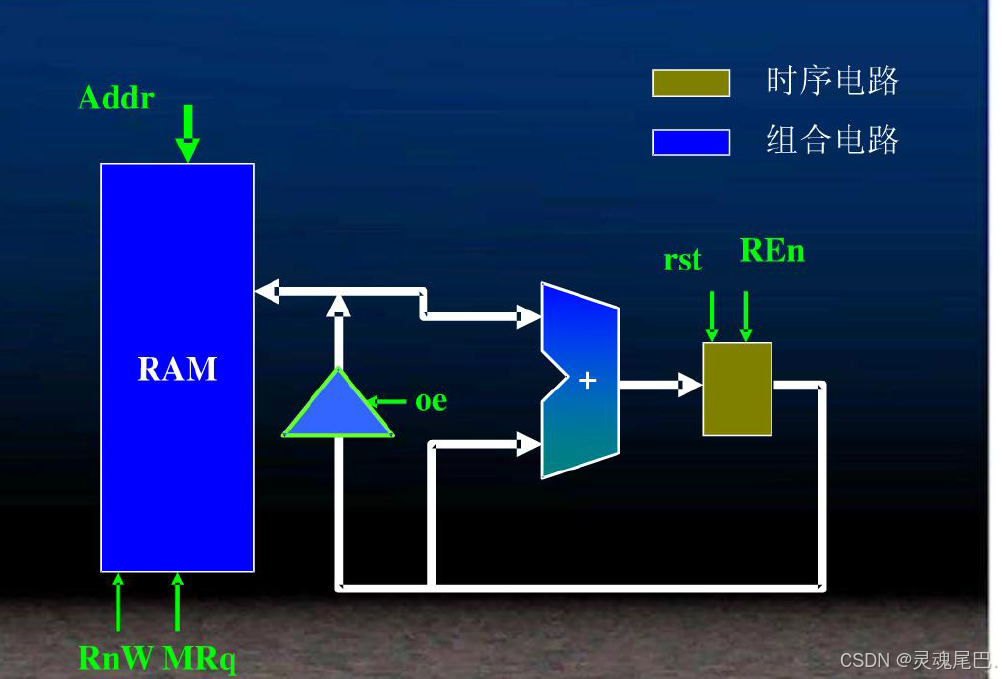

下图 数据链路

"OE"代表"Output Enable",中文意思是输出使能端或输出允许信号。

-

REn(Read Enable):

- 读使能信号,当该信号被激活(通常为低电平有效)时,允许从RAM中读取数据。

-

地址计数器(Address Counter):

- 地址计数器是一个计数器,用于生成或跟踪内存地址。在RAM操作中,它可能用于自动递增地址以访问连续的内存位置。

-

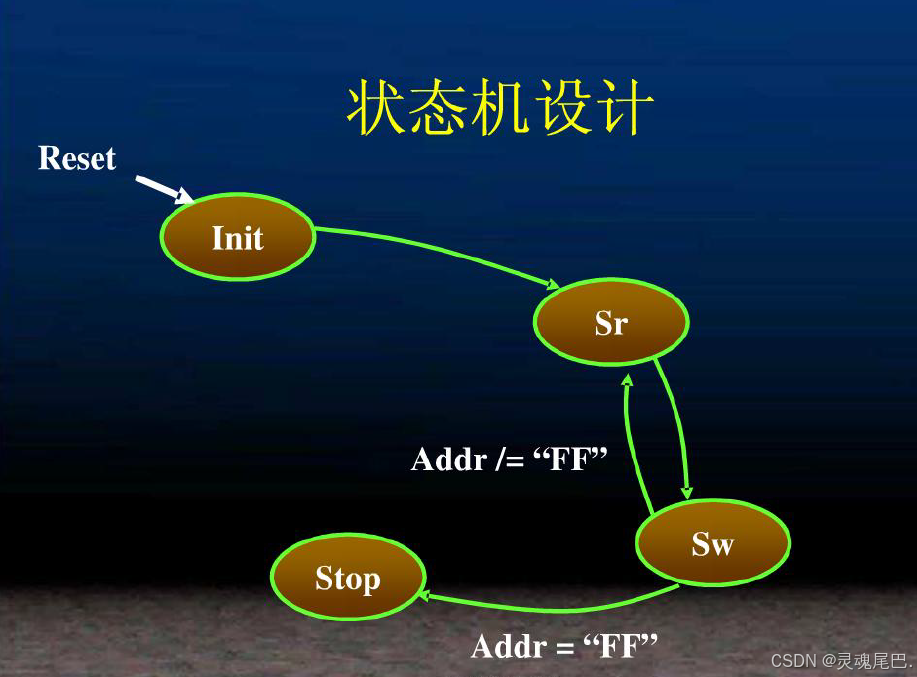

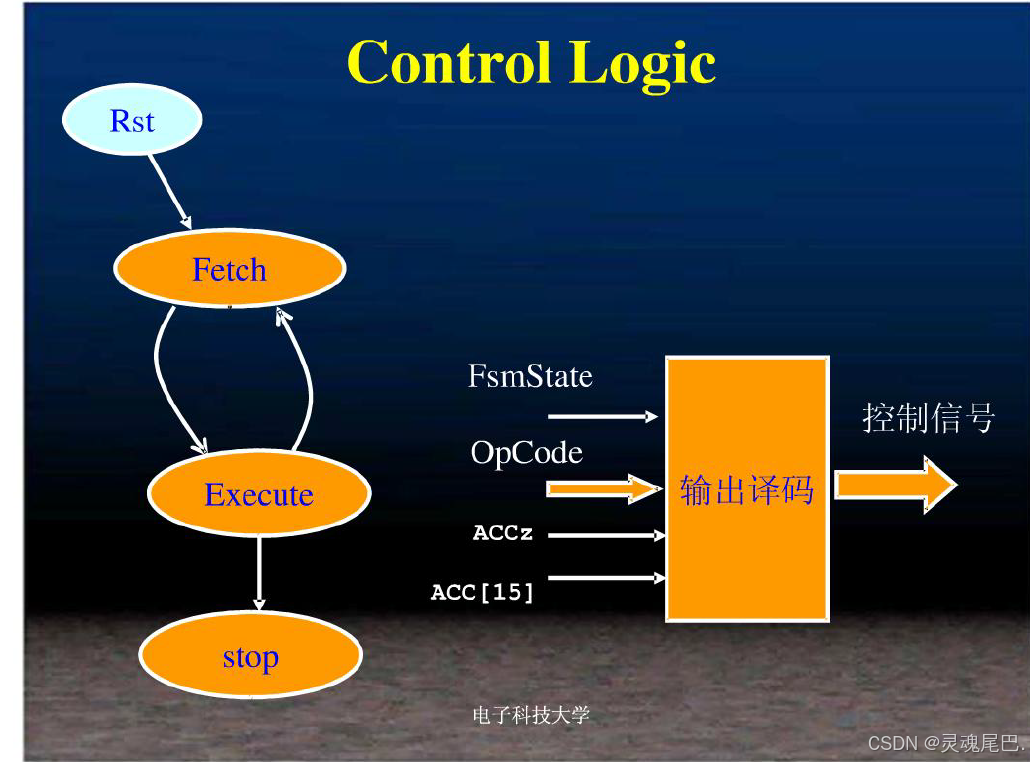

FsmNst(Next State):

- 次态译码,这是有限状态机(FSM)的一部分,用于根据当前状态和输入决定下一个状态。

-

FsmCst(Current State):

- 当前状态,这也是有限状态机(FSM)的一部分,表示FSM的当前状态。

-

输出译码(Output Decode):

- 输出译码是组合电路的一部分,用于根据输入信号生成特定的输出信号。

-

State_regs(State Registers):

- 状态寄存器,用于存储有限状态机的当前状态。

Sr Sw (Set read,set write:

- 这是一个设置读写的状态

SR触发器的名称源于其两个输入端的名称:S表示“设置”(Set),R表示“复位”(Reset)。

-

Addr/=“FF”:

- 这个表达式可能表示地址不等于“FF”(“FF”通常在十六进制中代表255,或在二进制中代表全1)。在状态机的上下文中,这可能表示一个条件,即只有当地址不等于“FF”时,状态机才会进行某种操作或转换。

-

Addr=“FF”:

- 与Addr/=“FF”相反,这个表达式表示地址等于“FF”。这可能是状态机中的一个特定条件或状态,触发特定的行为或状态转换。

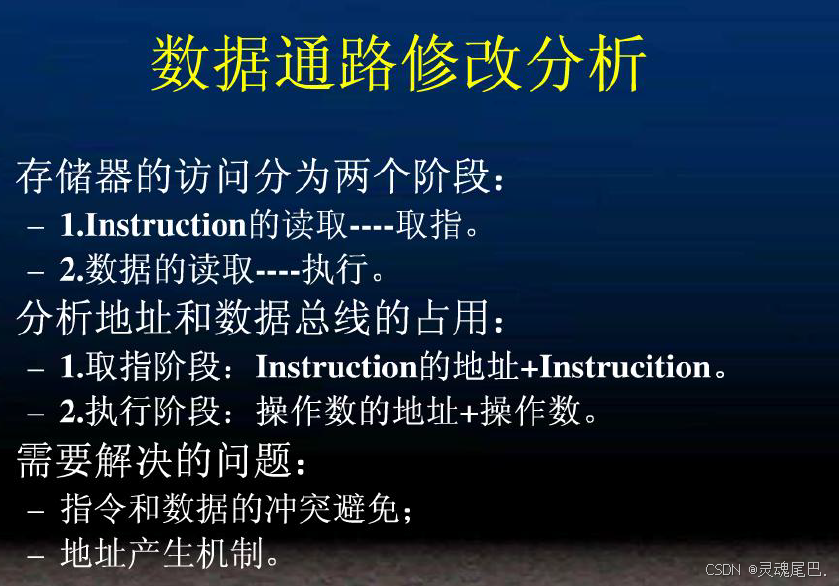

IR寄存器,全称为指令寄存器(Instruction Register),是CPU中用于暂时存储当前正在执行的一条指令的寄存器。当CPU需要从内存中读取一条新指令时,该指令首先被加载到IR寄存器中。IR寄存器保存了指令的完整信息,包括操作码(Opcode)和操作数地址等。

IR寄存器的主要功能包括:

- 指令暂存:IR寄存器用于存放当前从主存储器读出的正在执行的一条指令。

- 操作码分析:指令包括操作码和地址码两个字段,为了执行指令,必须对操作码进行测试,识别出所要求的操作,指令译码器(Instruction Decoder,ID)就是完成这项工作的。指令译码器对指令寄存器的操作码部分进行译码,以产生指令所要求操作的控制电位,并将其送到微操作控制线路上。

- 指令执行控制:指令寄存器中操作码字段的输出就是指令译码器的输入。操作码一经译码,即可向操作控制器发出具体操作的特定信号。

简而言之,IR寄存器在CPU中扮演着指令的临时存储和解析的关键角色,确保CPU能够正确理解和执行程序中的每一条指令。

-

S域(操作数地址域):

- 在某些处理器设计中,IR寄存器被分为几个部分,其中一部分专门用来存储操作数地址。这个部分有时被称为S域,即“地址域”(Address field)或“操作数域”(Operand field)。

-

产生操作数地址:

- 当CPU从内存中取出指令并将其加载到IR寄存器时,S域中的内容就是操作数的地址。这个地址随后被用来访问内存,以获取或存储数据。

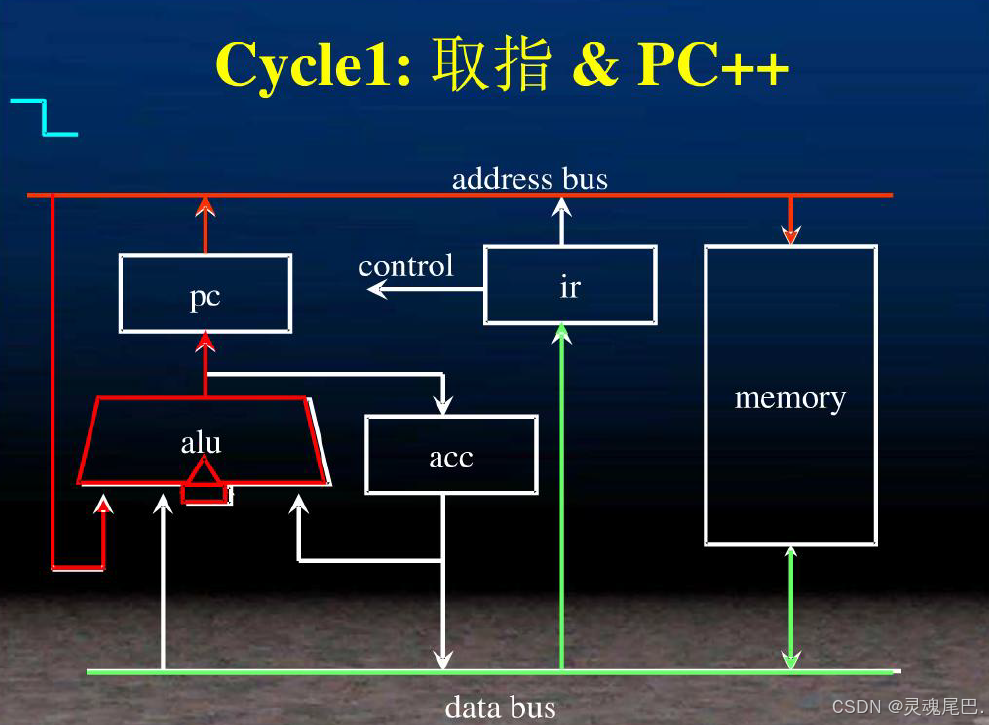

PC++" 指令通常指的是将程序计数器(Program Counter,PC)的值增加1

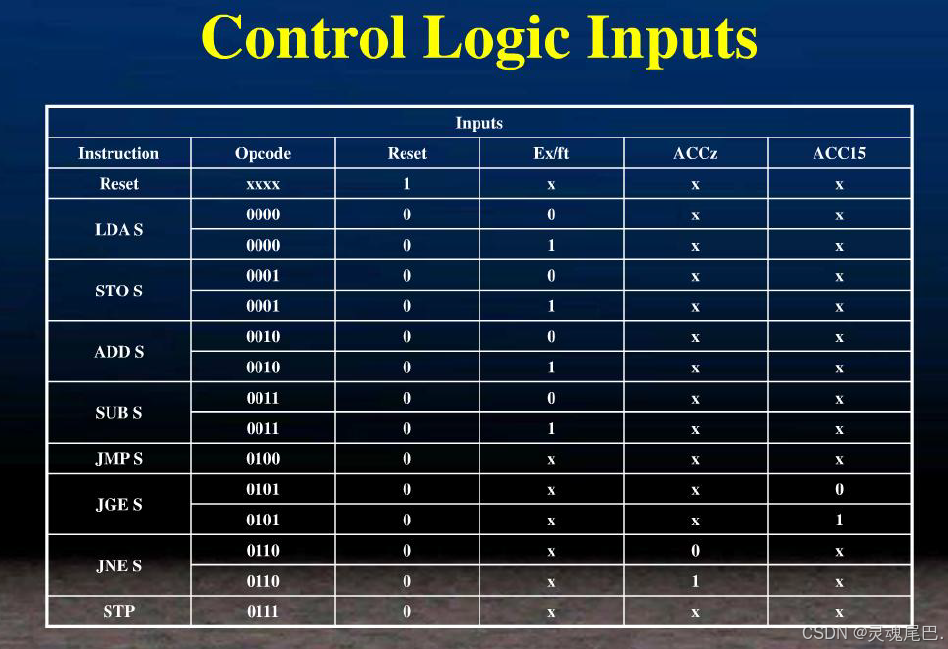

这张图描述了一个数字电路设计中的控制逻辑输入部分,特别是针对MU0处理器的指令集。控制逻辑是数字电路中负责根据输入信号生成控制信号的部分,这些信号用于管理数据流和时序,以执行特定的操作。以下是对表格中每一列和每一行的解释:

列标题解释:

-

Inputs:

- 这一列可能表示不同的输入信号,用于控制逻辑的决策过程。

-

Instruction:

- 表示当前正在执行的具体指令。

-

Opcode:

- 操作码,是指令中用于识别指令类型的部分。

-

Reset:

- 复位信号,用于将电路重置到初始状态。

-

Ex/ft:

- 这个信号可能表示“执行/ fetch”(Execution/Fetch),用于区分当前周期是执行指令还是获取下一条指令。

-

ACCz:

- 累加器(Accumulator)的零标志,表示累加器中的值是否为零。

-

ACC15:

- 累加器的第15位,可能用于特定的条件判断,如符号位或溢出检测。

行解释:

-

Reset:

- 当复位信号被激活(值为1),其他所有信号都被忽略,处理器被重置。

-

LDAS(Load Accumulator from Storage):

- 从存储器加载数据到累加器的指令。根据

Ex/ft的值(0表示获取指令,1表示执行指令),控制逻辑可能需要生成不同的控制信号。

- 从存储器加载数据到累加器的指令。根据

-

STOS(Store Accumulator in Storage):

- 将累加器的数据存储到存储器的指令。

-

ADDS(Add Storage to Accumulator):

- 将存储器的数据加到累加器的指令。

-

SUB S(Subtract Storage from Accumulator):

- 从累加器减去存储器的数据的指令。

-

JMPS(Jump to Storage):

- 跳转到存储器指定地址的指令。

-

JGES(Jump if Greater than or Equal to Zero):

- 如果累加器的值大于或等于零,则跳转到指定地址的指令。

-

JNE S(Jump if Not Equal to Zero):

- 如果累加器的值不等于零,则跳转到指定地址的指令。

-

STP(Stop):

- 停止执行的指令。

表格中的"X":

- 表格中的"X"表示在该特定指令的上下文中,该输入信号的值是无关紧要的,或者不参与该指令的控制逻辑决策。

这张图提供了一个控制逻辑的设计视图,展示了不同的指令和条件如何影响控制信号的生成。这是数字电路设计和计算机体系结构中的一个关键部分,它确保了指令能够正确地被执行。

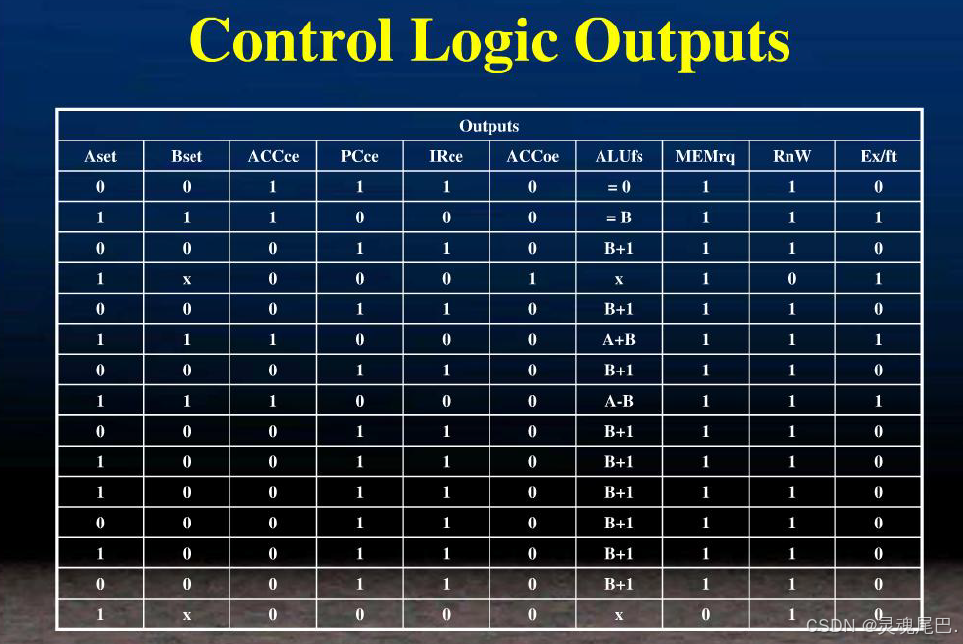

张图描述了一个数字电路设计中的控制逻辑输出部分,具体来说是MU0处理器的控制信号输出。控制逻辑输出决定了各个组件在每个时钟周期的行为。以下是对表格中每一列和每一行的解释:

列标题解释:

-

Aset:

- 地址寄存器A的设置信号。

-

Bset:

- 地址寄存器B的设置信号。

-

ACCce:

- 累加器(ACC)的时钟使能信号。

-

PCce:

- 程序计数器(PC)的时钟使能信号。

-

IRce:

- 指令寄存器(IR)的时钟使能信号。

-

ACCoe:

- 累加器的输出使能信号。

-

ALUfs:

- 算术逻辑单元(ALU)的功能选择信号。

-

MEMrq:

- 内存请求信号。

-

RnW:

- 读/写控制信号。

-

Ex/ft:

- 执行/取指控制信号。

行解释:

表格的每一行代表不同的指令或状态,显示了在该指令或状态下各个控制信号的值。例如:

-

第一行(通常为复位状态):

Aset = 0,Bset = 0,ACCce = 1,PCce = 1,IRce = 1,ACCoe = 0,ALUfs = 0,MEMrq = 1,RnW = 1,Ex/ft = 0。- 这意味着在复位状态下,累加器和程序计数器被允许时钟信号(允许更新),指令寄存器也被允许时钟信号,而累加器输出被禁用,算术逻辑单元功能设置为0(可能是无效或特定操作),内存请求被激活,读/写信号设置为读取,执行/取指信号设置为取指。

-

第二行(可能是LDAS指令的执行状态):

Aset = 1,Bset = 1,ACCce = 1,PCce = 0,IRce = 0,ACCoe = 0,ALUfs = B,MEMrq = 1,RnW = 1,Ex/ft = 1。- 这意味着在执行LDAS指令时,地址寄存器A和B被设置,累加器允许时钟信号,程序计数器不允许时钟信号(保持当前值),指令寄存器不允许时钟信号(保持当前指令),累加器输出被禁用,算术逻辑单元功能设置为B(可能是将B寄存器的值传送到累加器),内存请求被激活,读/写信号设置为读取,执行/取指信号设置为执行。

表格中的"X"和"=":

- 表格中的"X"表示在该特定指令的上下文中,该输出信号的值是无关紧要的或者不使用的。

- "="符号(如

ALUfs = 0或ALUfs = B+1)表示ALU功能选择信号的值取决于特定的操作或条。

微码ROM和硬连线逻辑是实现处理器控制逻辑的两种方式。

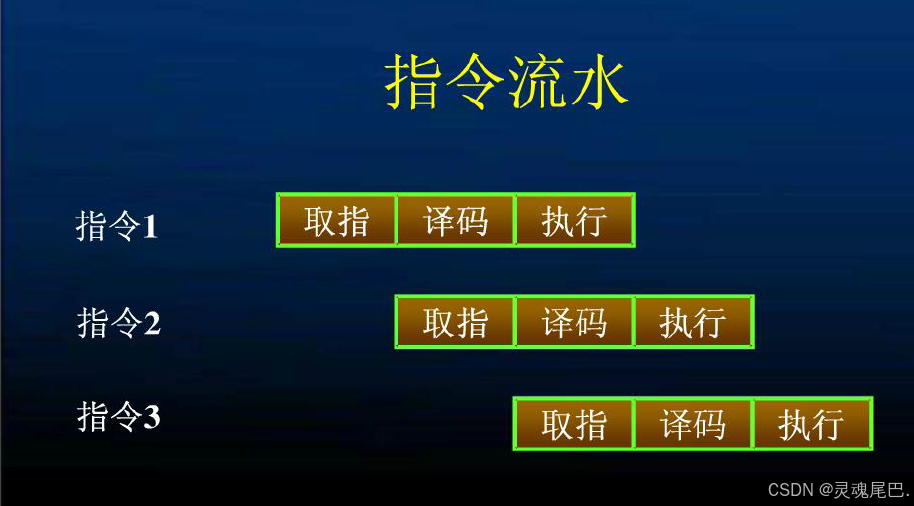

- 通过流水线技术,可以将指令的执行过程分解成多个阶段,并行处理,减少每个指令的周期时间。

- 特别提到了流水线MU0需要将跳转指令的指令周期扩展成2个时钟周期,这可能是为了处理跳转延迟或确保正确的流水线操作。

-

提高系统时钟频率:

- 通过增加CPU的时钟频率,可以加快指令的执行速度,从而提高处理器的性能。

-

微码ROM硬连线逻辑:

- 使用微码ROM或硬连线逻辑来实现控制逻辑,可以提高指令译码和执行的速度。

-

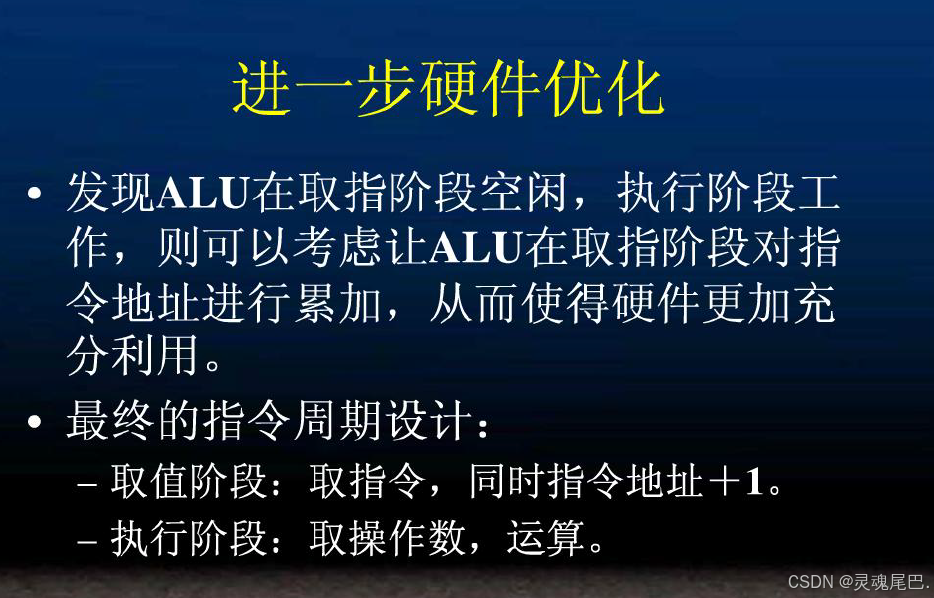

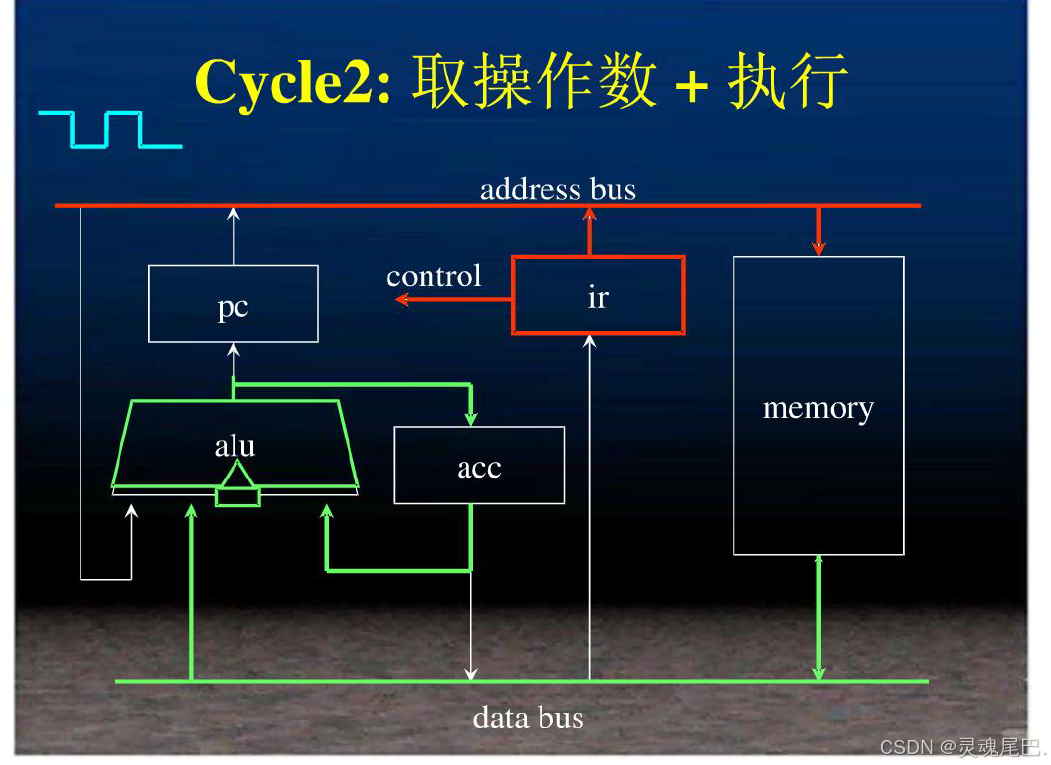

指令流水线:

- 通过流水线技术,可以将指令的执行过程分解成多个阶段,并行处理,减少每个指令的周期时间。

- 特别提到了流水线MU0需要将跳转指令的指令周期扩展成2个时钟周期,这可能是为了处理跳转延迟或确保正确的流水线操作。

-

程序与数据总线分开:哈佛总线:

- 哈佛架构允许将指令和数据存储器分开,这意味着它们可以同时被访问,提高了数据吞吐量。

- 这种架构通过分离程序和数据总线来提高性能,被称为哈佛总线结构。

-

进一步提高IPC:超标量结构:

- 超标量结构是指CPU在单个时钟周期内可以执行多条指令的技术,可以显著提高每周期指令数(IPC)。

- 这种结构允许CPU动态调度和并行执行多条指令。

-

突破存储器带宽瓶颈:指令Cache和数据Cache:

- 引入Cache可以减少访问主存储器的需求,通过在CPU附近存储频繁使用的数据和指令来提高性能。

- 指令Cache用于存储即将执行的指令,而数据Cache用于存储频繁访问的数据。

-

DSP中,引入硬件乘加器等以提高数据处理速度:

- 在数字信号处理器(DSP)中,通过引入专用的硬件乘加器,可以加速数学运算,特别是对于信号处理和多媒体应用中的乘法和累加操作。

1413

1413

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?