关于打拍优化时序你真的全面了解吗?-电子发烧友网 (elecfans.com)

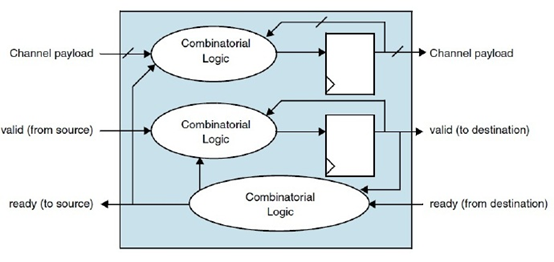

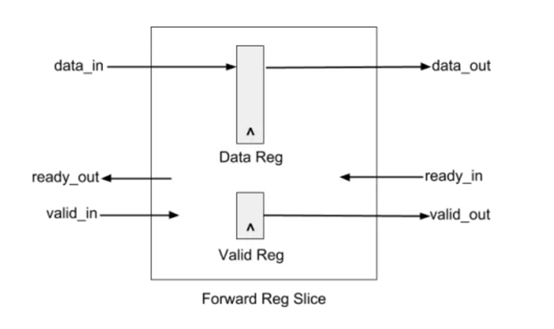

Forward Registered

always @(posedge clk or negedge rst_n)

begin if (rst_n == 1‘d0)

valid_dst 《= 1’d0;

else if (valid_src == 1‘d1)

valid_dst 《= #`DLY 1’d1;

else if (ready_dst == 1‘d1)

valid_dst 《= #`DLY 1’d0;

end

always @(posedge clk or negedge rst_n)

begin if (rst_n == 1‘d0)

payload_dst 《= ’d0;

else if (valid_src == 1‘d1 && ready_src == 1’d1)

payload_dst 《= #`DLY payload_src;

end

ready_src = (~valid_dst) | ready_dst

-

复位条件:

if (rst_n == 1'b0)这个条件检查异步复位信号

rst_n是否激活(低电平)。如果是,它将valid_dst和payload_dst信号重置为初始状态。 -

有效信号同步:

else if (valid_src == 1'b1) valid_dst <= #`DLY 1'b1; else if (ready_dst == 1'b1) valid_dst <= #`DLY 1'b0;这些行管理

valid_dst信号,该信号表示是否有数据可供传输。#符号前的DLY表示延迟,由DLY参数定义。这可能用于模拟时钟周期延迟或特定时间延迟。- 如果

valid_src(源有效信号)为高,valid_dst在延迟后被置为高。 - 如果

ready_dst(目标就绪信号)为高,它表示目标已准备好接受新数据,因此valid_dst在延迟后被清除。

- 如果

-

负载传输:

else if (valid_src == 1'b1 && ready_src == 1'b1) payload_dst <= #`DLY payload_src;此条件检查

valid_src和ready_src(源就绪信号)是否都为高,这表示是时候传输数据了。然后payload_src在定义的延迟后被赋值给payload_dst。 -

就绪信号生成:

ready_src = (~valid_dst) | ready_dst;这行计算

ready_src信号。它由valid_dst的非值和ready_dst的逻辑或产生。这意味着如果valid_dst不高(数据已被接受且当前无效)或ready_dst为高(目标已准备好接受更多数据),ready_src将为高。

需要注意的是,代码中使用了 1'b0 和 1'b1 来明确定义0和1的位级常量,这是Verilog中避免任何歧义的常见做法。

always @(posedge clk or negedge rst_n) 块表示块内的行为应在 clk 信号的正边沿或 rst_n 信号的负边沿时执行。

# 运算符用于延迟,这可能表示时钟周期延迟或根据仿真设置或综合指令的特定时间延迟。

现在来分析下上述Forward Registered 打拍代码的几个输出端口:

valid_dst:在master发请求(拉高valid_src)时拉高valid_dst,直到当前master没有valid请求并且slave可以接收请求(拉高ready_dst)时拉低valid_dst,表示一次传输完成。

payload_dst:在master发请求(拉高valid_src),并且前面没有请求、请求已经被接收或者正在被接收时将payload_src打拍赋给payload_dst。

其实master本身也会遵循valid-ready协议,payload_src和valid_src做同样处理就行,即也可以在(valid_src == 1‘d1 && ready_src == 1’d0)时进行赋值,因为此时payload_src输入应该约束保持原始数据。

ready_src:register slice或者slave可以接收数据时拉高ready_src.

原文标题:打拍优化时序不像听起来那么简单

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

916

916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?