半加器和全加器

半加器

半加:只考虑两个加数本身,不考虑低位进位的加法运算。实现半加运算的逻辑电路称为半加器。

其对应真值表为:

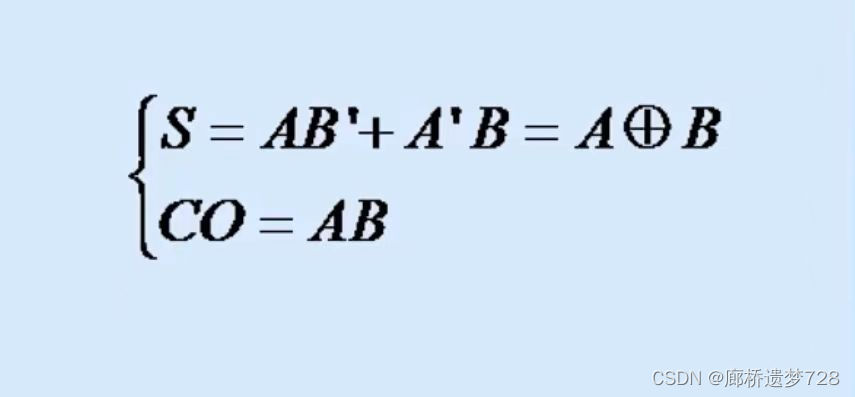

由真值表可得逻辑表达式:

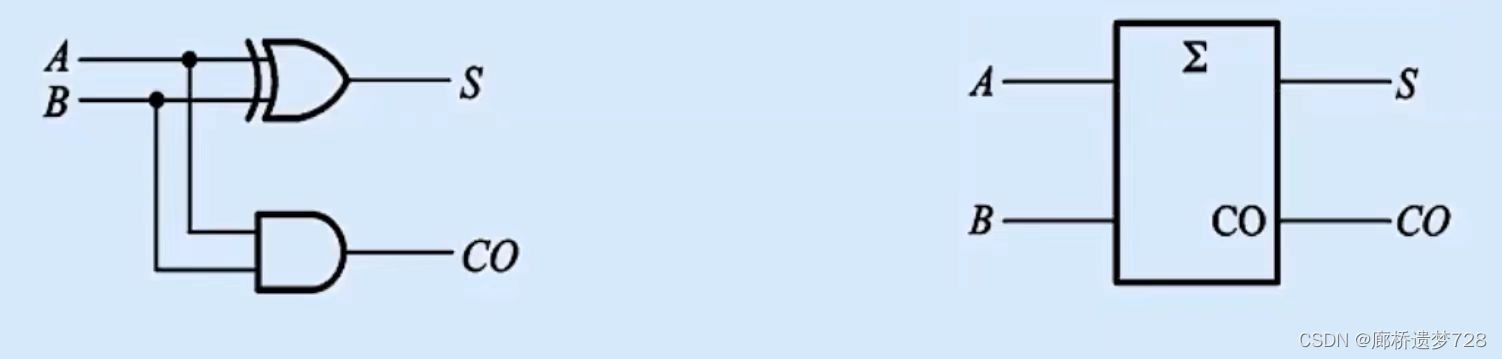

逻辑电路和框图如下:

逻辑电路和框图如下:

其中,CO为进位输出端,S为求和输出端。

全加器

全加:能完成被加数、加数和低位进位信号的相加的运算。实现全加运算的逻辑电路称为全加器。

其对应真值表为:

半加:只考虑两个加数本身,不考虑低位进位的加法运算。实现半加运算的逻辑电路称为半加器。

其对应真值表为:

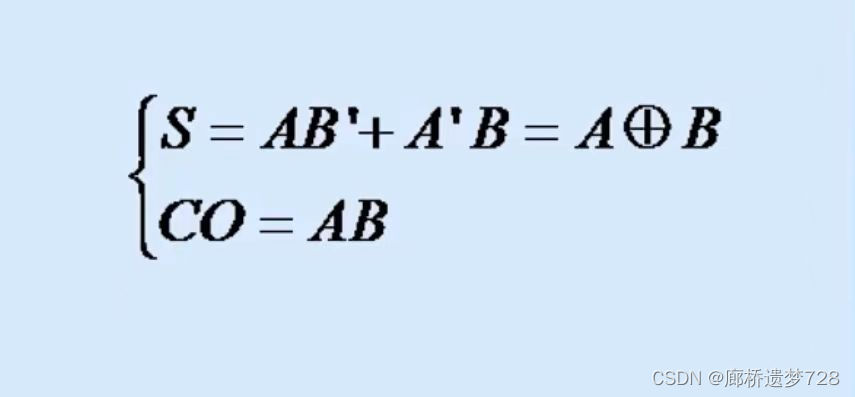

由真值表可得逻辑表达式:

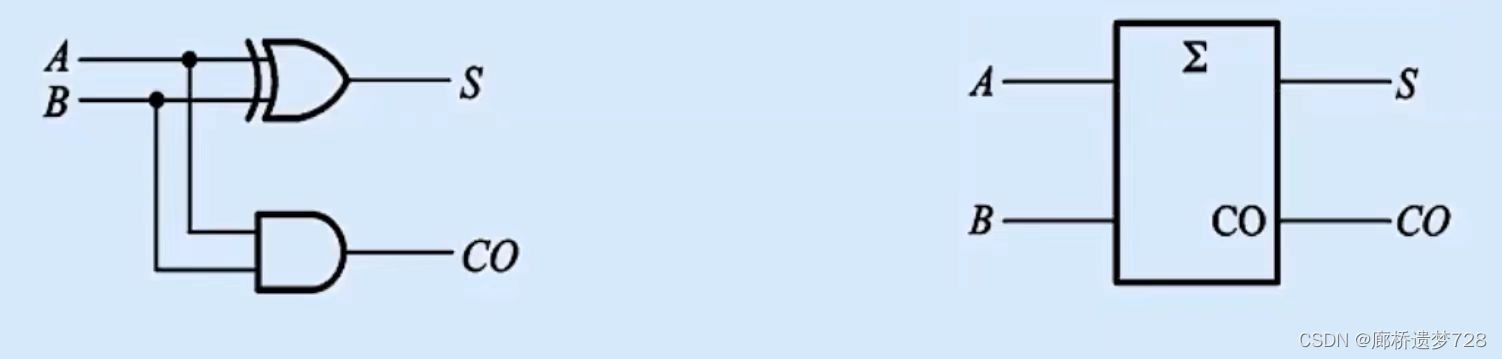

逻辑电路和框图如下:

逻辑电路和框图如下:

其中,CO为进位输出端,S为求和输出端。

全加:能完成被加数、加数和低位进位信号的相加的运算。实现全加运算的逻辑电路称为全加器。

其对应真值表为:

726

726

2011

2011

3911

3911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?