本篇内容,基于阅读J. Bhasker • Rakesh Chadha著作《Static Timing Analysis for Nanometer Designs》后进行的总结以及自己的观点和感想,如有不正确的地方,还请指点。读者有微电子基础将更好理解内容。(图片内容绝大部分直接引用书中)

本章节介绍STA check中各种timing相关的check。

前面有做过介绍,timing path一共分为4类,i2reg, reg2reg, reg2o,i2o,其中大量的检查应该是reg2reg。对于reg2reg的timing检查项又分为很多种,其中setup/hold check最为常见。

1. setup/hold timing check

关于setup/hold timing 的check,有专门拎出来一个文章介绍Timing Check – hold/setup check原理介绍。此处不再赘述,这个部分讨论一些我觉得可能比较重要或者比较疑惑的问题。

1.1 端口约束的min/max值

其实前面也有介绍端口约束的内容,set_input_delay/set_output_delay这样的命令

其实前面也有介绍端口约束的内容,set_input_delay/set_output_delay这样的命令。

以set_input_delay举例:

如果check setup,set_input_delay 2 –max –clocks CLK [get_ports PORT1]

如果check hold, set_input_delay 0 –min –clocks CLK [get_ports PORT1]

可以发现。Setup/hold 的端口处的约束有所不同,第一点是max/min的约束,针对setup/hold不同的check,第二点就是约束值了。通常情况下,对于setup check,这个max的值都是大于0的值,往往是一个比较大的值,这是为了把该design做的足够短,这样到了上一层,之间的path往往更容易满足。而对于hold check,这个min的值一般都是小于或者等于0的,这个也是取决于hold的检查方式,期望本层design的端口处hold timing足够,那么到了外层也更容易满足hold检查。

1.2 关于端口约束的时钟

关于virtual clock的内容,为什么要有这个虚拟时钟呢?其实很多比较标准的公司,design设计中对于block的port口,都有相应的clock的端口约束的描述。那对于没有描述的端口,或者没有描述的端口非常多的情况,其实可以拿一个virtual clock去做一个统一的约束,这样比较粗糙,但是节省时间和效率。

2. Multicycle Paths

2.1 Multicycle path 概念理解

所谓的multicycle,其实就是指多个cycle 的check,通常的STA check,reg2reg,上一个时钟沿发数,下一个时钟沿收数,在一个时钟周期内保证数据能从一个reg传递到另外一个reg。但是在有的时候design会有特殊的需求,比如我不需要一个时钟周期就采到数,我可能每三个时钟周期才会去采前一个reg的数。

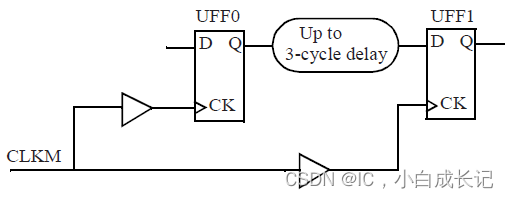

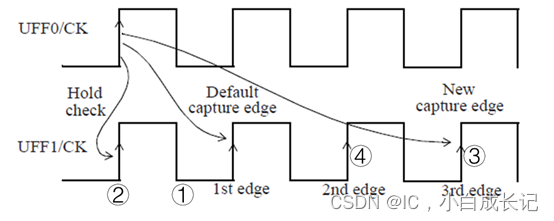

如下图所示,正常情况下①会作为我们的setup的capture时钟沿进行check,②作为默认的hold 沿进行check。 而当我们进行multicycle path的设定时候

set_multicycle_path 3 -setup -from [get_pins UFF0/CK] -to [get_pins UFF1/D]

set_multicycle_path 2 -hold -from [get_pins UFF0/CK] -to [get_pins UFF1/D]

此时的seutp check就是对应第③个时钟沿,而hold check对应第②个时钟沿。如果没有对于hold 的multicycle 设定,那么hold check 对应④这个沿,这个时候会有capture path多处来两个时钟周期,hold将会非常难以满足,报出很大的vio,这并不是我们原本期待的。

从命令里面可以看到,当setup的multicycle设置为3个时候,hold 相应设置为2个,这个怎么理解。其实从下图中依然可以看出来,一般情况下,setup check为下一个有效时钟沿,而hold check为当前有效时钟沿。因此hold check的时钟沿要比setup提前一个。而在STA工具中,会默认把hold的沿设置为setup的capture clock的前一个沿。所以当setup的时钟沿为第三个时候,那么hold设置一个2,再加上工具默认的提前一个沿,那么hold check还是在②。所以说我们在设置setup 的multicycle check时候,需要相应的设置hold 的multicycle check。

另外还有需要注意的,对于不同频率的两个clock之间path设置multicycle时候,在命令中需要指定-start/-end,start指的是相对与launch clock移动的时钟周期,end指的是相对与capture时钟移动的时钟周期。

2.1 different clock frequency cross

上个小节讲解了对于同一个clock 频率之间的timing check,如何设置multicycle以及check结果,那么对于不同频率之间的是稍微有些不同的。

2.1.1 慢到快时钟的检查

2.1.1.1 无特殊multicycle 设置

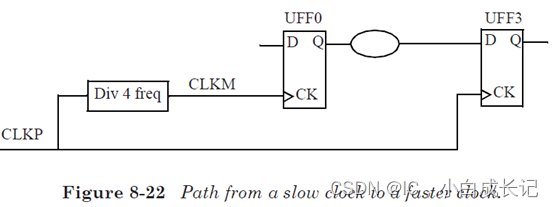

如下所示为低频到高频之间的path,当两个时钟属于同一个时钟分组,就会存在timing check。

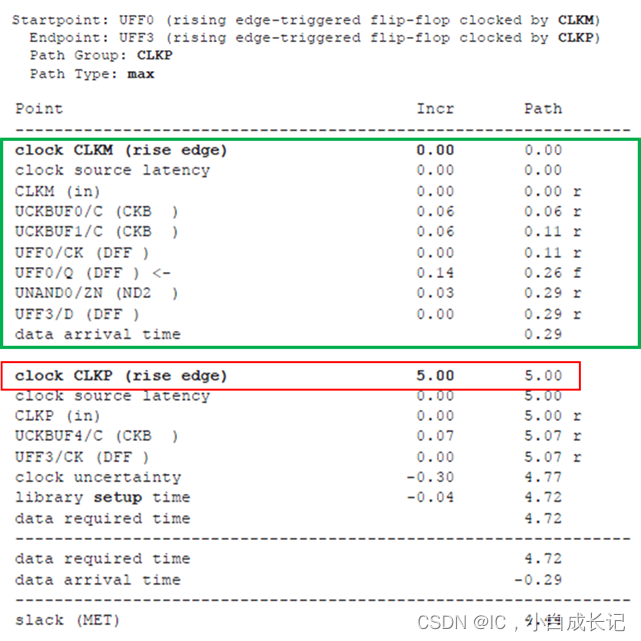

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

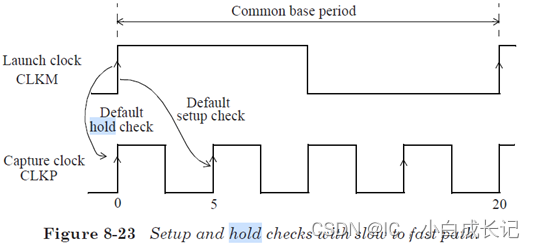

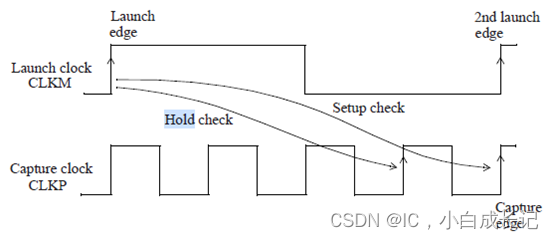

如果我们不对这两个时钟进行multicycle定义,那么STA工具会自动对两个时钟最相近的有效时钟沿进行check,如下图8-23所示,launch clock时钟沿为0,setup capture时钟沿为5ns ,STA会依然最严格的规则进行timing检查。Hold还按照capture的样子超前提一个周期,保持正常。

Setup timing report如下所示,从这个报告中可以看出来,timing 是meet的,但是在实际的电路中,如果clock skew相差很大,或者data path很长( 如下图绿色框所示),那么极易造成timing violation。

因为hold没有问题,还是同沿check,就不贴相应的path了。

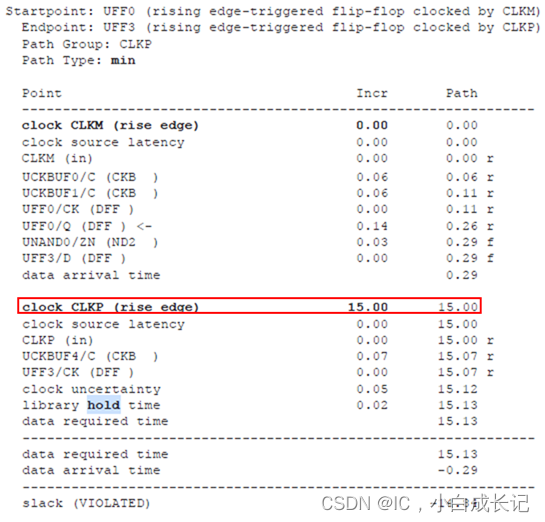

2.1.1.2 只设置setup multicycle check

如果我们只对其进行setup 的multicycle path 设定,如下命令,-end指代的是launch clock沿不变,capture clock沿按照第四个沿进行检查。那么这个时候,setup timing path中的clock CLKP (rise edge)将会变成20,如上图红色红红所示,而slack也会变成4.44+15=19.44.因为path变化不大,就不贴图了。

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] –end

但是此时的hold ,因为没有设置multicycle path ,所以检查的沿就如上图中的箭头所示,此时hold的capture clock 沿要比launch clock沿晚上3个CLKP的时钟周期,如下图中的红色框框所示,这个会导致很严重的timing vio,如下图所示:

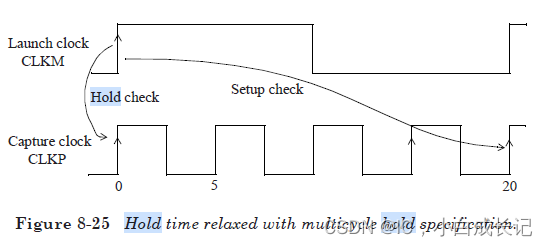

2.1.1.3 只设置同时设置setup和hold的 multicycle check

这样的timing vio不是我们所期望的。因为实际上期望的hold check是launch clock沿与capture clock沿保持一致有效的时候。因此,还需要对hold进行multicycle 设定。看如下命令所示,依然是-end,这个是指hold参考launch时钟沿,在setup check的第四个时钟沿基础上超前挪三个。加上工具自动挪的一个,这样hold检查的launch和capture沿就对齐了。如下图所示。设置完成下面命令以后,timing path相比较于上图,红框内的15就会变未0,slack就会变成-14.84+15=0.16。此处不再贴timing path 图。

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] –end

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] –end

2.1.2快到慢时钟的检查

上面讲解了慢到快时钟的timing check以及multicycle设定。其实快到慢是类似的。这个小节不会再详细展开。只会介绍一些不同点。

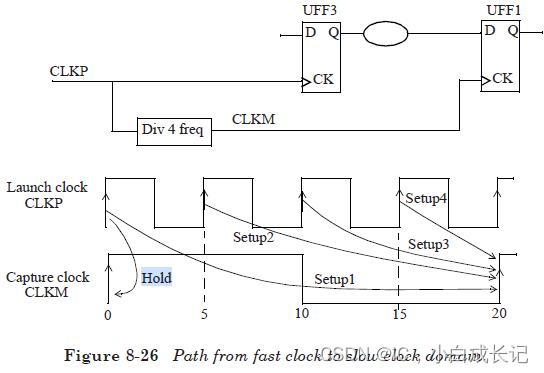

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

2.1.2.1. 如果不设置multicycle

这个时候,setup报告如图中所示,会找最紧的两个launch和capture沿进行check,即setup4这个检查。这个时候launch的其实时间是15,capture的起始时钟是20,依然是setup 检查需要满足5ns内完成。而此时的hold check是没有问题的,因为hold 检查沿相比较setup超前挪动了一个沿,此时的launch和capture是对齐的。

2.1.2.2. 只设置setup multicycle

如果只设置了setup multicycle 如下所示

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] –start

此时setup check的报告中,launch的起始点将会变成10,capture依然是20,这个时候setup检查需要在10ns内完成。

而如果没有设置hold,那么hold被工具自动相对与setup的captureclock移动一个start clock的周期,也就是在15ns处,这个时候hold check的launch clock沿为10ns,hold check的capture沿为15ns,存在5ns的差距,会导致vio出现。

2.1.2.3. 同时设置setup/hold multicycle

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] –start

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] –start

同时设置了,setup满足10个周期内检查没有问题。

对于hold,相对于setup的capture clock,向前移动一个start clock周期到了15ns,工具又自动移动一个start clock的周期到了10ns,这个时候hold check的launch和capture clock都是10ns,沿对齐了,这样timing check才不会有大问题。

7201

7201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?