ocv ,全称on chip varation,是用于signoff过程中为了弥补工艺制造过程中的不稳定情况的技术。

1. Overview

1.1 what is ocv?

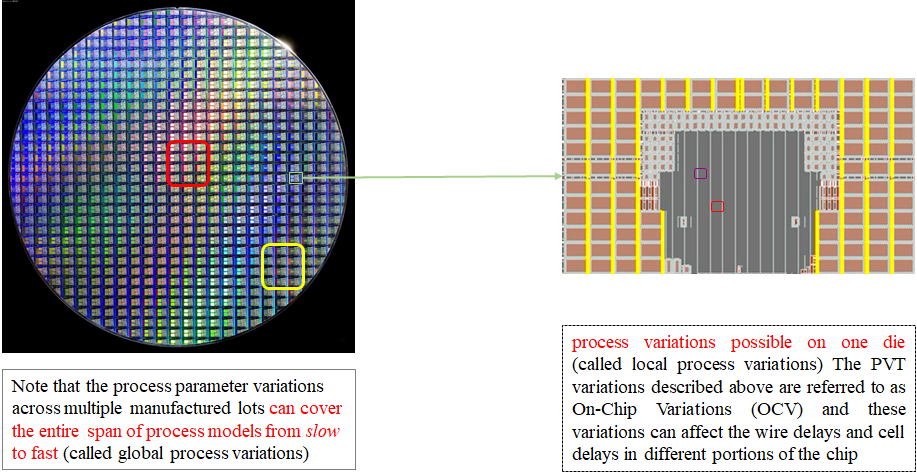

on chip varation,片上偏差。如下图左侧wafer上面的红色/黄色/绿色框框所示,虽然再同一片wafer上,但是因为位于不同的区域,因此在制造过程中总会有这样那样的差别,比如机器没控制好,红框沉积量要比黄框大一个百分比,比如绿框刻蚀的时候稍微严重了一些,等等情况导致wafer上的所有的die不尽相同。我们称之为varation。右侧图所示为一个die的放大图,variation在芯片上的影响就是对cell 和net真实delay的影响,那这个就会导致我们真实的std cell相关delay和foundry提供的标准单元库的相关delay有偏差,可能造成芯片的fail。为了cover这种variation,我们在STA signoff时候引入了OCV的技术,使得我们的signoff更加严格,从而影响工艺制造过程中的影响。一个技术,即使再先进,也是会有误差的。尤其是工艺从百ns级别到ns级别,些许的误差对于制造效果来说都影响巨大。

1.2 OCV. Effect on signoff

上面提到,varation会对timig signoff产生影响,具体如何影响的详细介绍如下:

1. Nomal mode timing signoff(不考虑ocv)

如上图所示为不考虑ocv情况下的timing signoff ,这时候进行setup timing check,如果满足途中的公式,我们就认为时序是没有问题的。

2. OCV mode timing signoff

当我们考虑了实际的制造过程,那么会出现如下的情况,如下图所示存在与launch line上的cell可能就比我们拿到的std cell的delay值要大一些,而存在与capture line的std cell的delay值要比std cell的小一些。

如果我们把varation有具体的数值表示:增加lauch clk delay和data line delay △1,减少capture clk delay △2,那么重新作用到setup的计算公式上如下图所示,可以看到这两个△的加入是有可能导致我们这个不等式不成立的,也就是说真实的工作时候,可能是不满足setup timing 检查的,就有可能导致芯片的fail。

1.3 How to remove the effects of ocv

上面1.2介绍了ocv对signoff的影响,那么如何消除这个影响呢?可以通过增加margin的方式,其实和uncertainty非常相似,就是通过把我们的check变得更加严格,从而来消除这种影响。ocv的消除方法是通过设置derate值。比如:对于launch clock,加上一个统一的大于1的derate值,就会在timing report中反映出来,相应的delay也会在原始值的基础上乘以这个derate值,相当于增大了launch line的delay,而对于capture clock line,相应地就会加上一个小于1的derate来计算delay,从而减小launch line的delay。通过这样的方法来让时序约束更加悲观,以此来覆盖生产中和实际应用中的各种variation。那需不需要考虑减小launch line,增大capture line的情况呢?对于setup肯定是不需要的,但是对于hold是需要的。接下来将会详细介绍derate设定的情况。

2. OCV applied and results

2.1 ocv applied

具体的ocv的实现方法以及效果是如何的呢,这个小部分展开讨论一下。

对launch, capture和data line上的cell或者net加一个固定的derate数值,使得setup和hold等时序约束比理想状况更加悲观从而能够覆盖部分实际生产中所产生的variation。如上图所示,针对于setup check,所有的launch path设置derate为1.1,所有的capture path 的derate值设置为0.9。我们在做hold check时候,那么就会和setup时候恰恰相反,launch path设置derate为0.9,所有的capture path 的derate值设置为1.1

如何实现这个设置呢,可以通过在sdc中增加如下命令的方式:

set_timing_derate -early 0.9

set_timing_derate -late 1.1

当设置这两个derate时候,-early表明我们期望最短的path,也就是期望最严格的检查,那么在setup时候,当然capture path越短越严格,同理,hold的时候launch path 越短越严格。-late恰恰相反。除此之外,关于set_timing_derate的命令还有很多的写法如下所示,-data/clock表示这个derate作用于clock path还是data path,cell delay/net delay表示作用于cell还是net:

set_timing_derate -early 0.9 –clock/data

set_timing_derate -net_delay/cell delay -late 1.1

set_timing_derate -cell_delay -early 0.9

2.2 timing report

如下图示例很清晰的讲解了derate如何作用于timing signoff的情况。图中所示标识了common clock path delay为1.2ns,launch clock delay为0.8ns,data path为5.2ns,capture clock delay为0.86ns,Tsetup为0.35ns

当我们设定如下图所示的derate后,那么刚刚描述的内容会发生变化

此时的launch path长度:(5.2+0.8+1.2)1.2 = 8.64

此时的capture path长度:(1.2+0.86)0.9 + 0.351.1 = 2.239

那么如果想要setup 满足,最小的时钟周期为T = 8.64 - 2.239 = 6.401

而因为common path有1.2ns的公共部分,过于悲观,去掉这一部分,这个过程叫做CRPR,去除悲观度。

那么真实的可以达到的最小时钟周期T = 6.401 - 1.2(1.2-0.9) = 6.041.

而真实的derate值在timing 报告中应该是如下图所示:

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?