电子行业始终遵循一条规则—如何以更快、更准确的方式传输数据。半导体集成器件通过将大量元件集成到单个Si芯片上,已基本实现了这一目标。近半个世纪以来,仅靠摩尔定律(本质上是每一年半处理能力翻倍)就足以保持器件成本竞争力,同时提升芯片密度和性能。晶体管尺寸的微缩在保持功率密度恒定的同时提高了速度,但这种微缩趋势已因栅极氧化层厚度达到原子级、短沟道效应、互连RC限制等问题而放缓,导致功率密度随尺寸缩小而上升。尽管作者认为上述问题均可解决且摩尔定律仍将持续数年,但仍需为高速数据通信需求的增长做好替代方案准备。

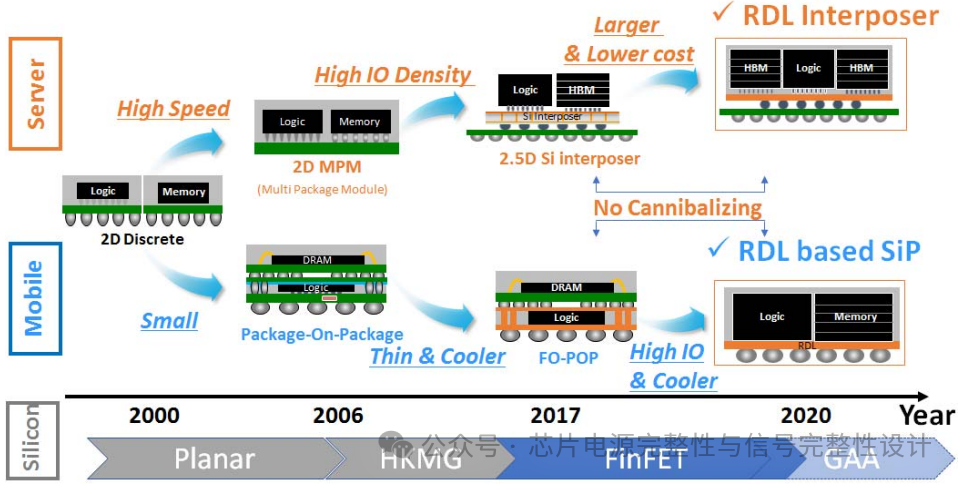

Si微缩技术为数据驱动型世界奠定了基础。过去二十多年中,Si基CMOS芯片能够满足市场对高性能逻辑(服务器应用)和低功耗逻辑(移动应用)的需求。截至2000年代初,服务器和移动应用的主流封装类型均为分立式封装(如图1所示)。2000年代中期,用户对计算能力和数据传输速度的要求大幅提升,但简单的封装类型难以满足需求。这些需求包括社交网络服务(SNS)、虚拟现实(VR)、增强现实(AR)、物联网(IoT)、云计算以及采用深度神经网络(DNN)或卷积神经网络(CNN)等复杂算法的人工智能(AI)。

为提升封装级集成密度,堆叠封装(POP)于1990年代被提出。POP的目标是通过小型化、薄型化封装实现功能集成,同时提升电气性能、设计灵活性和降低成本。利用底部封装逻辑芯片与顶部封装存储芯片之间的短互连优势,POP可轻松增加带宽。因此,三维(3D)集成(POP)在过去十年中从LPDDR1到LPDDR4x(见图1)的移动应用中证明了其价值,并将在动态功耗(即热耗散可控)受限时继续发挥作用。

图1:服务器与移动应用的封装技术演进,同时展示Si技术发展历程。

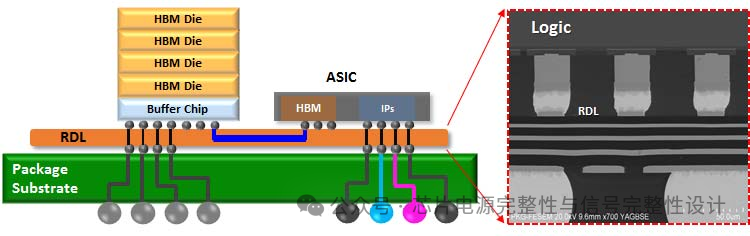

POP之后,interposer封装(支持行业标准内存焊球间距)和晶圆级封装相继出现。相比之下,服务器应用的封装平台变化较晚。尽管分立封装和模块封装仍用于CPU,但“数据密集型”和“计算密集型”趋势以及用户对高性能体验的需求,要求服务器和网络产品的封装平台进行根本性变革。在低功耗系统与高速I/O开发的限制下,带宽需求通过25DSiinterposer上的高带宽内存(HBM)增加I/O数量而非速度来满足。随着第二代HBM(HBM2)的问世,25DSiinterposer已可支持4-HBM集成。精细的导体线宽与间距设计规则对实现大型异构系统和非冯·诺依曼架构至关重要,而封装技术可在此领域贡献更多价值。基于这一理念,RDL技术平台被开发为更具成本效益、热耐受性或更小尺寸的解决方案。

常见的基于RDL技术平台包括FO-POP、FO-SIP、RDL interposer:

-Si interposer:适用于高端服务器

-FO-POP:适用于对尺寸敏感的移动应用

-FO-SIP:适用于对热性能敏感的智能设备

-RDL interposer:适用于高带宽服务器应用

Si interposer与RDL interposer对比

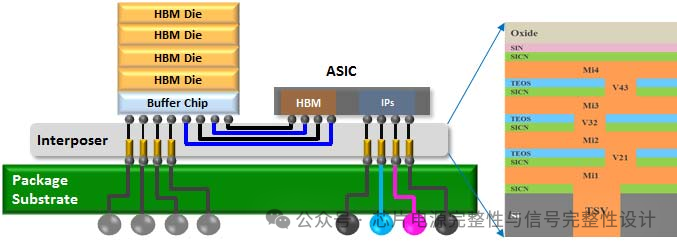

近年来已有大量关于Si interposer电气性能的文献。如图2所示,25DSiinterposer包含两个接口:(1)逻辑-HBM,(2)通过含TSV的Siinterposer连接逻辑与封装基板。以下问题会影响仿真结果,但据作者所知,尚未得到充分解决:

-需以薄膜形式测量介电层(TEOS、FTEOS、SiCN、SiN)的特性。

-损耗角正切值未知。

-Si interposer设计基于图形数据系统(GDS),与片外仿真工具不兼容,需将设计数据库转换为仿真工具可识别的格式,否则只能在仿真工具中绘制少数信号线而无法捕捉设计细节。

-电源完整性(PI)建模完全依赖片内工具(如StarRC)。

-窄信号线可能位于网状接地层上方或仅位于介电层上。

-TSV需用3D电磁工具单独精确建模。

图2:25D封装的垂直结构与interposer堆叠。

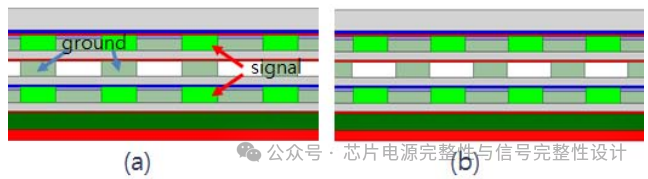

与封装基板不同,Si interposer只能在不降低良率的情况下制造网状平面。信号线宽可能窄于网状接地的间距,因此信号可能位于网状接地的上方或下方,也可能仅位于介电层上,未正确参考接地。这导致图3(a)与(b)中的眼图张开度存在差异。由于电容效应,图3(b)结果优于图3(a),眼图张开度在4、5、6mm长度时分别相差3%、4.4%和7%,且差距随线长增加而扩大。因此,设计阶段需考虑这些影响。

图3:信号上下不同Ground mesh形式

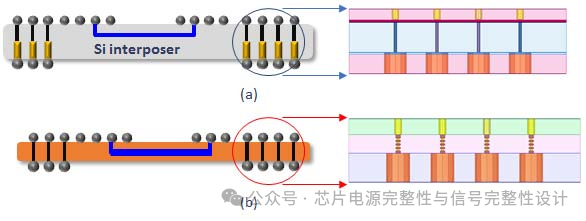

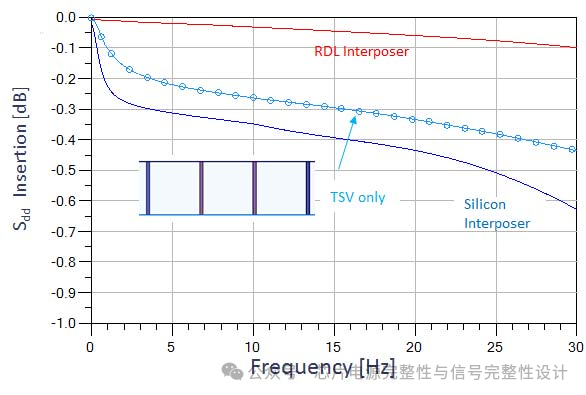

TSV需精确建模以捕捉通道电感效应,TSV被损耗性氧化Si包裹,因此Si interposer的信号损耗主要由TSV主导,与含TSV的Si interposer相比,RDL interposer的插入损耗略优(最大0.3dB),如图4和图5所示。所有仿真均采用Ansys HFSS对G(接地)-S(信号)-S-G差分结构进行。如前所述,仿真未基于GDS实际设计,而是直接在片外仿真工具中绘制少量TSV。因此,去除TSV不仅可降低成本,还能简化仿真难度。相反,RDL interposer基于封装设计工具设计,其电气建模与PCB封装类似。需注意,在IP设计阶段对齐微凸块(ubump)与TSV至C4焊球至关重要,否则需分别为interposer和非interposer设计两个IP模块。

图4:(a) Silicon interposer (b) TSV-less RDL interposer

图5:Sdd仿真结果:RDL interposer(上),TSV(中),带TSV Si interposer

扇出型堆叠封装(FO-POP)

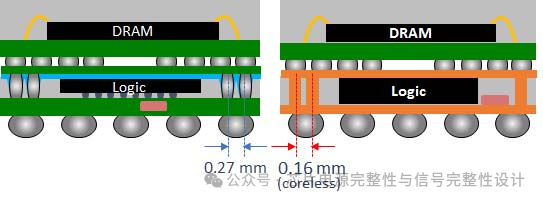

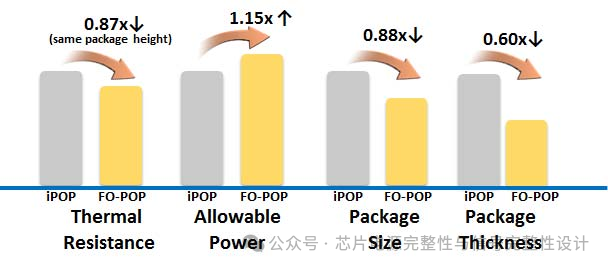

如图1和图6所示,该平台已开发完成并即将量产,以快速响应市场需求。薄型RDL替代了较厚的POP PCB基板,由此节省的高度用于增加芯片厚度,从而改善热性能(见图7)。此外,封装高度可减少40%,且外形尺寸(移动应用封装选型的首要因素)缩小12%。这得益于图6中节距的缩减,即在相同I/O数量和电路密度下,封装面积得以缩小。前端RDL的线宽、间距和厚度分别为7μm、7μm和5μm。

图6:传统POP(interposer POP)与FO-PLP结构对比

图7:FO-POP与传统iPOP的热性能与设计对比。

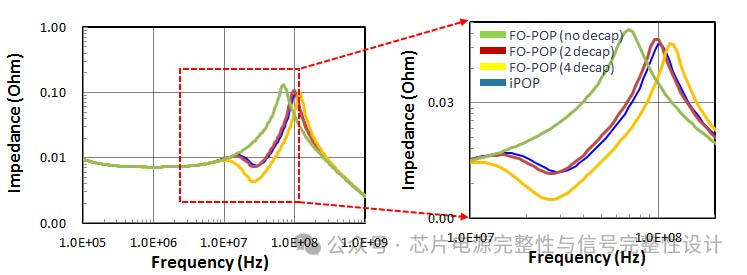

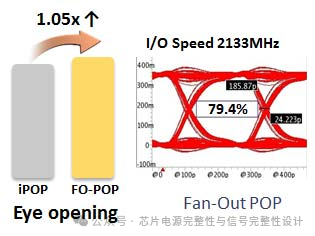

由于去除了PCB基板,嵌入式去耦电容需置于芯片侧(见图6)。当使用足够的嵌入式去耦电容时,FO-POP的阻抗可低于传统POP(interposer POP或iPOP)。图8展示了POP与FO-POP在多种去耦电容配置下的CPU电源分配网络(PDN)自阻抗曲线。图9对比了两者的电气性能(眼图张开度)。FO-POP的短互连设计可显著提升性能。

图8:POP与FO-POP的阻抗曲线对比

图9:iPOP与FO-POP的电气性能对比

扇出型系统级封装(FO-SIP)

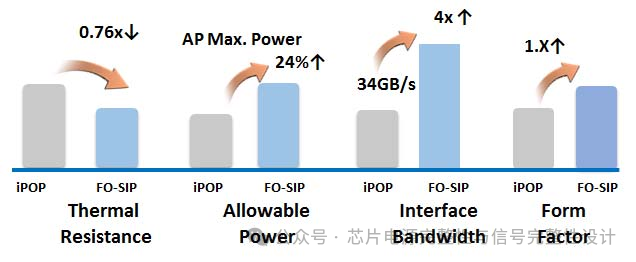

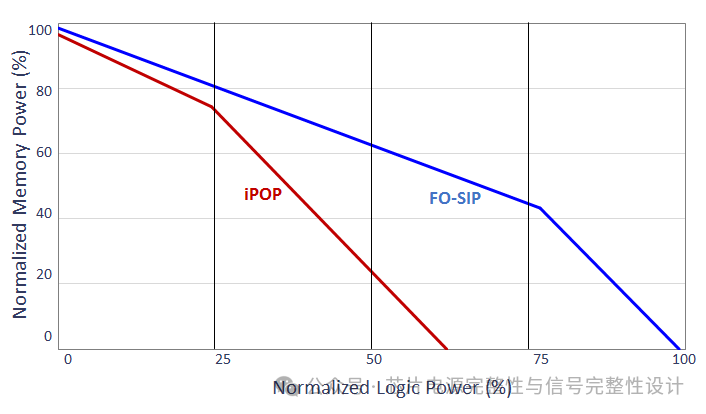

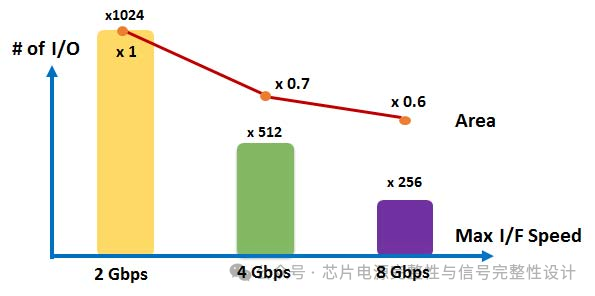

FO-SIP将逻辑与内存封装并排放置(亦称“FO-SIP并排封装”),使芯片厚度增加,从而有效解决热问题。如图12所示,FO-SIP可提供服务器或网络产品所需的高带宽,且封装尺寸增幅可控(假设需开发x256内存,封装尺寸增幅低于两倍)。

图12:iPOP和FO-SIP对比

A电气性能分析

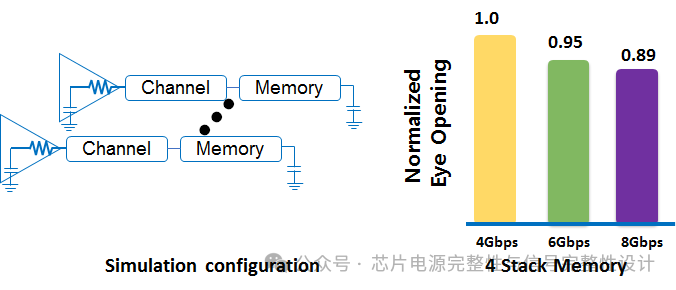

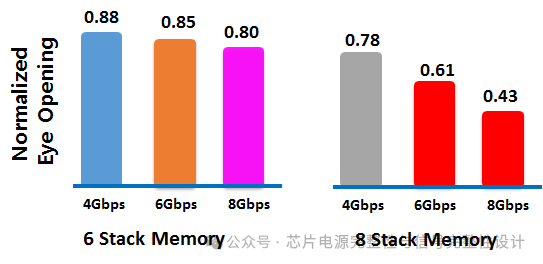

通过通道仿真验证FO-SIP平台。假设芯片间距约100μm,总线长约1mm,线宽/间距为5μm/5μm,并采用HBM2线性模型扩展至8Gbps。以±40mV为眼图掩模,仿真结果显示4栈和6栈内存性能达标,但8栈内存无法满足眼图要求(图13-14)。总体而言,FO-SIP的电气性能优于传统iPOP或FO-POP。

图13:4栈内存的FO-SIP仿真

图14:不同内存栈数的通道仿真

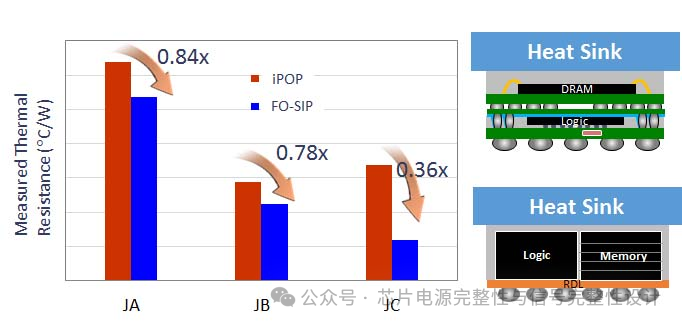

B热性能分析

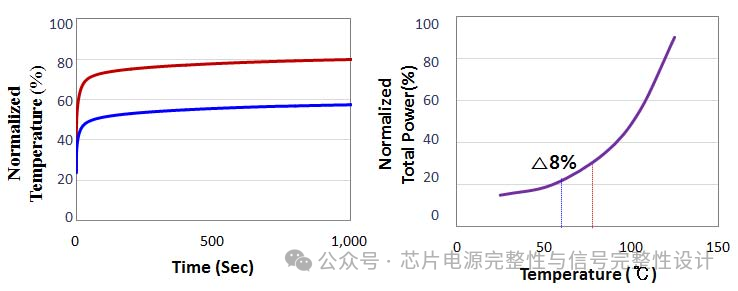

通过热测试载体(TTV)结果,稳态热实验表明,FO-SIP的结壳热阻(θJC)显著优于POP(图17)。瞬态分析显示,在施加4W功率时,FO-SIP达到允许最高温度的时间更长(图18)。此外,FO-SIP的漏电功耗较POP低8%,且热串扰(图19)验证了其热性能优势。

图17:POP与FO-SIP的热阻对比,包括结-环境(θJA)、结-板(θJB)和结-壳(θJC)

图18:系统级瞬态温度(左)与功耗增益(右)对比

图19:POP与FO-SIP的逻辑-内存热串扰对比

RDL interposer封装

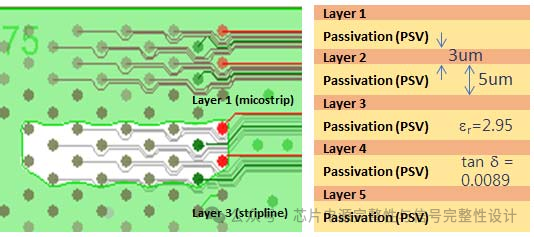

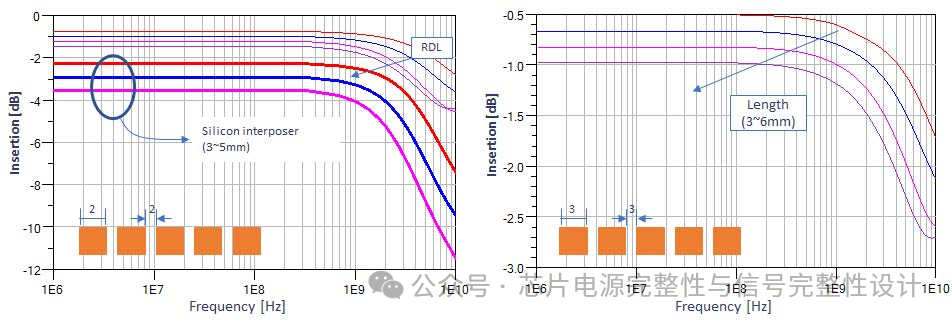

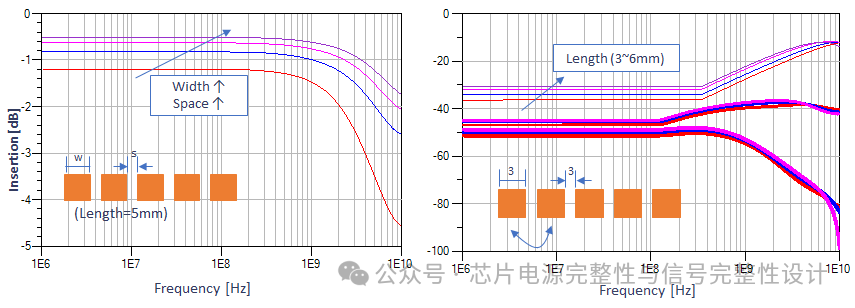

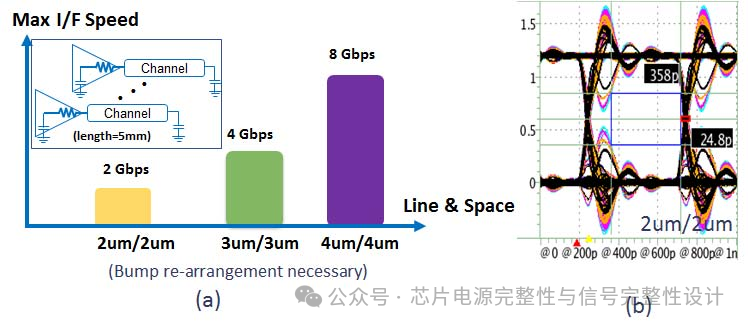

RDL interposer通过晶圆、面板或玻璃基工艺]替代2.5D Si interposer,并去除TSV(故称“无Si”RDL interposer),具有成本优势。晶圆级工艺可提供精细线宽/间距(<2μm/2μm),面板级工艺则通过更大面板尺寸实现更高生产率(线宽/间距为7μm/7μm~5μm/5μm)。图20展示了RDL interposer结构,图21为一个实际设计的叠层及设计,其导体厚度(3μm)远高于Si interposer(0.9μm),相同线宽/间距下直流电阻更低,插入损耗更优(图22,图23)。仿真表明,RDL interposer在5mm线长下支持的最高接口速度随线宽/间距变化(图24),且通过优化凸块布局可实现更高带宽(图25)。

图20:RDL interposer截面

图21:RDL interposer叠层设计

图22:2μm线宽/间距的插入损耗对比(左)与3μm线宽/间距的插入损耗(右)

图23:不同线宽/线距插入损耗和Crosstalk对比

图24:RDLinterposer在不同线宽/间距下的最高接口速度(a)与2μm/2μm配置的眼图张开度(b)

图25:接口速度与所需I/O数量及预估IP面积的关系

结论

本文介绍了三种基于RDL技术的封装(FO-PLP、FO-SIP、RDL interposer),分别适用于移动应用(尺寸敏感)、未来智能设备(热敏感)和服务器(高带宽)。FO-PLP满足移动设备小型化趋势;FO-SIP凭借热性能优势,为智能手机提供潜在的高密度内存支持;RDL interposer以设计灵活性、成本优势和电气性能媲美2.5D Si interposer,成为高性能计算产品的理想选择。这些平台尚处发展初期,但将在第四次工业革命中引领封装行业。

3434

3434

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?