紧接上篇文章 【ARM Cortex-M 系列 2.1 – Cortex-M7 Debug system registers】

单步调试概述

在ARMv7-M架构中,通过使用单步调试(Halting Debug Stepping),调试器能够从调试状态退出,执行单条指令,然后重新进入调试状态。这是一种在精确调试软件时十分有用的功能,它允许开发者逐条检查指令的执行情况。单步调试是在以下所有条件满足时激活的:

单步执行原理

DHCSR.C_DEBUGEN被设置为1,使能 debug state。DHCSR.C_STEP被设置为1,使能单步调试。- 处理器处于非调试状态。

当处理器退出调试状态并且单步调试变为活动状态时,处理器将按照如下方式执行一个单步调试:

- 执行以下操作之一:

- 执行下一条指令,不生成任何异常。

- 接受任何待处理的足够优先级的异常入口。

- 执行下一条指令,生成一个同步异常,并接受该异常。

- 将

DFSR.HALTED位设置为1。 - 返回到调试状态。

调试器还可以选择性地将 DHCSR.C_MASKINTS 位设置为1,以防止PendSV、SysTick和外部可配置中断被接受。当 DHCSR.C_MASKINTS 被设置为1时,如果允许的异常变为活动状态,处理器将会在执行关联的异常处理程序的第一条指令之前停滞并进入单步调试。

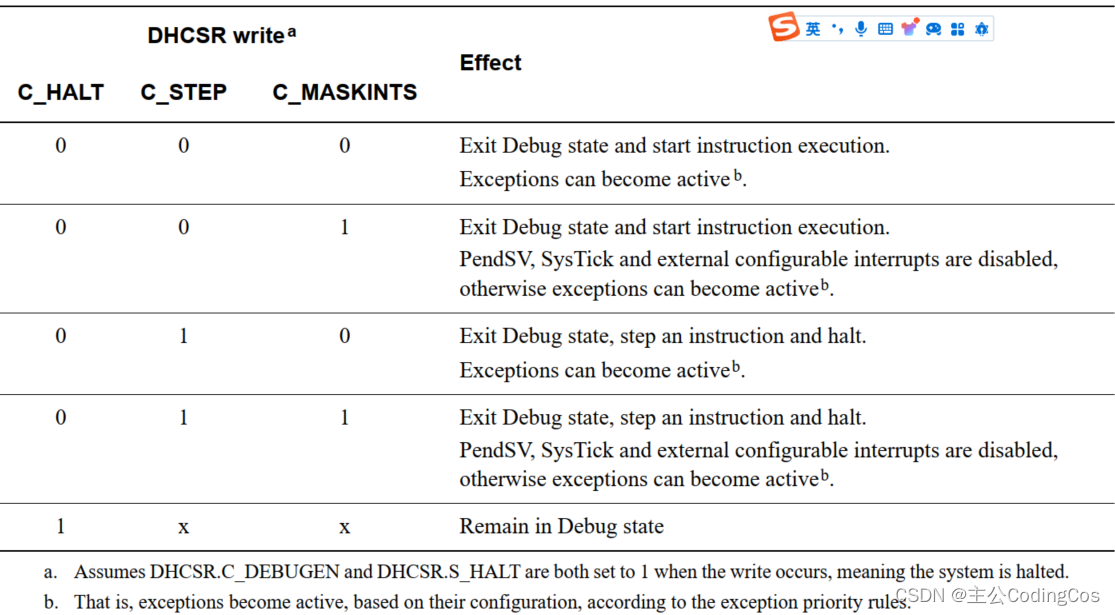

此外,DHCSR.{C_HALT, C_STEP, C_MASKINTS} 可以通过对 DHCSR 的单次写入来设置。这意味着,通过一个操作即可同时配置多个调试相关的控制位,从而为调试提供更大的灵活性和控制力。

在看了上述描述外,好像还是不清楚单步调试时怎么进行的?

简单来说可以按照下面步骤进行:

-

调试器设置

DHCSR.C_DEBUGEN和C_HALT位来暂停内核。 读取DHCSR.S_HALT判断是否处于debug state。 -

将

C_STEP位设置为 1来使能单步执行,然后将C_HALT位设置为0内核离开 debug state,内核可以单步执行, 然后再进入停止状态。具体可以从下表可以看到当 C_HALT 为 0, C_STEP 为 1 的时候就是这种情况。

Debug stepping control using the DHCSR

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?