片外互连延迟不断增长的问题解决方案出现了系统级芯片(System-on-Chip, SoC)。把所有的元器件集成到单片衬底上可以提升系统的总体速度,同时也降低了功耗。

基于芯片堆叠式的3D技术

3D IC的初期形态,目前仍广泛应用于SiP领域,是将功能相同的裸芯片从下至上堆在一起形成3D堆叠,再由两侧的键合线连接,最后以系统级封装SiP的外观呈现。堆叠的方式可为金字塔形、悬臂形、并排堆叠形等多种方式。

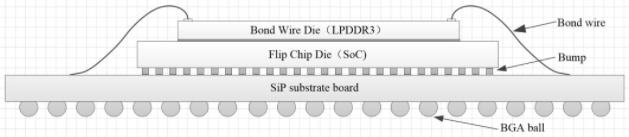

另一种常见的方式是将一颗倒装焊(flip-chip)裸芯片安装在SiP基板上,另外一颗裸芯片以键合的方式安装在其上方,如下图所示,这种3D解决方案在手机中比较常用。

基于无源TSV的3D技术

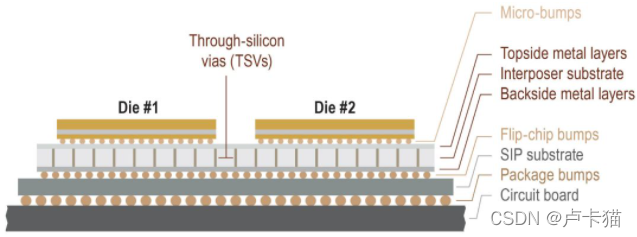

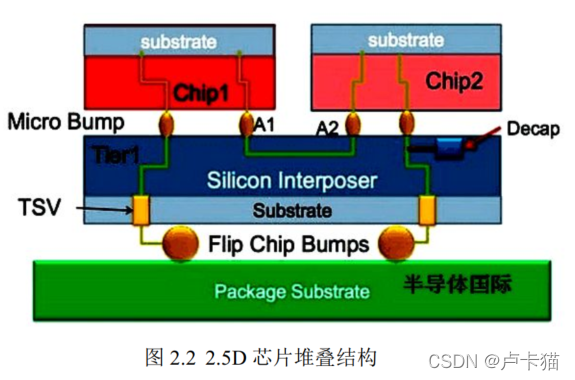

在SiP基板与裸芯片之间放置一个中介层(interposer)硅基板,中介层具备硅通孔(TSV),通过TSV连结硅基板上方与下方表面的金属层。有人将这种技术称为2.5D,因为作为中介层的硅基板是无源被动元件,TSV硅通孔并没有打在芯片本身上。如下图所示

基于有源TSV的3D技术:

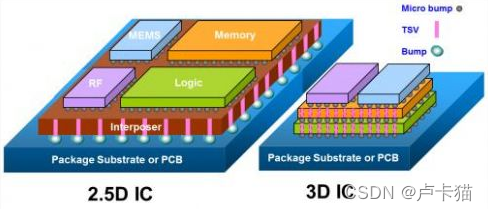

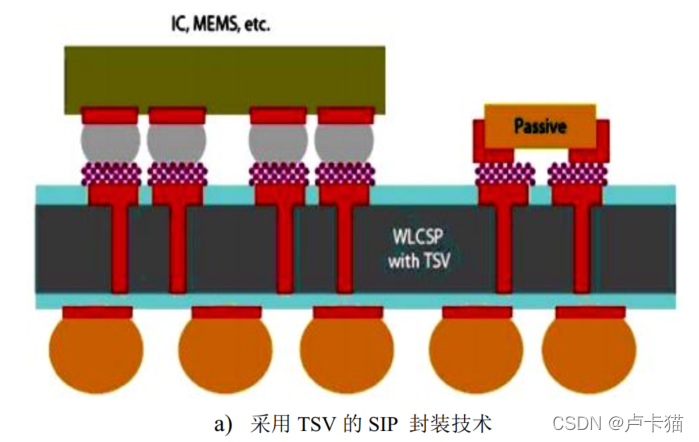

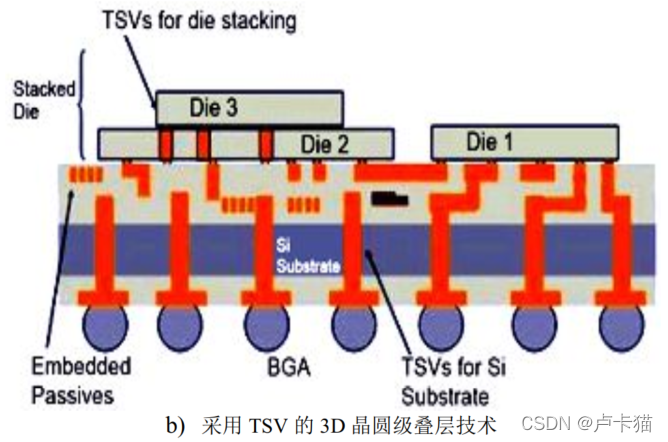

在这种3D集成技术中,至少有一颗裸芯片与另一颗裸芯片叠放在一起,下方的那颗裸芯片是采用TSV技术,通过TSV让上方的裸芯片与下方裸芯片、SiP基板通讯。如下图所示

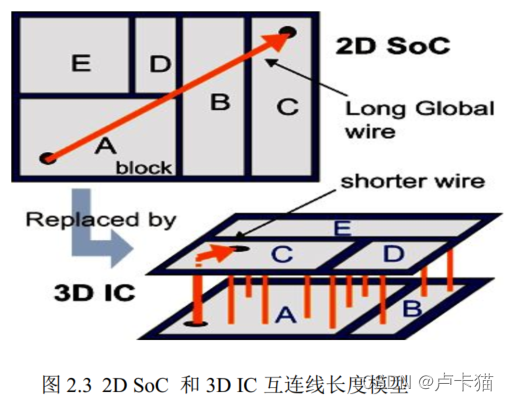

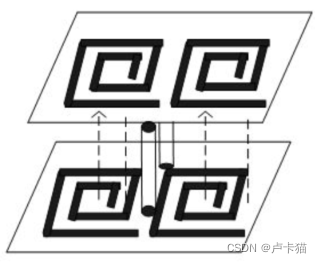

3D IC实质在于可以让集成电路上最长的互连线长度大大缩减,在下图可以看出,在二维平面中,连接A区和C区的信号线会横跨整个平面,而在三维继承中,则通过把A区和C区布局规划在两个die之间通过TSV来互连,将大大缩短互连线的距离。

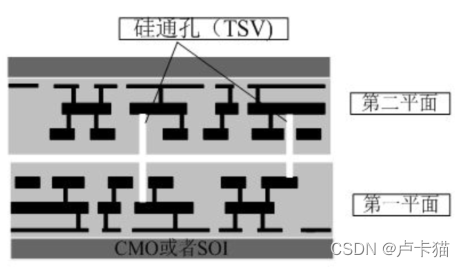

目前部门厂商开发出TSV(Through silicon via)硅穿孔,除了普通的互连线之外,TSV在层间互连也起到万分重要的作用,它是连接两层芯片的唯一通道,不仅作为信号通道、时钟通道,并且是重要的电源通道。

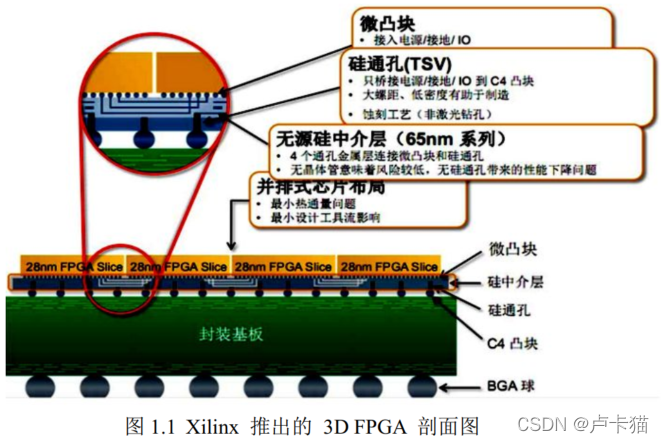

赛灵思提出堆叠硅片互连(SSI)3D IC架构,SSI技术利用无源65nm硅中介层上的与大节距硅通孔(TSV)技术整合在一起的微凸块(Bump)技术。

系统级封装(SIP)和3D IC的工艺是两种主要三维电路集成方法,一般人们对二者容易混淆。SIP和3D IC间的区分标准在于3D系统的不同平面上电路之间通信互连所使用的工艺技术。在SIP中采用高深宽比的硅通孔,由于通孔的尺寸是长而宽的低密度垂直互连,决定其无法达到很高的垂直互连密度,提供粗精度的互连。另一种方案由窄而短的TSV为3D IC中不同平面之间的器件提供精细的互连。

虽然3D IC可以描述为SIP的一个子集,但与SIP所用的互连机制相比,3D垂直互连的优势更为显著。

3D 系统可以视为一个单片结构,3D IC可以通过多个晶圆或者裸的管芯的键合来形成。SIP和3D IC之间的显著区别在于垂直互连结构的不同。

3D IC中不同管芯之间通信的实现方式如下:

1.高密度的短而细的TSV,设置在横跨管芯未被晶体管占据的任何一点

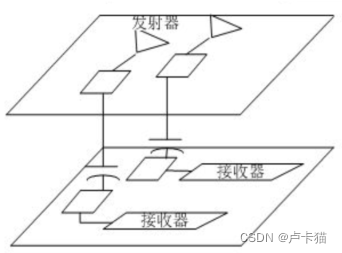

2.垂直方向相邻管芯上平行的金属平面间的电容耦合

3.垂直方向相邻管芯上各电感间的电感耦合

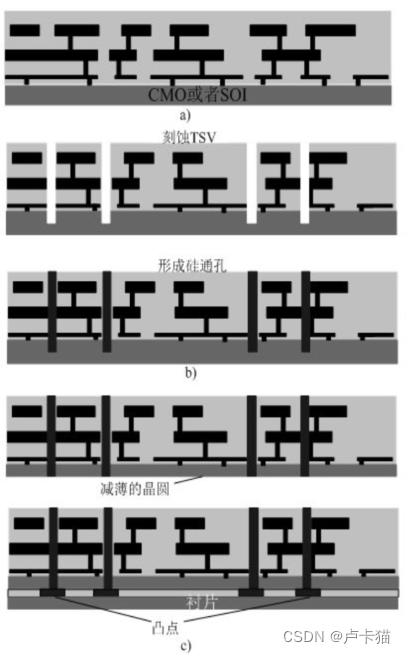

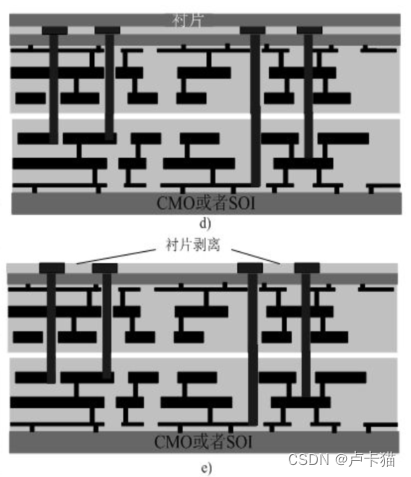

制作过程:

制作深槽使之穿过平面间介质(ILD)、金属和器件层,钝化深槽侧壁使之与金属层和导电衬底(对于 CMOS 电路)绝缘,然后用导电材料填充深槽,在 3D 系统的平面问形成电连接。

在平面堆叠前,通常将晶圆减薄以减小3D系统的整体高度和平面间过孔的长度。但是这导致减薄后的晶圆不能承受转移和键合等3D加工的机械应力。所以需要在减薄前将衬片粘到晶圆上。

晶圆准备->TSV刻蚀->晶圆减薄->制造凸点->衬片粘合->晶圆键合->去除衬片

参考文献:

基于OC8051芯片处理器的3D IC布局布线设计——李琨(西安电子科技大学)

https://www.sohu.com/a/373749548_132567

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?