什么是虚拟输入输出调试?

FPGA虚拟输入输出调试工具是一个可定制的IP核,它可用于实时监视和驱动内部FPGA的信号。

在FPGA设计和调试过程中起着重要的作用,它可以帮助设计人员快速验证设计的正确性和性能,并加快设计的迭代和优化过程。同时,它也可以减少硬件资源的占用和开发时间的消耗,提高整个系统开发的效率。

可以定制输入和输出端口的数量与宽度,用于和FPGA设计进行连接。由于IP核与被监视和驱动的设计同步,因此应用于设计的时钟约束也适用于IP核内的元件。

不同FPGA的方案

xilinx 叫虚拟输入输出(Virtual Input Output,VIO)核。

altera中类似的工具为In-System Sources and Probes Editor(ISSP)

本文主要介绍In-System Sources and Probes Editor(ISSP)的使用。

使用步骤

本说明基于quartus21版本。

1 建立FPGA工程,导入V文件。

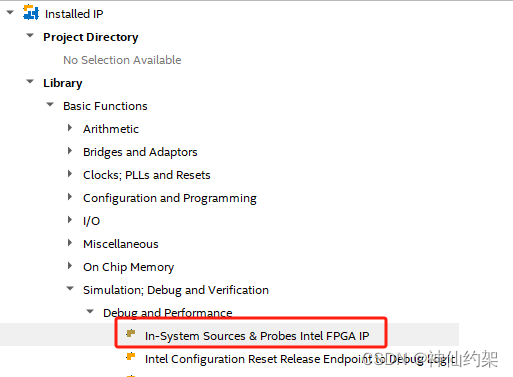

2 在tools->IP Catalog->Library中双击选择In-System Sources and Probes Intel FPGA IP

3 进入New IP Variant,新建ISSP IP,命名为issp1(可以根据需求命名)

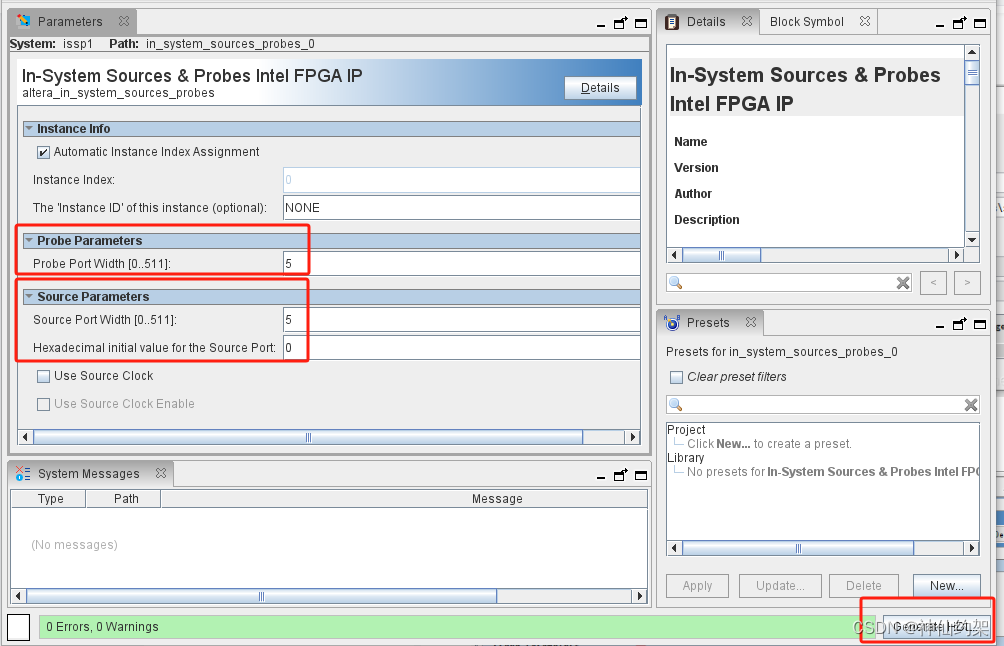

4 修改probe 和 source的参数值,可设置最宽512bit,本例设置值都为5,点击Generate HDL

5 点击Generate -> show Instantiation Template,产生Example HDL,点击Copy

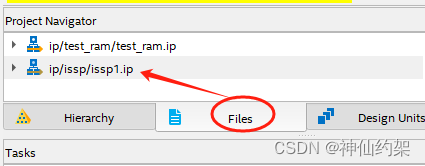

6 之后可在Project Navigate Files页看到新建的issp1.ip

7 把复制的example粘贴到工程V文件中

source为需要外部输入控制的寄存器

probe为需要抓取输出的寄存器

8 编译FPGA工程,生成下载文件。

9 菜单选择Tools -> In-System Sources and Probes Editor,打开In-System Sources and Probes Editor工具

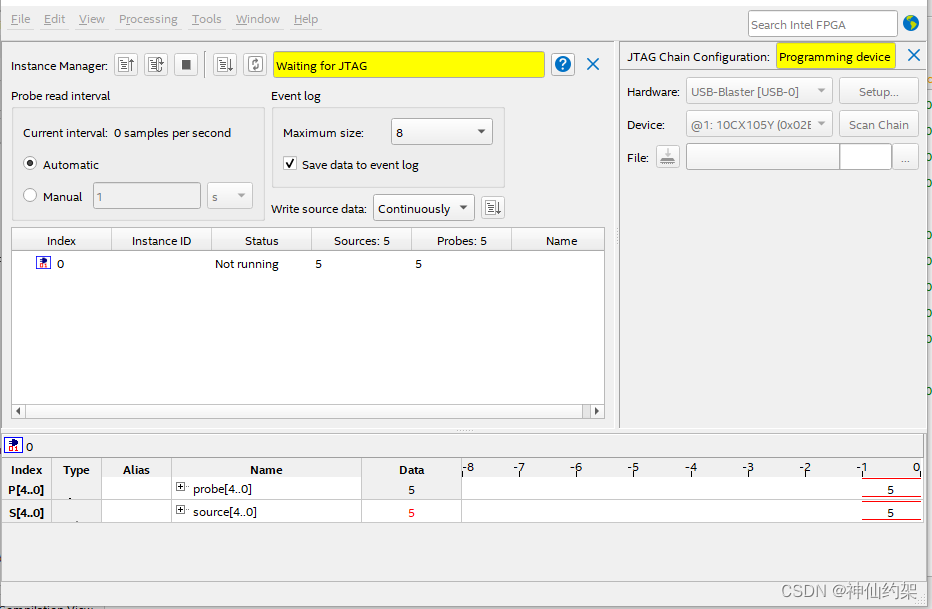

10 右侧JTAG选择对应的Hardware和Device,选中生成的sof文件,点击下载按钮

11 下载完成后,会自动载入生成的In-System Sources and Probes Editor信号

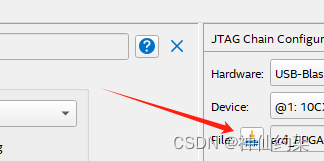

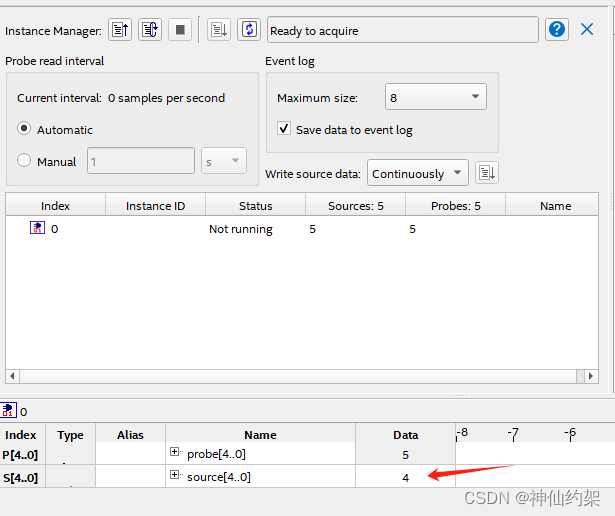

点击source的Data,键入想写入的寄存器值,这里设置为4,点击键盘 回车 确认输入。

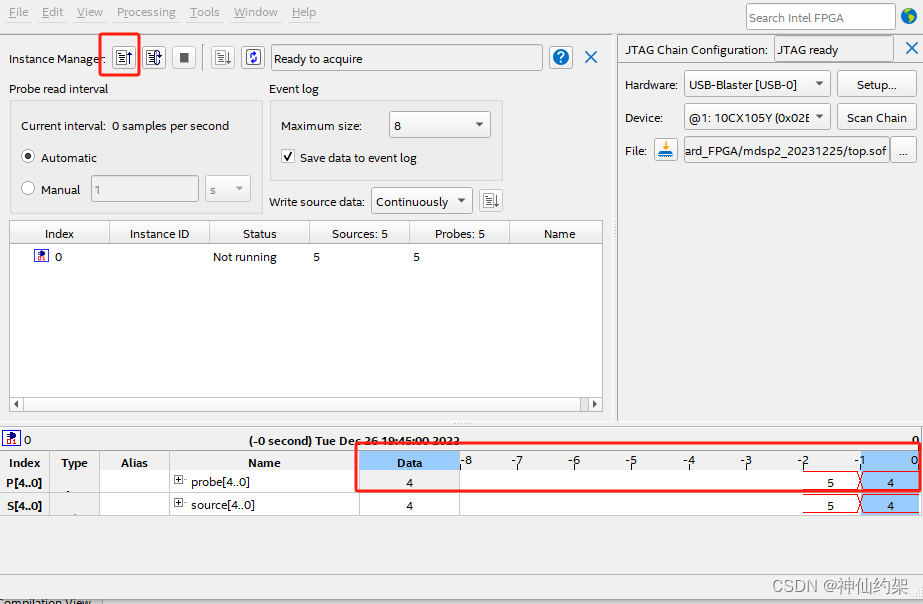

12 注意到,probe的Data仍为上次读出的5,点击instance manager -> read probe data按钮,可见data数据变化为4

至此,ISSP的使用介绍完毕,有需要的朋友欢迎收藏转发。

1399

1399

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?