一、ISSP IP概要:

ISSP:In-System Sources & Probes Intel FPGA IP

作用:

- 分为In-System Sources与In-System Probes

- n-System Sources,输入端,等价于拨码开关,通过输入板载FPGA上的拨码开关状态改变FPGA内部功能

- In-System Probes,输出端,等价于LED灯仔,通常通过肉眼观察LED亮灭判断程序运行状态,如果没有设计板载LED邓状态,可以通过Quartus的In-System Probes读取

- 目前工程里用的最多的是Sources,即作为输入使用

- ISSP等价于没有实际IO pin引脚的FPGA的IO口

普通的IO口有具体的引脚输出,可以使用LED灯仔或者示波器抓取输入/输出信号,但是ISSP只能通过Quartus的软件在线查看;

二、创建ISSP IP

2.1 添加ISSP IP

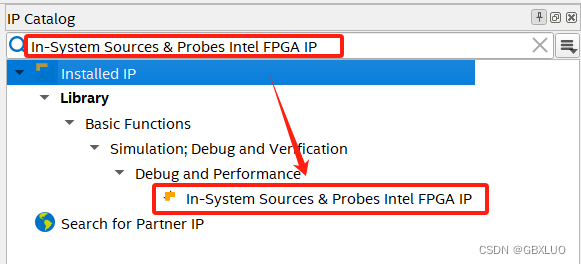

在IP Catalog的搜索框输入:In-System Sources & Probes Intel FPGA IP并双击即可打开

本文介绍了IntelFPGA的In-SystemSources(输入)和Probes(输出)功能,包括如何在Quartus中添加、配置这些IP,以及如何在工程中实例化和使用它们进行FPGA的调试。重点讲解了设置步骤和使用方法,包括编译、下载到FPGA和通过USB-Blaster进行通信的过程。

本文介绍了IntelFPGA的In-SystemSources(输入)和Probes(输出)功能,包括如何在Quartus中添加、配置这些IP,以及如何在工程中实例化和使用它们进行FPGA的调试。重点讲解了设置步骤和使用方法,包括编译、下载到FPGA和通过USB-Blaster进行通信的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1747

1747

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?