参考:

Burst(突发)信号详解_yuzhong_沐阳的博客-CSDN博客_burst传输

Burst传输_Phenixyf的博客-CSDN博客_burst传输

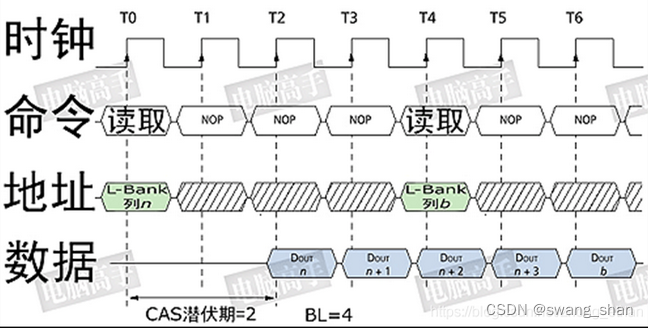

Burst是指在同一行中相邻的存储单元连续进行数据传输的方式。连续传输所涉及到存储单元(列)的数量就是突发长度,简称BL(burst length)。

Burst实质就是一次传输过程中,只发送一次地址,提高了传输效率。很多传输如AHB总线,发送每个数据都要对应发送其地址。两者区别请看下两图:

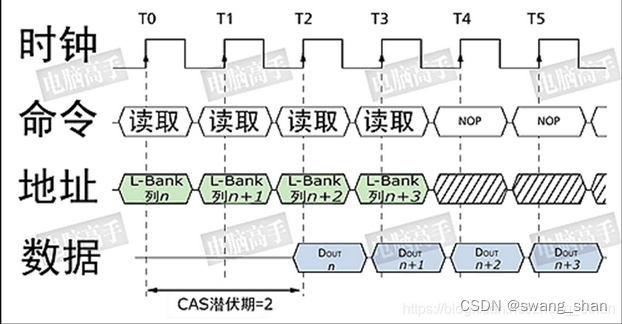

非突发连续读取模式:不采用突发传输而是依次单独寻址,此时可等效于BL=1,虽然可以让数据是连续的传输,但每次都要发送列地址与命令信息,控制资源占用极大。

突发连续读取模式:只要指定起始列地址与突发长度,寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输。

806

806

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?