众所周知,电信号在分布良好的导线上传输速度约等于光速。在实际的板级布线中,稍微长些的布线,系统延时可能会达到ns级别。ns级别的延时对于低速的系统中随不值一提,但在高速门电路、FPAG等高速系统中,这个数量级的延时就不可被忽略了。当然,对于高速系统中,走线上的延时仅仅只是其中之一。例如,高速PCB设计中还需考虑信号的开始端阻抗与终端阻抗不匹配,将会出现电磁波的反射现象。它会使信号失真,产生有害的干扰脉冲,影响系统运行。因此,在设计高速PCB时,信号延时的问题需要考虑,EMI/EMC等问题也需要考虑。

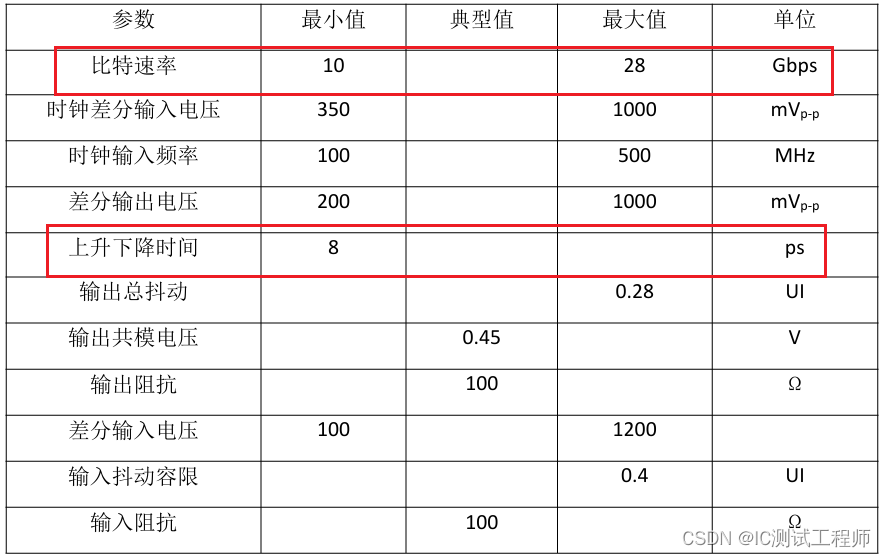

目前绝大部分的PCB设计人员经常根据感觉来进行PCB设计,而不是使用适当的方法和规则。而高速的模拟/数字电路设计不可能凭感觉设计出可靠的电路。还有现在大部分PCB设计人员搞不清晰哪些属于高速信号,这个高速信号不是单一依靠频率进行定义的,上升下降时间等AC参数也是关键。通常,通过元器件的数据手册可以查出对应信号的上升下降时间典型值。而在PCB设计中,实际布线长度决定了信号的传播时间。如果过孔多、拓扑结构不合理都将导致延时增大。一般情况下,高速逻辑器件的信号上升时间大都在200ps以下。Serdes接口参数规范如下图:

以上升时间举例子,确定某个信号是否需要考虑进行高速PCB设计方法:

以T_rise表示信号的上升时间,T_delay表示信号线的传播延时

若T_rise大于4倍的T_delay,信号落在安全区域;

若T_rise大于2倍的T_delay且小于4倍的T_delay,信号落在不确定区域;

若T_rise小于2倍的T_delay,信号落在问题区域;

当信号落在不确定区域和问题区域时应该使用高速布线方法进行PCB设计。

7116

7116

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?