最近控制过程中,被下三桥采样小坑了一下。

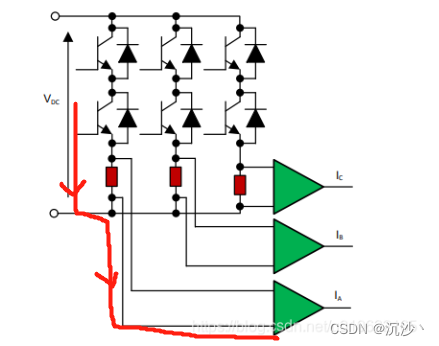

如下图所示为下桥臂三电阻采样方式,该方法的采样器件是高精度电阻,电阻两端电压经过采样调理电路输出至单片机ADC,三电阻采样成本低、结构简单,并且采样信号和输出强电之间是共地的,所以也不需要特地添加隔离电路。但是该方法也存在一定的劣势。

缺点:仅支持在对应下桥臂开通的时候进行电流采样。不采取补偿措施时,采样窗口必须满足一定宽度。

首先回答问题一:为什么只能在下桥臂开通时采样?

例如上图所示的A相,A相采样电阻仅在下桥臂开关管导通的时候才有电流流过,只有这个时候才能对A相进行电流采样。

其次回答问题二:什么是采样窗口?

采样窗口是电压矢量000作用的时间段。

按照三相逆变器的电压矢量分配表,开关矢量的定义如下:

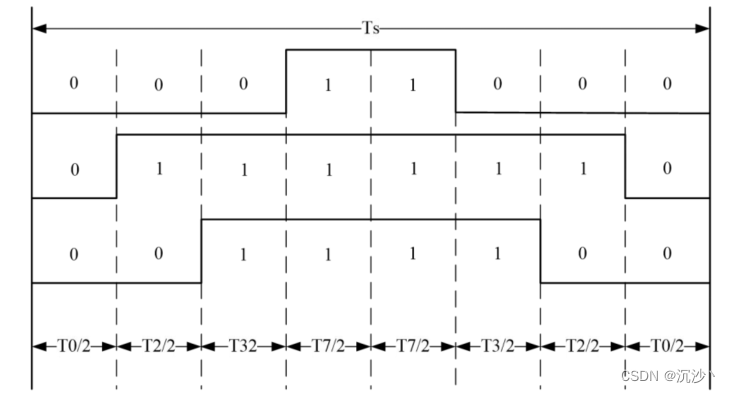

当上桥臂导通下桥臂关断时,开关状态为1;当上桥臂关断下桥臂导通时,开关状态为0。因此只能在对应相开关状态为0时进行采样才能采样到该相电流。三相电流采样需要同步进行,最终只能在电压矢量组合为000时进行采样。下图为一个载波周期七段式SVPWM图,调制周期的中心可进行电流采样。

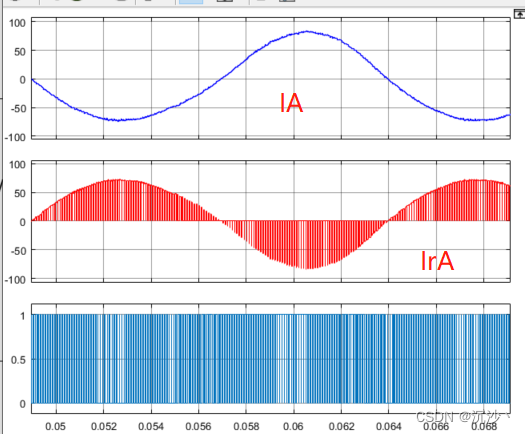

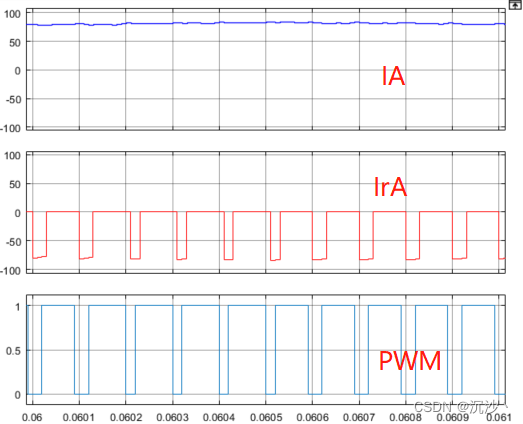

做个仿真试一下,如下图所示,三电阻采样的实际相电流是IA,IrA为采样电阻电流,最下面一排波形为PWM。

假如将其放大,如下图所示,PWM为0时,IrA才有值。

再来回答问题三:采样窗口最低为多少?

采样窗口即为000矢量最小持续时间,满足以下关系式:

T最小矢量持续时间 = T死区时间 + T开通关断延迟时间 + T芯片ADC转化时间

死区时间一般为1-5us,T开通关断延迟约为1-2us,芯片转换延迟时间约为3-6us,

以MOS为例,当驱动芯片为STM32F405时,死区时间为 2us,开通关断延迟 1us,ADC转换时间3us,全部合在一起是6us。因此窗口必须保证大于等于6us,设置为大概8us较为合适。

最后回答问题四:采样窗口固定的危害是什么?

假如一个控制系统的载波频率是10k,此时一个载波周期为 100us,若必须保持8us的采样窗口,则最大占空比只有 100 - 8 / 100 = 92%,从而导致电压利用率低。

电机的输出电压最大值决定了电机最高能跑多高速,这个电压利用率肯定是不高的。

强行去提速,当中间零矢量持续时间不足时,采样所得电流均为噪声,影响控制性能,严重的将导致电机失控。

小结:

1、A相采样电阻仅在下桥臂开关管导通的时候才有电流流过,只有这个时候才能对A相进行电流采样。

2、采样窗口是电压矢量000作用的时间段。

3、采样窗口最小时间 = T最小零矢量持续时间 = T死区时间 + T开通关断延迟时间 + T芯片ADC转化时间。

4、限制电压利用率低,无法跑到高速区。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?