一、buffer长时钟树

buffer 与 inverter 区别

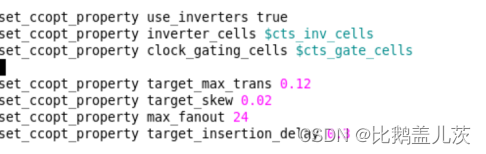

二、ccopt property

可加入floating pin (命令 insertion_delay)

三、NDR规则 和 摆放规则

![]()

用5-8层clock绕线,并w2s2

为了给filler cell 留空间,gap2

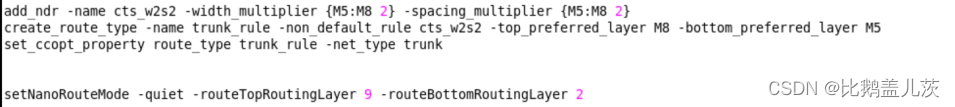

四、创建clock spec文档

![]()

五、ccopt_design -cts

六、报告查看与分析

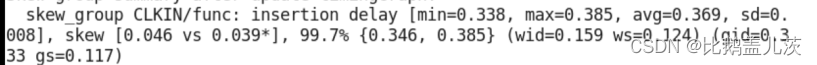

1.log

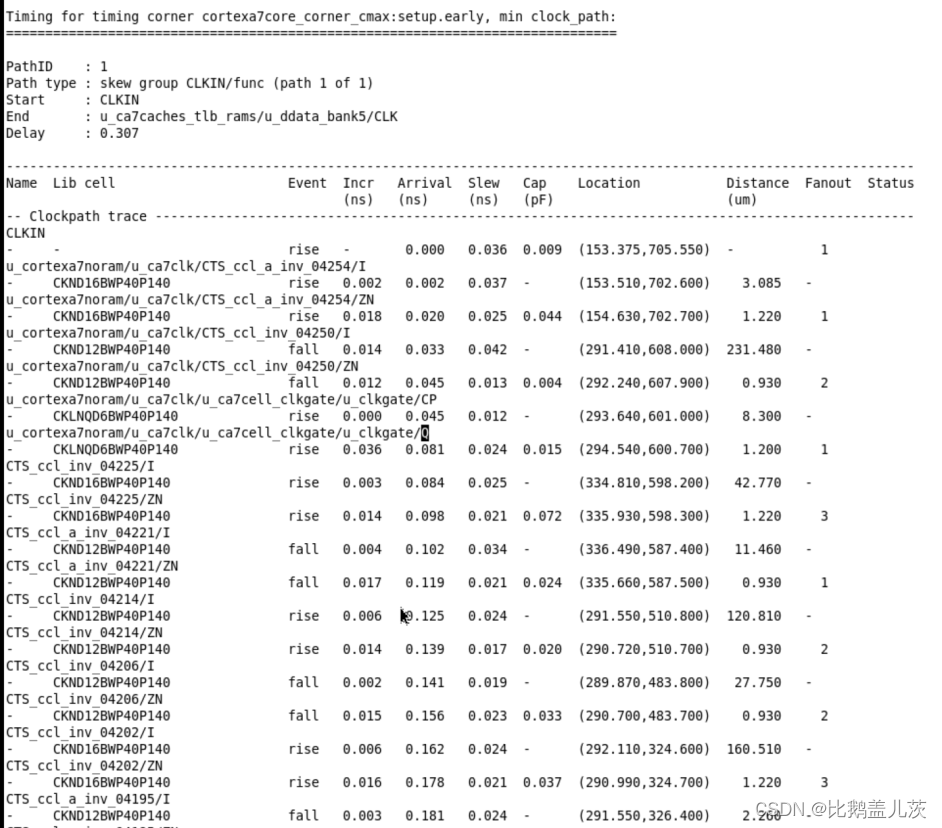

这里target skew为0.039ns ,是工具根据后面0.385--0.346=0.039自动设定的,这个区间占比99.7%

tree的平均长度369ps , skew 为46ps

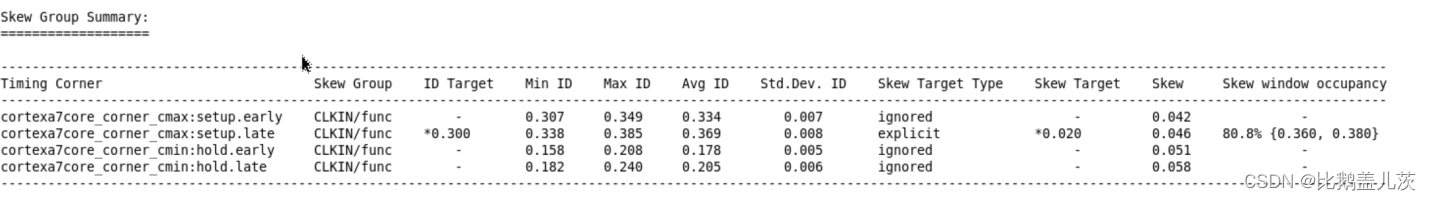

2.report_ccopt_skew_groups >

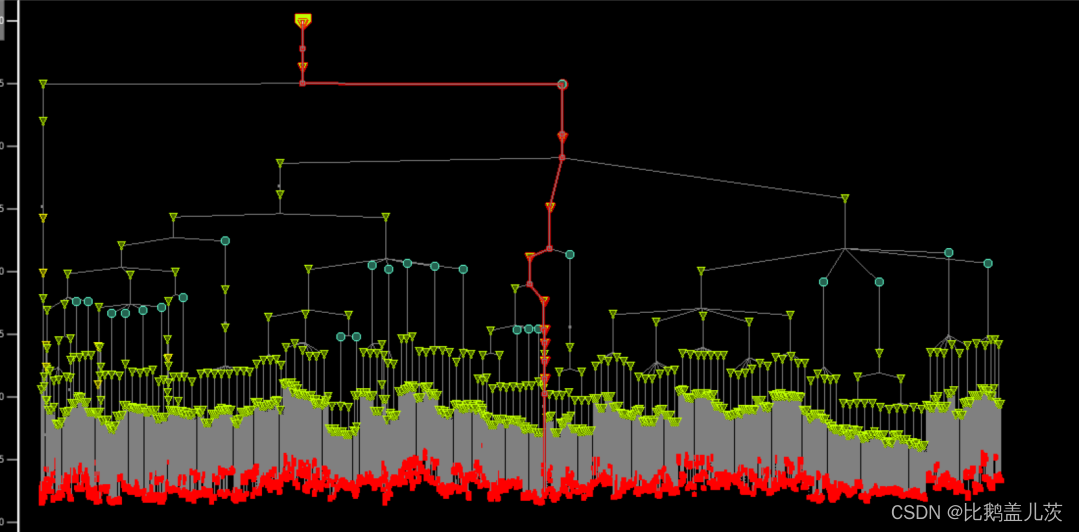

3.report_ccopt_clock_tree_structure

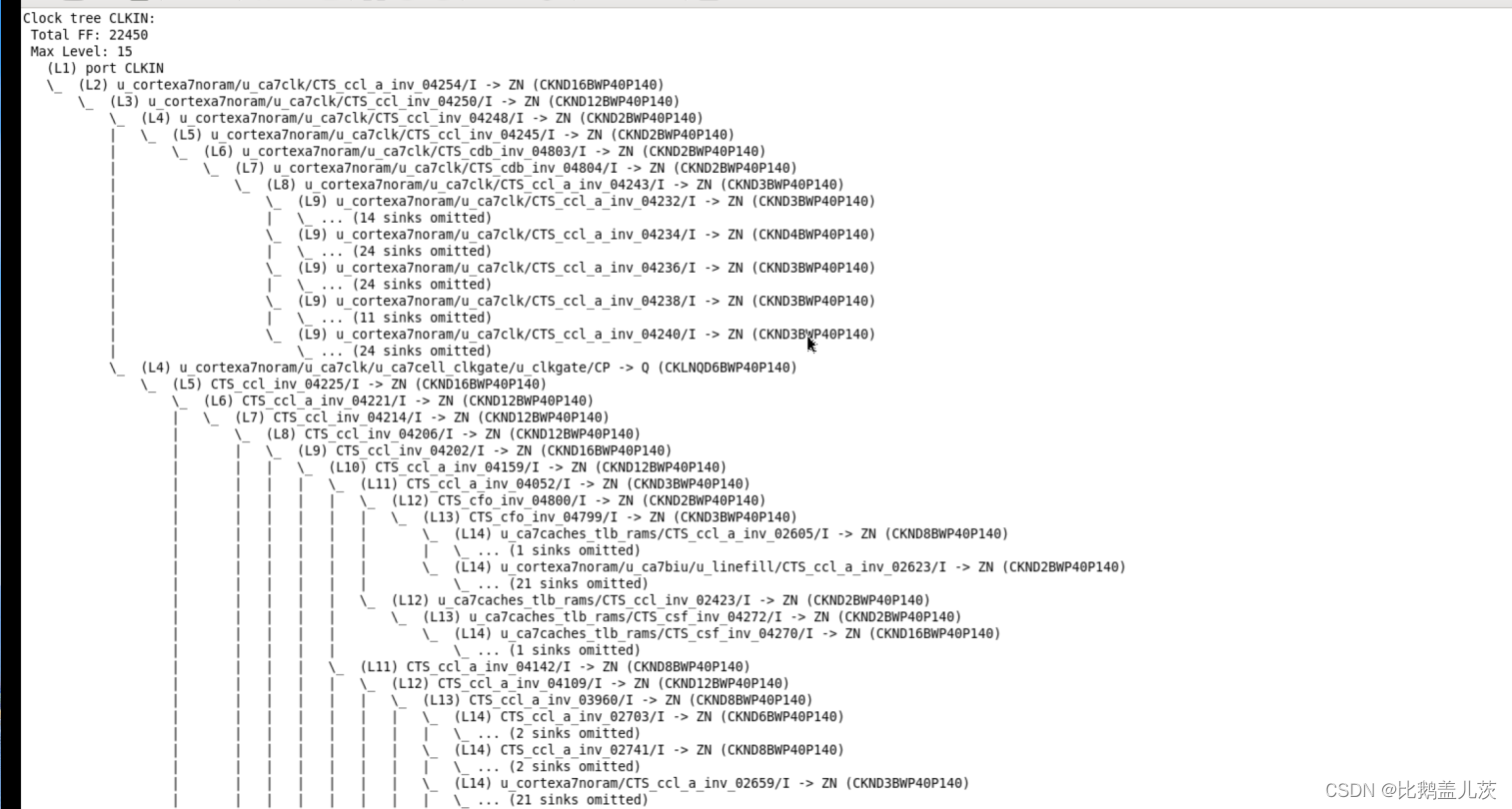

最大14级

1)每个clock group的clock tree级数。级数越大,说明clock tree latency越大。

2)每个时钟树各个level的clock inverter情况。比如看到ccl就代表这颗inverter是用于解transition的,看到cdb代表这颗inverter是用于balance用的。

3)clock tree上哪些是ignore pin,stop pin, exclude pin等信息看得非常清晰,这些会直接报出来的。

实际应用时假如我们发现某个点的tree不合理,我们可以直接在这里面直接搜索,来查看这个分支tree的具体情况,可以实现快速定位问题的目的。

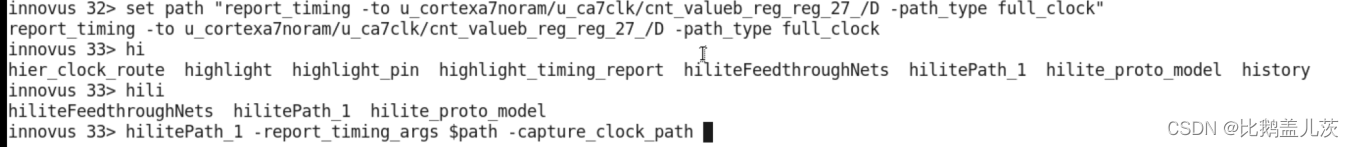

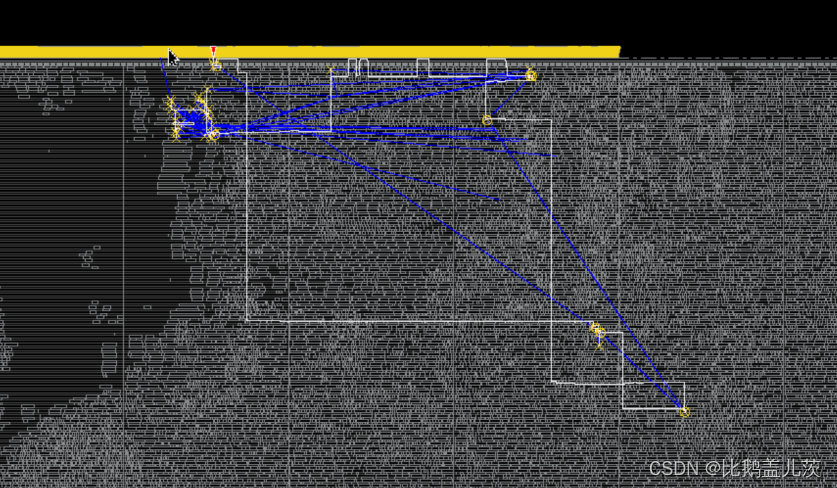

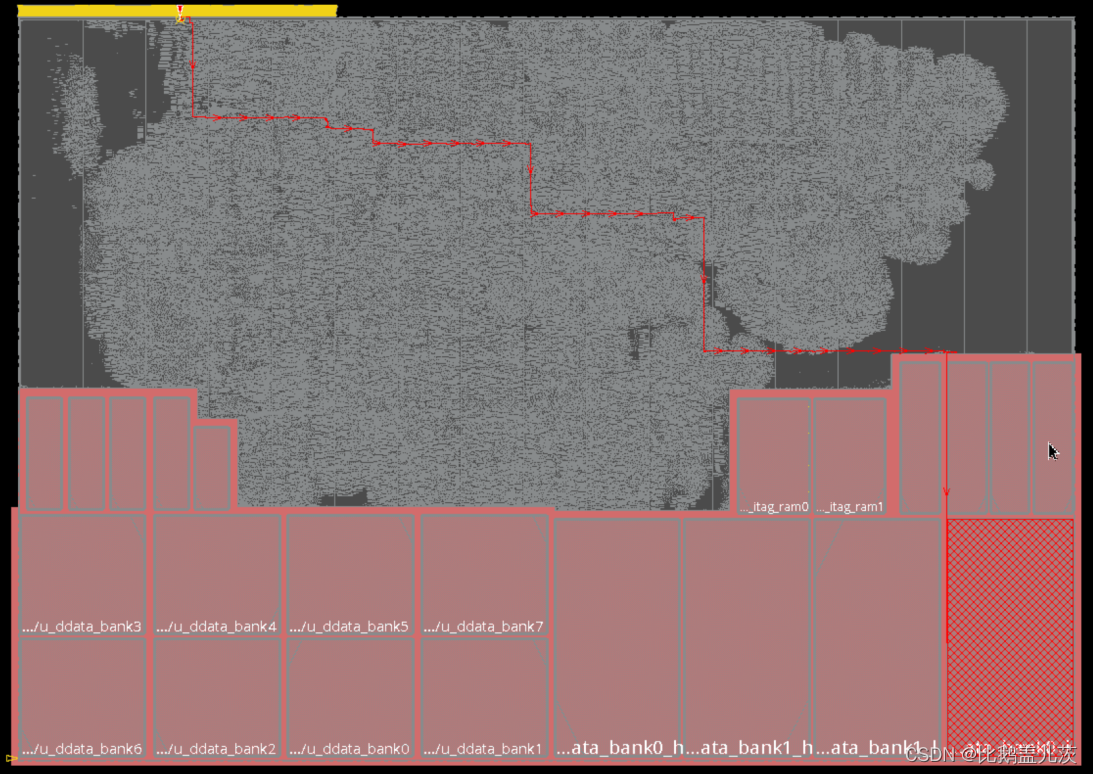

4.用已经写好的脚本高亮

结果:

clock latency 最长

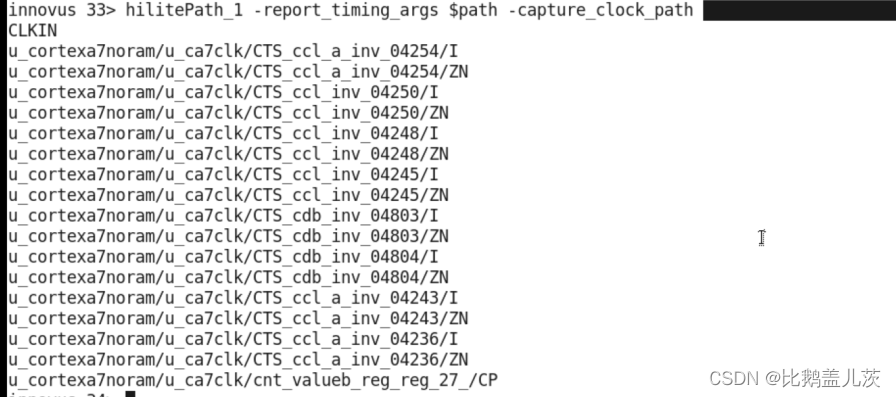

clock 物理最长

clock tree debugger(CTD)

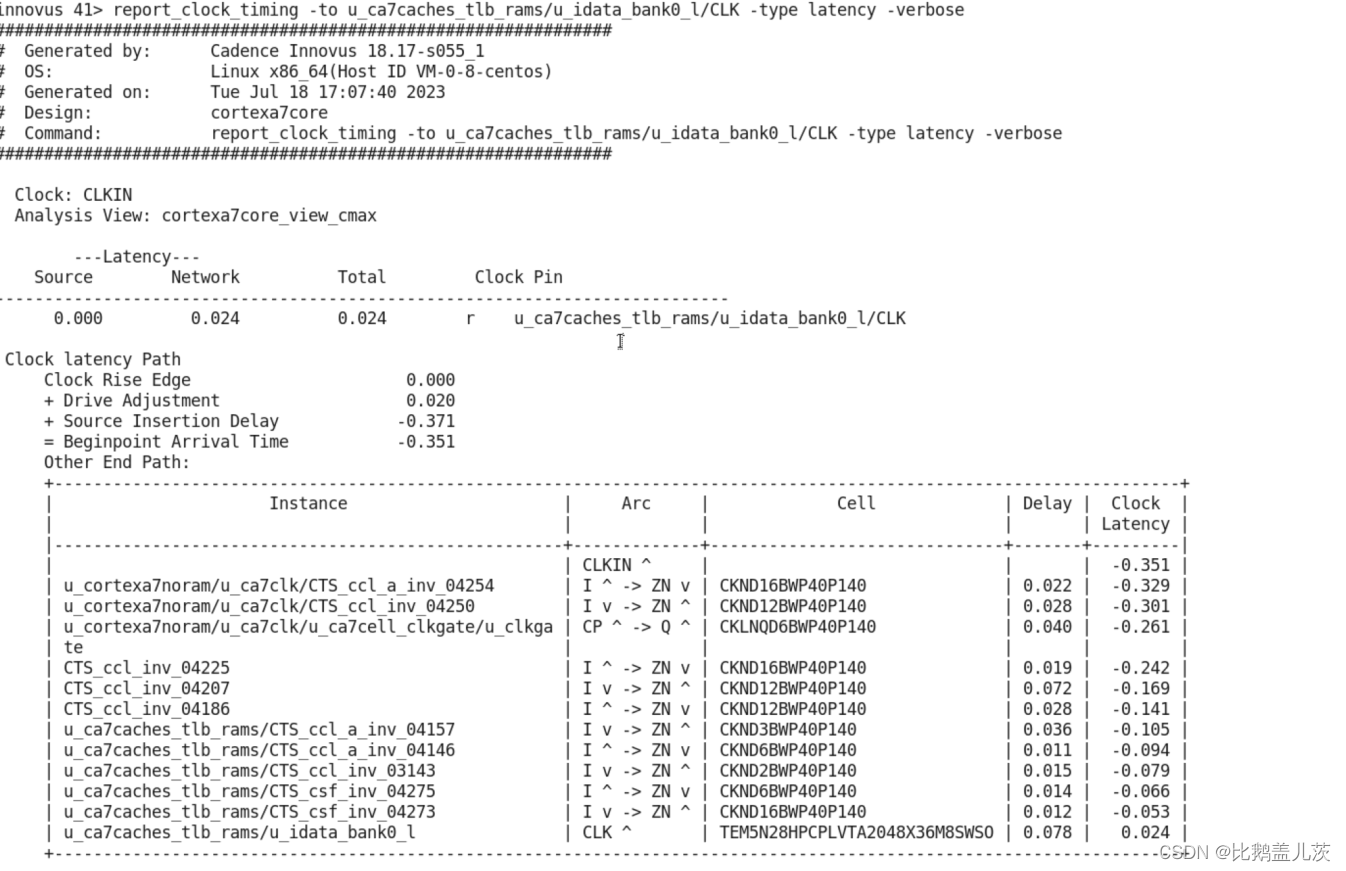

report_clock_timing

物理上最长的tree没有CDB cell,因为只有这样才不会使得其它path与之做balance,被拖累

2078

2078

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?