Latch up 最易产生在易受外部干扰的I/O电路处, 也偶尔发生在内部电路。

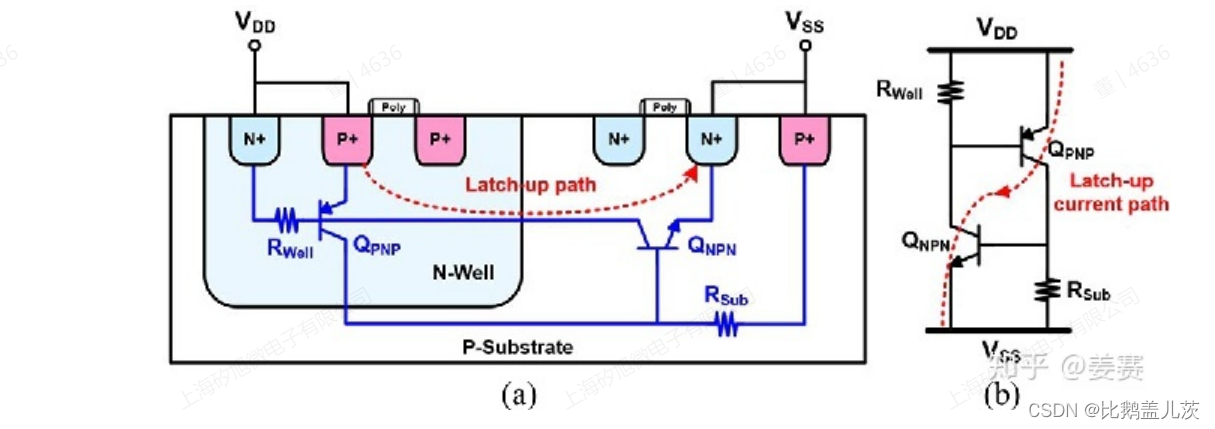

Latch up 是指cmos晶片中, 在电源power VDD和地线GND(VSS)之间由于寄生的PNP和NPN双极性BJT相互影响而产生的一低阻抗通路, 它的存在会使VDD和GND之间产生大电流。

Latch-up发生的条件:

(i) 当两个BJT都导通,在VDD和GND之间产生低阻抗通路;

(ii) 两个晶体管反馈回路(feedback loop)增益的乘积大于1( \beta_{1}\times\beta_{2}\ge1 )。

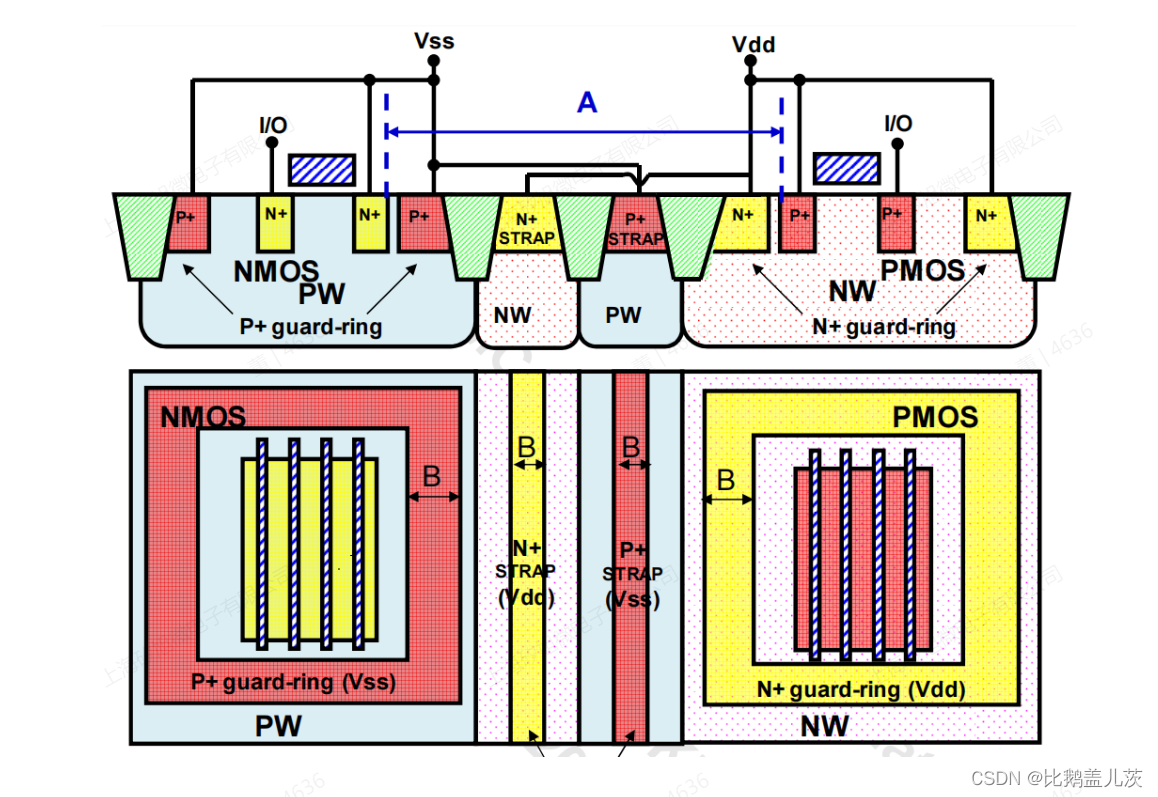

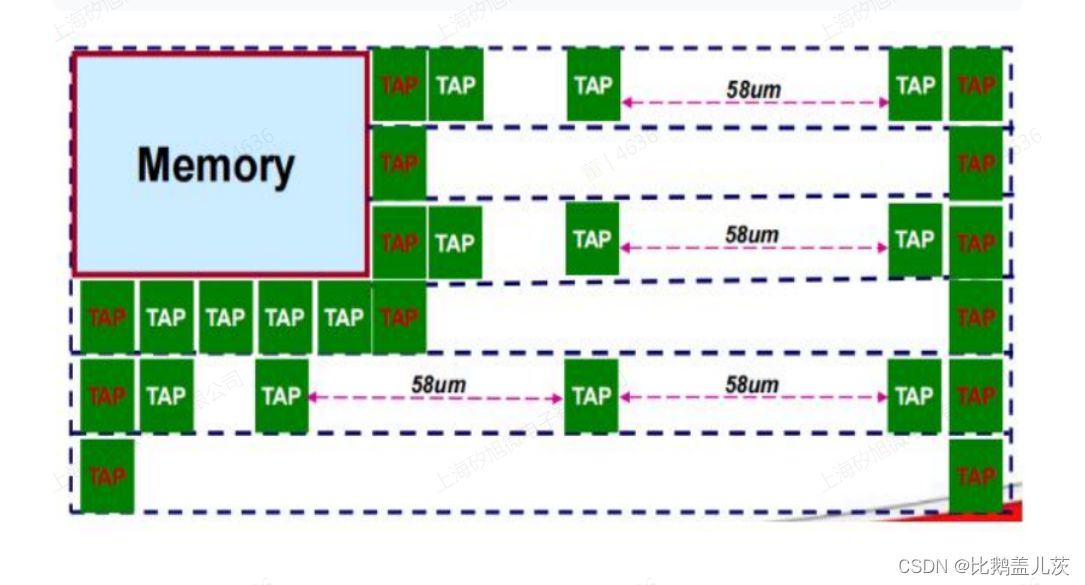

tap cell作用:

为避免闩锁,应尽可能频繁地插入p-substrate-tap(与Gnd连接)和n-well-tap(与Vdd连接)。这具有做空Rwell和Rsub的效果。从而阻止避免VDD直接相连到 GND的大电流导通

3323

3323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?