\qquad 下面是HD-GR基带模块宏设置的Verilog代码(下载完整的HD-GR基带模块代码):

// -*- Mode: Verilog -*-

// Filename : namuro_gnss_setup.v

// Description : contain settings for correlator core

//`define ENABLE_32BIT_ACCUMULATOR

//`define ENABLE_CARRIER_PHASE_MEASUREMENT

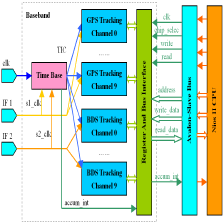

\qquad 下面是HD-GR基带顶层模块的Verilog代码(下载完整的HD-GR基带模块代码):

// -*- Mode: Verilog -*-

// Original filename : gps_baseband.v

// Filename : gnss_baseband.v

// Description : top level, includes address decoder, 10 GPS tracking channels,

// : and 10 BDS tracking channels

// Author : Peter Mumford UNSW 2005

// Author : Cheng Huaide, turing321.com, 2015 (BDS & 1PPS - processing upgrade)

// ----------------------------------------------------------------------------------------

// fix log

// ----------------------------------------------------------------------------------------

// 2/3/07 : Peter Mumford

// Fixed a problem when a new data read coincides or imediately

// follows a dump pulse. In this case the new data flag for that channel is lost.

// The fix involved capturing the dump state of all channels on a read of the

// new data register and using it as a mask for the new data flags.

// The following registers accomplish a two clock cycle wide mask function.

// reg [11:0] dump_mask; // mask a channel that has a dump aligned with the new data read

// reg [11:0] dump_mask_2; // mask for two clock cycles

// ----------------------------------------------------------------------------------------

/* This module connects to the Avalon bus

address map

block address offset

-------------------------

chan 0 (GPS) 00-0F

chan 1 (GPS) 10-1F

chan 2 (GPS) 20-2F

chan 3 (GPS) 30-3F

chan 4 (GPS) 40-4F

chan 5 (GPS) 50-5F

chan 6 (GPS) 60-6F

chan 7 (GPS) 70-7F

chan 8 (GPS) 80-8F

chan 9 (GPS) 90-9F

spare A0-CF

spare D0-DF

status E0-EF

control F0-FF

chan 10 (BDS) 100-10F

chan 11 (BDS) 110-11F

chan 12 (BDS) 120-12F

chan 13 (BDS) 130-13F

chan 14 (BDS) 140-14F

chan 15 (BDS) 150-15F

chan 16 (BDS) 160-16F

chan 17 (BDS) 170-17F

chan 18 (BDS) 180-18F

chan 19 (BDS) 190-19F

channel address offset

-------------------------

prn_key 0 write

carrier_nco 1 write

code_nco 2 write

code_slew 3 write

I_early 4 read

Q_early 5 read

I_prompt 6 read

Q_prompt 7 read

I_late 8 read

Q_late 9 read

carrier_val A read

code_val B read

epoch C read

epoch_check D read

epoch_load E write

spare F-F

status address offset

-------------------------

status 0 read // TIC = bit 0, ACCUM_INT = bit 1, cleared on read

new_data 1 read // chan0 = bit 0, chan1 = bit 1 etc, cleared on read

pps_tic_count 2 read // the current value of the 4 bit PPS TIC counter

spare 3-F

control address offset

-------------------------

reset 0

prog_tic_div 1 write

prog_accum_int 2 write

prog_pps_div 3 write

prog_tic_delay 4 write

prog_tic_load 5 write

spare 6-F

*/

`include "namuro_gnss_setup.v"

module gnss_baseband (clk, hw_rstn,

sample_clk_1, sign_in_1, mag_in_1,

sample_clk_2, sign_in_2, mag_in_2,

chip_select, write, read,

address, write_data, read_data,

accum_int, pps_timemark

);

input clk, hw_rstn, chip_select, write, read;

input sample_clk_1, sign_in_1, mag_in_1; // raw data in from RF front end 1

input sample_clk_2, sign_in_2, mag_in_2; // raw data in from RF front end 2

input [8:0] address;

input [31:0] write_data;

output reg [31:0] read_data;

output reg accum_int; // interrupt pulse to tell FW to collect accumulation data, cleared on STATUS read

output pps_timemark;

// wire s_clk;

// timing signals geenerated from time_base.v

wire accum_enable_s; // only used to generate accum_int signal in this module

wire pre_tic_enable; // only used in code_nco to generate hc_enable signal.

// pre_tic_enable is ahead of tic_enable a clk cycle.

wire tic_enable; // used in code_gento generate fc_enable signal.

wire accum_sample_enable_1; // only used to trigger RF front end 1 sampling accumulation in accumulator

wire accum_sample_enable_2; // only used to trigger RF front end 2 sampling accumulation in accumulator

wire [3:0] pps_tic_count;

reg sw_rst; // reset to tracking module

wire rstn; // software generated reset

// channel 0 registers (GPS)

reg [9:0] ch0_prn_key;

reg [28:0] ch0_carr_nco;

reg [27:0] ch0_code_nco;

reg [10:0] ch0_code_slew;

reg [10:0] ch0_epoch_load;

reg ch0_prn_key_enable, ch0_slew_enable, ch0_epoch_enable;

wire ch0_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch0_i_early, ch0_q_early, ch0_i_prompt, ch0_q_prompt, ch0_i_late, ch0_q_late;

`else

wire [15:0] ch0_i_early, ch0_q_early, ch0_i_prompt, ch0_q_prompt, ch0_i_late, ch0_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch0_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch0_code_val;

wire [10:0] ch0_epoch, ch0_epoch_check;

// channel 1 registers (GPS)

reg [9:0] ch1_prn_key;

reg [28:0] ch1_carr_nco;

reg [27:0] ch1_code_nco;

reg [10:0] ch1_code_slew;

reg [10:0] ch1_epoch_load;

reg ch1_prn_key_enable, ch1_slew_enable, ch1_epoch_enable;

wire ch1_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch1_i_early, ch1_q_early, ch1_i_prompt, ch1_q_prompt, ch1_i_late, ch1_q_late;

`else

wire [15:0] ch1_i_early, ch1_q_early, ch1_i_prompt, ch1_q_prompt, ch1_i_late, ch1_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch1_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch1_code_val;

wire [10:0] ch1_epoch, ch1_epoch_check;

// channel 2 registers (GPS)

reg [9:0] ch2_prn_key;

reg [28:0] ch2_carr_nco;

reg [27:0] ch2_code_nco;

reg [10:0] ch2_code_slew;

reg [10:0] ch2_epoch_load;

reg ch2_prn_key_enable, ch2_slew_enable, ch2_epoch_enable;

wire ch2_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch2_i_early, ch2_q_early, ch2_i_prompt, ch2_q_prompt, ch2_i_late, ch2_q_late;

`else

wire [15:0] ch2_i_early, ch2_q_early, ch2_i_prompt, ch2_q_prompt, ch2_i_late, ch2_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch2_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch2_code_val;

wire [10:0] ch2_epoch, ch2_epoch_check;

// channel 3 registers (GPS)

reg [9:0] ch3_prn_key;

reg [28:0] ch3_carr_nco;

reg [27:0] ch3_code_nco;

reg [10:0] ch3_code_slew;

reg [10:0] ch3_epoch_load;

reg ch3_prn_key_enable, ch3_slew_enable, ch3_epoch_enable;

wire ch3_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch3_i_early, ch3_q_early, ch3_i_prompt, ch3_q_prompt, ch3_i_late, ch3_q_late;

`else

wire [15:0] ch3_i_early, ch3_q_early, ch3_i_prompt, ch3_q_prompt, ch3_i_late, ch3_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch3_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch3_code_val;

wire [10:0] ch3_epoch, ch3_epoch_check;

// channel 4 registers (GPS)

reg [9:0] ch4_prn_key;

reg [28:0] ch4_carr_nco;

reg [27:0] ch4_code_nco;

reg [10:0] ch4_code_slew;

reg [10:0] ch4_epoch_load;

reg ch4_prn_key_enable, ch4_slew_enable, ch4_epoch_enable;

wire ch4_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch4_i_early, ch4_q_early, ch4_i_prompt, ch4_q_prompt, ch4_i_late, ch4_q_late;

`else

wire [15:0] ch4_i_early, ch4_q_early, ch4_i_prompt, ch4_q_prompt, ch4_i_late, ch4_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch4_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch4_code_val;

wire [10:0] ch4_epoch, ch4_epoch_check;

// channel 5 registers (GPS)

reg [9:0] ch5_prn_key;

reg [28:0] ch5_carr_nco;

reg [27:0] ch5_code_nco;

reg [10:0] ch5_code_slew;

reg [10:0] ch5_epoch_load;

reg ch5_prn_key_enable, ch5_slew_enable, ch5_epoch_enable;

wire ch5_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch5_i_early, ch5_q_early, ch5_i_prompt, ch5_q_prompt, ch5_i_late, ch5_q_late;

`else

wire [15:0] ch5_i_early, ch5_q_early, ch5_i_prompt, ch5_q_prompt, ch5_i_late, ch5_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch5_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch5_code_val;

wire [10:0] ch5_epoch, ch5_epoch_check;

// channel 6 registers (GPS)

reg [9:0] ch6_prn_key;

reg [28:0] ch6_carr_nco;

reg [27:0] ch6_code_nco;

reg [10:0] ch6_code_slew;

reg [10:0] ch6_epoch_load;

reg ch6_prn_key_enable, ch6_slew_enable, ch6_epoch_enable;

wire ch6_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch6_i_early, ch6_q_early, ch6_i_prompt, ch6_q_prompt, ch6_i_late, ch6_q_late;

`else

wire [15:0] ch6_i_early, ch6_q_early, ch6_i_prompt, ch6_q_prompt, ch6_i_late, ch6_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch6_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch6_code_val;

wire [10:0] ch6_epoch, ch6_epoch_check;

// channel 7 registers (GPS)

reg [9:0] ch7_prn_key;

reg [28:0] ch7_carr_nco;

reg [27:0] ch7_code_nco;

reg [10:0] ch7_code_slew;

reg [10:0] ch7_epoch_load;

reg ch7_prn_key_enable, ch7_slew_enable, ch7_epoch_enable;

wire ch7_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch7_i_early, ch7_q_early, ch7_i_prompt, ch7_q_prompt, ch7_i_late, ch7_q_late;

`else

wire [15:0] ch7_i_early, ch7_q_early, ch7_i_prompt, ch7_q_prompt, ch7_i_late, ch7_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch7_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch7_code_val;

wire [10:0] ch7_epoch, ch7_epoch_check;

// channel 8 registers (GPS)

reg [9:0] ch8_prn_key;

reg [28:0] ch8_carr_nco;

reg [27:0] ch8_code_nco;

reg [10:0] ch8_code_slew;

reg [10:0] ch8_epoch_load;

reg ch8_prn_key_enable, ch8_slew_enable, ch8_epoch_enable;

wire ch8_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch8_i_early, ch8_q_early, ch8_i_prompt, ch8_q_prompt, ch8_i_late, ch8_q_late;

`else

wire [15:0] ch8_i_early, ch8_q_early, ch8_i_prompt, ch8_q_prompt, ch8_i_late, ch8_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch8_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch8_code_val;

wire [10:0] ch8_epoch, ch8_epoch_check;

// channel 9 registers (GPS)

reg [9:0] ch9_prn_key;

reg [28:0] ch9_carr_nco;

reg [27:0] ch9_code_nco;

reg [10:0] ch9_code_slew;

reg [10:0] ch9_epoch_load;

reg ch9_prn_key_enable, ch9_slew_enable, ch9_epoch_enable;

wire ch9_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch9_i_early, ch9_q_early, ch9_i_prompt, ch9_q_prompt, ch9_i_late, ch9_q_late;

`else

wire [15:0] ch9_i_early, ch9_q_early, ch9_i_prompt, ch9_q_prompt, ch9_i_late, ch9_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch9_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [20:0] ch9_code_val;

wire [10:0] ch9_epoch, ch9_epoch_check;

// channel 10 registers (BDS)

reg [10:0] ch10_prn_key;

reg [28:0] ch10_carr_nco;

reg [27:0] ch10_code_nco;

reg [11:0] ch10_code_slew;

reg [10:0] ch10_epoch_load;

reg ch10_prn_key_enable, ch10_slew_enable, ch10_epoch_enable;

wire ch10_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch10_i_early, ch10_q_early, ch10_i_prompt, ch10_q_prompt, ch10_i_late, ch10_q_late;

`else

wire [15:0] ch10_i_early, ch10_q_early, ch10_i_prompt, ch10_q_prompt, ch10_i_late, ch10_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch10_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch10_code_val;

wire [10:0] ch10_epoch, ch10_epoch_check;

// channel 11 registers (BDS)

reg [10:0] ch11_prn_key;

reg [28:0] ch11_carr_nco;

reg [27:0] ch11_code_nco;

reg [11:0] ch11_code_slew;

reg [10:0] ch11_epoch_load;

reg ch11_prn_key_enable, ch11_slew_enable, ch11_epoch_enable;

wire ch11_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch11_i_early, ch11_q_early, ch11_i_prompt, ch11_q_prompt, ch11_i_late, ch11_q_late;

`else

wire [15:0] ch11_i_early, ch11_q_early, ch11_i_prompt, ch11_q_prompt, ch11_i_late, ch11_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch11_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch11_code_val;

wire [10:0] ch11_epoch, ch11_epoch_check;

// channel 12 registers (BDS)

reg [10:0] ch12_prn_key;

reg [28:0] ch12_carr_nco;

reg [27:0] ch12_code_nco;

reg [11:0] ch12_code_slew;

reg [10:0] ch12_epoch_load;

reg ch12_prn_key_enable, ch12_slew_enable, ch12_epoch_enable;

wire ch12_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch12_i_early, ch12_q_early, ch12_i_prompt, ch12_q_prompt, ch12_i_late, ch12_q_late;

`else

wire [15:0] ch12_i_early, ch12_q_early, ch12_i_prompt, ch12_q_prompt, ch12_i_late, ch12_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch12_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch12_code_val;

wire [10:0] ch12_epoch, ch12_epoch_check;

// channel 13 registers (BDS)

reg [10:0] ch13_prn_key;

reg [28:0] ch13_carr_nco;

reg [27:0] ch13_code_nco;

reg [11:0] ch13_code_slew;

reg [10:0] ch13_epoch_load;

reg ch13_prn_key_enable, ch13_slew_enable, ch13_epoch_enable;

wire ch13_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch13_i_early, ch13_q_early, ch13_i_prompt, ch13_q_prompt, ch13_i_late, ch13_q_late;

`else

wire [15:0] ch13_i_early, ch13_q_early, ch13_i_prompt, ch13_q_prompt, ch13_i_late, ch13_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch13_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch13_code_val;

wire [10:0] ch13_epoch, ch13_epoch_check;

// channel 14 registers (BDS)

reg [10:0] ch14_prn_key;

reg [28:0] ch14_carr_nco;

reg [27:0] ch14_code_nco;

reg [11:0] ch14_code_slew;

reg [10:0] ch14_epoch_load;

reg ch14_prn_key_enable, ch14_slew_enable, ch14_epoch_enable;

wire ch14_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch14_i_early, ch14_q_early, ch14_i_prompt, ch14_q_prompt, ch14_i_late, ch14_q_late;

`else

wire [15:0] ch14_i_early, ch14_q_early, ch14_i_prompt, ch14_q_prompt, ch14_i_late, ch14_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch14_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch14_code_val;

wire [10:0] ch14_epoch, ch14_epoch_check;

// channel 15 registers (BDS)

reg [10:0] ch15_prn_key;

reg [28:0] ch15_carr_nco;

reg [27:0] ch15_code_nco;

reg [11:0] ch15_code_slew;

reg [10:0] ch15_epoch_load;

reg ch15_prn_key_enable, ch15_slew_enable, ch15_epoch_enable;

wire ch15_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch15_i_early, ch15_q_early, ch15_i_prompt, ch15_q_prompt, ch15_i_late, ch15_q_late;

`else

wire [15:0] ch15_i_early, ch15_q_early, ch15_i_prompt, ch15_q_prompt, ch15_i_late, ch15_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch15_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch15_code_val;

wire [10:0] ch15_epoch, ch15_epoch_check;

// channel 16 registers (BDS)

reg [10:0] ch16_prn_key;

reg [28:0] ch16_carr_nco;

reg [27:0] ch16_code_nco;

reg [11:0] ch16_code_slew;

reg [10:0] ch16_epoch_load;

reg ch16_prn_key_enable, ch16_slew_enable, ch16_epoch_enable;

wire ch16_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch16_i_early, ch16_q_early, ch16_i_prompt, ch16_q_prompt, ch16_i_late, ch16_q_late;

`else

wire [15:0] ch16_i_early, ch16_q_early, ch16_i_prompt, ch16_q_prompt, ch16_i_late, ch16_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch16_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch16_code_val;

wire [10:0] ch16_epoch, ch16_epoch_check;

// channel 17 registers (BDS)

reg [10:0] ch17_prn_key;

reg [28:0] ch17_carr_nco;

reg [27:0] ch17_code_nco;

reg [11:0] ch17_code_slew;

reg [10:0] ch17_epoch_load;

reg ch17_prn_key_enable, ch17_slew_enable, ch17_epoch_enable;

wire ch17_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch17_i_early, ch17_q_early, ch17_i_prompt, ch17_q_prompt, ch17_i_late, ch17_q_late;

`else

wire [15:0] ch17_i_early, ch17_q_early, ch17_i_prompt, ch17_q_prompt, ch17_i_late, ch17_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch17_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch17_code_val;

wire [10:0] ch17_epoch, ch17_epoch_check;

// channel 18 registers (BDS)

reg [10:0] ch18_prn_key;

reg [28:0] ch18_carr_nco;

reg [27:0] ch18_code_nco;

reg [11:0] ch18_code_slew;

reg [10:0] ch18_epoch_load;

reg ch18_prn_key_enable, ch18_slew_enable, ch18_epoch_enable;

wire ch18_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch18_i_early, ch18_q_early, ch18_i_prompt, ch18_q_prompt, ch18_i_late, ch18_q_late;

`else

wire [15:0] ch18_i_early, ch18_q_early, ch18_i_prompt, ch18_q_prompt, ch18_i_late, ch18_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch18_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch18_code_val;

wire [10:0] ch18_epoch, ch18_epoch_check;

// channel 19 registers (BDS)

reg [10:0] ch19_prn_key;

reg [28:0] ch19_carr_nco;

reg [27:0] ch19_code_nco;

reg [11:0] ch19_code_slew;

reg [10:0] ch19_epoch_load;

reg ch19_prn_key_enable, ch19_slew_enable, ch19_epoch_enable;

wire ch19_dump;

`ifdef ENABLE_32BIT_ACCUMULATOR

wire [31:0] ch19_i_early, ch19_q_early, ch19_i_prompt, ch19_q_prompt, ch19_i_late, ch19_q_late;

`else

wire [15:0] ch19_i_early, ch19_q_early, ch19_i_prompt, ch19_q_prompt, ch19_i_late, ch19_q_late;

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

wire [31:0] ch19_carrier_val;

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

wire [22:0] ch19_code_val;

wire [10:0] ch19_epoch, ch19_epoch_check;

// status registers

reg [1:0] status; // TIC = bit 0, ACCUM_INT = bit 1, cleared on read

reg status_read; // pulse when status register is read

reg [19:0] new_data; // chan0 = bit 0, chan1 = bit 1 etc, cleared on read

reg new_data_read; // pules when new_data register is read

reg [19:0] dump_mask; // mask a channel that has a dump aligned with the new data read

reg [19:0] dump_mask_2; // mask for two clock cycles

// control registers

reg [24:0] prog_tic_div;

reg [17:0] prog_accum_int;

reg tic_delay_enable;

reg [31:0] tic_delay_value;

reg [17:0] prog_pps_div;

reg pps_tic_enable;

reg [3:0] pps_tic_load;

reg [17:0] pps_q; // output of counter pe

wire pps_tic_0;

/*

// sign and mag samples

reg sign, sign_tmp;

reg mag, mag_tmp;

// metastability input registers for sign and mag

always @ (posedge clk) begin

if (!hw_rstn) begin

sign_tmp <= 0;

sign <= 0;

mag_tmp <= 0;

mag <= 0;

end

else begin

sign_tmp <= sign_in_1;

sign <= sign_tmp;

mag_tmp <= mag_in_1;

mag <= mag_tmp;

end

end

*/

// connect up time base

time_base tb (.clk(clk), .rstn(rstn),

.accum_divide(prog_accum_int),

.tic_divide(prog_tic_div),

.tic_delay_enable(tic_delay_enable),

.tic_delay_value(tic_delay_value),

.pps_tic_enable(pps_tic_enable),

.pps_tic_load(pps_tic_load),

.pps_tic_0(pps_tic_0),

.pps_tic_count(pps_tic_count),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.accum_enable(accum_enable_s),

.sample_clk_1(sample_clk_1),

.accum_sample_enable_1(accum_sample_enable_1),

.sample_clk_2(sample_clk_2),

.accum_sample_enable_2(accum_sample_enable_2)

);

//assign sample_clk_1 = s_clk;

assign rstn = hw_rstn & ~sw_rst;

// connect up tracking channels

gps_tracking_channel gps_tc0 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch0_carr_nco),

.code_nco_fc(ch0_code_nco),

.prn_key(ch0_prn_key),

.prn_key_enable(ch0_prn_key_enable),

.code_slew(ch0_code_slew),

.slew_enable(ch0_slew_enable),

.epoch_enable(ch0_epoch_enable),

.dump(ch0_dump),

.i_early(ch0_i_early),

.q_early(ch0_q_early),

.i_prompt(ch0_i_prompt),

.q_prompt(ch0_q_prompt),

.i_late(ch0_i_late),

.q_late(ch0_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch0_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch0_code_val),

.epoch_load(ch0_epoch_load),

.epoch(ch0_epoch),

.epoch_check(ch0_epoch_check));

gps_tracking_channel gps_tc1 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch1_carr_nco),

.code_nco_fc(ch1_code_nco),

.prn_key(ch1_prn_key),

.prn_key_enable(ch1_prn_key_enable),

.code_slew(ch1_code_slew),

.slew_enable(ch1_slew_enable),

.epoch_enable(ch1_epoch_enable),

.dump(ch1_dump),

.i_early(ch1_i_early),

.q_early(ch1_q_early),

.i_prompt(ch1_i_prompt),

.q_prompt(ch1_q_prompt),

.i_late(ch1_i_late),

.q_late(ch1_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch1_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch1_code_val),

.epoch_load(ch1_epoch_load),

.epoch(ch1_epoch),

.epoch_check(ch1_epoch_check));

gps_tracking_channel gps_tc2 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch2_carr_nco),

.code_nco_fc(ch2_code_nco),

.prn_key(ch2_prn_key),

.prn_key_enable(ch2_prn_key_enable),

.code_slew(ch2_code_slew),

.slew_enable(ch2_slew_enable),

.epoch_enable(ch2_epoch_enable),

.dump(ch2_dump),

.i_early(ch2_i_early),

.q_early(ch2_q_early),

.i_prompt(ch2_i_prompt),

.q_prompt(ch2_q_prompt),

.i_late(ch2_i_late),

.q_late(ch2_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch2_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch2_code_val),

.epoch_load(ch2_epoch_load),

.epoch(ch2_epoch),

.epoch_check(ch2_epoch_check));

gps_tracking_channel gps_tc3 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch3_carr_nco),

.code_nco_fc(ch3_code_nco),

.prn_key(ch3_prn_key),

.prn_key_enable(ch3_prn_key_enable),

.code_slew(ch3_code_slew),

.slew_enable(ch3_slew_enable),

.epoch_enable(ch3_epoch_enable),

.dump(ch3_dump),

.i_early(ch3_i_early),

.q_early(ch3_q_early),

.i_prompt(ch3_i_prompt),

.q_prompt(ch3_q_prompt),

.i_late(ch3_i_late),

.q_late(ch3_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch3_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch3_code_val),

.epoch_load(ch3_epoch_load),

.epoch(ch3_epoch),

.epoch_check(ch3_epoch_check));

gps_tracking_channel gps_tc4 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch4_carr_nco),

.code_nco_fc(ch4_code_nco),

.prn_key(ch4_prn_key),

.prn_key_enable(ch4_prn_key_enable),

.code_slew(ch4_code_slew),

.slew_enable(ch4_slew_enable),

.epoch_enable(ch4_epoch_enable),

.dump(ch4_dump),

.i_early(ch4_i_early),

.q_early(ch4_q_early),

.i_prompt(ch4_i_prompt),

.q_prompt(ch4_q_prompt),

.i_late(ch4_i_late),

.q_late(ch4_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch4_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch4_code_val),

.epoch_load(ch4_epoch_load),

.epoch(ch4_epoch),

.epoch_check(ch4_epoch_check));

gps_tracking_channel gps_tc5 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch5_carr_nco),

.code_nco_fc(ch5_code_nco),

.prn_key(ch5_prn_key),

.prn_key_enable(ch5_prn_key_enable),

.code_slew(ch5_code_slew),

.slew_enable(ch5_slew_enable),

.epoch_enable(ch5_epoch_enable),

.dump(ch5_dump),

.i_early(ch5_i_early),

.q_early(ch5_q_early),

.i_prompt(ch5_i_prompt),

.q_prompt(ch5_q_prompt),

.i_late(ch5_i_late),

.q_late(ch5_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch5_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch5_code_val),

.epoch_load(ch5_epoch_load),

.epoch(ch5_epoch),

.epoch_check(ch5_epoch_check));

gps_tracking_channel gps_tc6 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch6_carr_nco),

.code_nco_fc(ch6_code_nco),

.prn_key(ch6_prn_key),

.prn_key_enable(ch6_prn_key_enable),

.code_slew(ch6_code_slew),

.slew_enable(ch6_slew_enable),

.epoch_enable(ch6_epoch_enable),

.dump(ch6_dump),

.i_early(ch6_i_early),

.q_early(ch6_q_early),

.i_prompt(ch6_i_prompt),

.q_prompt(ch6_q_prompt),

.i_late(ch6_i_late),

.q_late(ch6_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch6_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch6_code_val),

.epoch_load(ch6_epoch_load),

.epoch(ch6_epoch),

.epoch_check(ch6_epoch_check));

gps_tracking_channel gps_tc7 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch7_carr_nco),

.code_nco_fc(ch7_code_nco),

.prn_key(ch7_prn_key),

.prn_key_enable(ch7_prn_key_enable),

.code_slew(ch7_code_slew),

.slew_enable(ch7_slew_enable),

.epoch_enable(ch7_epoch_enable),

.dump(ch7_dump),

.i_early(ch7_i_early),

.q_early(ch7_q_early),

.i_prompt(ch7_i_prompt),

.q_prompt(ch7_q_prompt),

.i_late(ch7_i_late),

.q_late(ch7_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch7_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch7_code_val),

.epoch_load(ch7_epoch_load),

.epoch(ch7_epoch),

.epoch_check(ch7_epoch_check));

gps_tracking_channel gps_tc8 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch8_carr_nco),

.code_nco_fc(ch8_code_nco),

.prn_key(ch8_prn_key),

.prn_key_enable(ch8_prn_key_enable),

.code_slew(ch8_code_slew),

.slew_enable(ch8_slew_enable),

.epoch_enable(ch8_epoch_enable),

.dump(ch8_dump),

.i_early(ch8_i_early),

.q_early(ch8_q_early),

.i_prompt(ch8_i_prompt),

.q_prompt(ch8_q_prompt),

.i_late(ch8_i_late),

.q_late(ch8_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch8_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch8_code_val),

.epoch_load(ch8_epoch_load),

.epoch(ch8_epoch),

.epoch_check(ch8_epoch_check));

gps_tracking_channel gps_tc9 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_1),

.if_sign(sign_in_1), .if_mag(mag_in_1),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch9_carr_nco),

.code_nco_fc(ch9_code_nco),

.prn_key(ch9_prn_key),

.prn_key_enable(ch9_prn_key_enable),

.code_slew(ch9_code_slew),

.slew_enable(ch9_slew_enable),

.epoch_enable(ch9_epoch_enable),

.dump(ch9_dump),

.i_early(ch9_i_early),

.q_early(ch9_q_early),

.i_prompt(ch9_i_prompt),

.q_prompt(ch9_q_prompt),

.i_late(ch9_i_late),

.q_late(ch9_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch9_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch9_code_val),

.epoch_load(ch9_epoch_load),

.epoch(ch9_epoch),

.epoch_check(ch9_epoch_check));

bds_tracking_channel bds_tc10 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch10_carr_nco),

.code_nco_fc(ch10_code_nco),

.prn_key(ch10_prn_key),

.prn_key_enable(ch10_prn_key_enable),

.code_slew(ch10_code_slew),

.slew_enable(ch10_slew_enable),

.epoch_enable(ch10_epoch_enable),

.dump(ch10_dump),

.i_early(ch10_i_early),

.q_early(ch10_q_early),

.i_prompt(ch10_i_prompt),

.q_prompt(ch10_q_prompt),

.i_late(ch10_i_late),

.q_late(ch10_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch10_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch10_code_val),

.epoch_load(ch10_epoch_load),

.epoch(ch10_epoch),

.epoch_check(ch10_epoch_check));

bds_tracking_channel bds_tc11 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch11_carr_nco),

.code_nco_fc(ch11_code_nco),

.prn_key(ch11_prn_key),

.prn_key_enable(ch11_prn_key_enable),

.code_slew(ch11_code_slew),

.slew_enable(ch11_slew_enable),

.epoch_enable(ch11_epoch_enable),

.dump(ch11_dump),

.i_early(ch11_i_early),

.q_early(ch11_q_early),

.i_prompt(ch11_i_prompt),

.q_prompt(ch11_q_prompt),

.i_late(ch11_i_late),

.q_late(ch11_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch11_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch11_code_val),

.epoch_load(ch11_epoch_load),

.epoch(ch11_epoch),

.epoch_check(ch11_epoch_check));

bds_tracking_channel bds_tc12 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch12_carr_nco),

.code_nco_fc(ch12_code_nco),

.prn_key(ch12_prn_key),

.prn_key_enable(ch12_prn_key_enable),

.code_slew(ch12_code_slew),

.slew_enable(ch12_slew_enable),

.epoch_enable(ch12_epoch_enable),

.dump(ch12_dump),

.i_early(ch12_i_early),

.q_early(ch12_q_early),

.i_prompt(ch12_i_prompt),

.q_prompt(ch12_q_prompt),

.i_late(ch12_i_late),

.q_late(ch12_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch12_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch12_code_val),

.epoch_load(ch12_epoch_load),

.epoch(ch12_epoch),

.epoch_check(ch12_epoch_check));

bds_tracking_channel bds_tc13 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch13_carr_nco),

.code_nco_fc(ch13_code_nco),

.prn_key(ch13_prn_key),

.prn_key_enable(ch13_prn_key_enable),

.code_slew(ch13_code_slew),

.slew_enable(ch13_slew_enable),

.epoch_enable(ch13_epoch_enable),

.dump(ch13_dump),

.i_early(ch13_i_early),

.q_early(ch13_q_early),

.i_prompt(ch13_i_prompt),

.q_prompt(ch13_q_prompt),

.i_late(ch13_i_late),

.q_late(ch13_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch13_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch13_code_val),

.epoch_load(ch13_epoch_load),

.epoch(ch13_epoch),

.epoch_check(ch13_epoch_check));

bds_tracking_channel bds_tc14 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch14_carr_nco),

.code_nco_fc(ch14_code_nco),

.prn_key(ch14_prn_key),

.prn_key_enable(ch14_prn_key_enable),

.code_slew(ch14_code_slew),

.slew_enable(ch14_slew_enable),

.epoch_enable(ch14_epoch_enable),

.dump(ch14_dump),

.i_early(ch14_i_early),

.q_early(ch14_q_early),

.i_prompt(ch14_i_prompt),

.q_prompt(ch14_q_prompt),

.i_late(ch14_i_late),

.q_late(ch14_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch14_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch14_code_val),

.epoch_load(ch14_epoch_load),

.epoch(ch14_epoch),

.epoch_check(ch14_epoch_check));

bds_tracking_channel bds_tc15 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch15_carr_nco),

.code_nco_fc(ch15_code_nco),

.prn_key(ch15_prn_key),

.prn_key_enable(ch15_prn_key_enable),

.code_slew(ch15_code_slew),

.slew_enable(ch15_slew_enable),

.epoch_enable(ch15_epoch_enable),

.dump(ch15_dump),

.i_early(ch15_i_early),

.q_early(ch15_q_early),

.i_prompt(ch15_i_prompt),

.q_prompt(ch15_q_prompt),

.i_late(ch15_i_late),

.q_late(ch15_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch15_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch15_code_val),

.epoch_load(ch15_epoch_load),

.epoch(ch15_epoch),

.epoch_check(ch15_epoch_check));

bds_tracking_channel bds_tc16 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch16_carr_nco),

.code_nco_fc(ch16_code_nco),

.prn_key(ch16_prn_key),

.prn_key_enable(ch16_prn_key_enable),

.code_slew(ch16_code_slew),

.slew_enable(ch16_slew_enable),

.epoch_enable(ch16_epoch_enable),

.dump(ch16_dump),

.i_early(ch16_i_early),

.q_early(ch16_q_early),

.i_prompt(ch16_i_prompt),

.q_prompt(ch16_q_prompt),

.i_late(ch16_i_late),

.q_late(ch16_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch16_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch16_code_val),

.epoch_load(ch16_epoch_load),

.epoch(ch16_epoch),

.epoch_check(ch16_epoch_check));

bds_tracking_channel bds_tc17 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch17_carr_nco),

.code_nco_fc(ch17_code_nco),

.prn_key(ch17_prn_key),

.prn_key_enable(ch17_prn_key_enable),

.code_slew(ch17_code_slew),

.slew_enable(ch17_slew_enable),

.epoch_enable(ch17_epoch_enable),

.dump(ch17_dump),

.i_early(ch17_i_early),

.q_early(ch17_q_early),

.i_prompt(ch17_i_prompt),

.q_prompt(ch17_q_prompt),

.i_late(ch17_i_late),

.q_late(ch17_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch17_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch17_code_val),

.epoch_load(ch17_epoch_load),

.epoch(ch17_epoch),

.epoch_check(ch17_epoch_check));

bds_tracking_channel bds_tc18 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch18_carr_nco),

.code_nco_fc(ch18_code_nco),

.prn_key(ch18_prn_key),

.prn_key_enable(ch18_prn_key_enable),

.code_slew(ch18_code_slew),

.slew_enable(ch18_slew_enable),

.epoch_enable(ch18_epoch_enable),

.dump(ch18_dump),

.i_early(ch18_i_early),

.q_early(ch18_q_early),

.i_prompt(ch18_i_prompt),

.q_prompt(ch18_q_prompt),

.i_late(ch18_i_late),

.q_late(ch18_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch18_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch18_code_val),

.epoch_load(ch18_epoch_load),

.epoch(ch18_epoch),

.epoch_check(ch18_epoch_check));

bds_tracking_channel bds_tc19 (

.clk(clk), .rstn(rstn),

.accum_sample_enable(accum_sample_enable_2),

.if_sign(sign_in_2), .if_mag(mag_in_2),

.pre_tic_enable(pre_tic_enable),

.tic_enable(tic_enable),

.carr_nco_fc(ch19_carr_nco),

.code_nco_fc(ch19_code_nco),

.prn_key(ch19_prn_key),

.prn_key_enable(ch19_prn_key_enable),

.code_slew(ch19_code_slew),

.slew_enable(ch19_slew_enable),

.epoch_enable(ch19_epoch_enable),

.dump(ch19_dump),

.i_early(ch19_i_early),

.q_early(ch19_q_early),

.i_prompt(ch19_i_prompt),

.q_prompt(ch19_q_prompt),

.i_late(ch19_i_late),

.q_late(ch19_q_late),

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

.carrier_val(ch19_carrier_val),

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

.code_val(ch19_code_val),

.epoch_load(ch19_epoch_load),

.epoch(ch19_epoch),

.epoch_check(ch19_epoch_check));

// address decoder ----------------------------------

always @ (posedge clk)

begin

if (!hw_rstn)

begin

// Need to initialize nco's (at least for simulation) or they don't run.

ch0_carr_nco <= 0;

ch1_carr_nco <= 0;

ch2_carr_nco <= 0;

ch3_carr_nco <= 0;

ch4_carr_nco <= 0;

ch5_carr_nco <= 0;

ch6_carr_nco <= 0;

ch7_carr_nco <= 0;

ch8_carr_nco <= 0;

ch9_carr_nco <= 0;

ch0_code_nco <= 0;

ch1_code_nco <= 0;

ch2_code_nco <= 0;

ch3_code_nco <= 0;

ch4_code_nco <= 0;

ch5_code_nco <= 0;

ch6_code_nco <= 0;

ch7_code_nco <= 0;

ch8_code_nco <= 0;

ch9_code_nco <= 0;

ch10_carr_nco <= 0;

ch11_carr_nco <= 0;

ch12_carr_nco <= 0;

ch13_carr_nco <= 0;

ch14_carr_nco <= 0;

ch15_carr_nco <= 0;

ch16_carr_nco <= 0;

ch17_carr_nco <= 0;

ch18_carr_nco <= 0;

ch19_carr_nco <= 0;

ch10_code_nco <= 0;

ch11_code_nco <= 0;

ch12_code_nco <= 0;

ch13_code_nco <= 0;

ch14_code_nco <= 0;

ch15_code_nco <= 0;

ch16_code_nco <= 0;

ch17_code_nco <= 0;

ch18_code_nco <= 0;

ch19_code_nco <= 0;

// Anything else need initializing here?

tic_delay_value <= 0;

pps_tic_load <= 0;

end

else

begin

sw_rst <= 0;

status_read <= 0;

new_data_read <= 0;

ch0_prn_key_enable <= 0;

ch0_slew_enable <= 0;

ch0_epoch_enable <= 0;

ch1_prn_key_enable <= 0;

ch1_slew_enable <= 0;

ch1_epoch_enable <= 0;

ch2_prn_key_enable <= 0;

ch2_slew_enable <= 0;

ch2_epoch_enable <= 0;

ch3_prn_key_enable <= 0;

ch3_slew_enable <= 0;

ch3_epoch_enable <= 0;

ch4_prn_key_enable <= 0;

ch4_slew_enable <= 0;

ch4_epoch_enable <= 0;

ch5_prn_key_enable <= 0;

ch5_slew_enable <= 0;

ch5_epoch_enable <= 0;

ch6_prn_key_enable <= 0;

ch6_slew_enable <= 0;

ch6_epoch_enable <= 0;

ch7_prn_key_enable <= 0;

ch7_slew_enable <= 0;

ch7_epoch_enable <= 0;

ch8_prn_key_enable <= 0;

ch8_slew_enable <= 0;

ch8_epoch_enable <= 0;

ch9_prn_key_enable <= 0;

ch9_slew_enable <= 0;

ch9_epoch_enable <= 0;

ch10_prn_key_enable <= 0;

ch10_slew_enable <= 0;

ch10_epoch_enable <= 0;

ch11_prn_key_enable <= 0;

ch11_slew_enable <= 0;

ch11_epoch_enable <= 0;

ch12_prn_key_enable <= 0;

ch12_slew_enable <= 0;

ch12_epoch_enable <= 0;

ch13_prn_key_enable <= 0;

ch13_slew_enable <= 0;

ch13_epoch_enable <= 0;

ch14_prn_key_enable <= 0;

ch14_slew_enable <= 0;

ch14_epoch_enable <= 0;

ch15_prn_key_enable <= 0;

ch15_slew_enable <= 0;

ch15_epoch_enable <= 0;

ch16_prn_key_enable <= 0;

ch16_slew_enable <= 0;

ch16_epoch_enable <= 0;

ch17_prn_key_enable <= 0;

ch17_slew_enable <= 0;

ch17_epoch_enable <= 0;

ch18_prn_key_enable <= 0;

ch18_slew_enable <= 0;

ch18_epoch_enable <= 0;

ch19_prn_key_enable <= 0;

ch19_slew_enable <= 0;

ch19_epoch_enable <= 0;

tic_delay_enable <= 0;

pps_tic_enable <= 0;

case (address)

// channel 0

9'h000 : begin

ch0_prn_key_enable <= write & chip_select;

if (write & chip_select) ch0_prn_key <= write_data[9:0];

end

9'h001 : if (write & chip_select) ch0_carr_nco <= write_data[28:0];

9'h002 : if (write & chip_select) ch0_code_nco <= write_data[27:0];

9'h003 : begin

ch0_slew_enable <= write & chip_select;

if (write & chip_select) ch0_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h004 : read_data <= ch0_i_early;

9'h005 : read_data <= ch0_q_early;

9'h006 : read_data <= ch0_i_prompt;

9'h007 : read_data <= ch0_q_prompt;

9'h008 : read_data <= ch0_i_late;

9'h009 : read_data <= ch0_q_late;

`else

9'h004 : read_data <= {16'h0, ch0_i_early};

9'h005 : read_data <= {16'h0, ch0_q_early};

9'h006 : read_data <= {16'h0, ch0_i_prompt};

9'h007 : read_data <= {16'h0, ch0_q_prompt};

9'h008 : read_data <= {16'h0, ch0_i_late};

9'h009 : read_data <= {16'h0, ch0_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h00A : read_data <= ch0_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h00B : read_data <= {11'h0, ch0_code_val}; // 21 bits

9'h00C : read_data <= {21'h0, ch0_epoch}; // 11 bits

9'h00D : read_data <= {21'h0, ch0_epoch_check}; // 11 bits

9'h00E : begin

ch0_epoch_enable <= write & chip_select;

if (write & chip_select) ch0_epoch_load <= write_data[10:0];

end

// channel 1

9'h010 : begin

ch1_prn_key_enable <= write & chip_select;

if (write & chip_select) ch1_prn_key <= write_data[9:0];

end

9'h011 : if (write & chip_select) ch1_carr_nco <= write_data[28:0];

9'h012 : if (write & chip_select) ch1_code_nco <= write_data[27:0];

9'h013 : begin

ch1_slew_enable <= write & chip_select;

if (write & chip_select) ch1_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h014 : read_data <= ch1_i_early;

9'h015 : read_data <= ch1_q_early;

9'h016 : read_data <= ch1_i_prompt;

9'h017 : read_data <= ch1_q_prompt;

9'h018 : read_data <= ch1_i_late;

9'h019 : read_data <= ch1_q_late;

`else

9'h014 : read_data <= {16'h0, ch1_i_early};

9'h015 : read_data <= {16'h0, ch1_q_early};

9'h016 : read_data <= {16'h0, ch1_i_prompt};

9'h017 : read_data <= {16'h0, ch1_q_prompt};

9'h018 : read_data <= {16'h0, ch1_i_late};

9'h019 : read_data <= {16'h0, ch1_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h01A : read_data <= ch1_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h01B : read_data <= {11'h0, ch1_code_val}; // 21 bits

9'h01C : read_data <= {21'h0, ch1_epoch}; // 11 bits

9'h01D : read_data <= {21'h0, ch1_epoch_check};

9'h01E : begin

ch1_epoch_enable <= write & chip_select;

if (write & chip_select) ch1_epoch_load <= write_data[10:0];

end

// channel 2

9'h020 : begin

ch2_prn_key_enable <= write & chip_select;

if (write & chip_select) ch2_prn_key <= write_data[9:0];

end

9'h021 : if (write & chip_select) ch2_carr_nco <= write_data[28:0];

9'h022 : if (write & chip_select) ch2_code_nco <= write_data[27:0];

9'h023 : begin

ch2_slew_enable <= write & chip_select;

if (write & chip_select) ch2_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h024 : read_data <= ch2_i_early;

9'h025 : read_data <= ch2_q_early;

9'h026 : read_data <= ch2_i_prompt;

9'h027 : read_data <= ch2_q_prompt;

9'h028 : read_data <= ch2_i_late;

9'h029 : read_data <= ch2_q_late;

`else

9'h024 : read_data <= {16'h0, ch2_i_early};

9'h025 : read_data <= {16'h0, ch2_q_early};

9'h026 : read_data <= {16'h0, ch2_i_prompt};

9'h027 : read_data <= {16'h0, ch2_q_prompt};

9'h028 : read_data <= {16'h0, ch2_i_late};

9'h029 : read_data <= {16'h0, ch2_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h02A : read_data <= ch2_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h02B : read_data <= {11'h0, ch2_code_val}; // 21 bits

9'h02C : read_data <= {21'h0, ch2_epoch}; // 11 bits

9'h02D : read_data <= {21'h0, ch2_epoch_check};

9'h02E : begin

ch2_epoch_enable <= write & chip_select;

if (write & chip_select) ch2_epoch_load <= write_data[10:0];

end

// channel 3

9'h030 : begin

ch3_prn_key_enable <= write & chip_select;

if (write & chip_select) ch3_prn_key <= write_data[9:0];

end

9'h031 : if (write & chip_select) ch3_carr_nco <= write_data[28:0];

9'h032 : if (write & chip_select) ch3_code_nco <= write_data[27:0];

9'h033 : begin

ch3_slew_enable <= write & chip_select;

if (write & chip_select) ch3_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h034 : read_data <= ch3_i_early;

9'h035 : read_data <= ch3_q_early;

9'h036 : read_data <= ch3_i_prompt;

9'h037 : read_data <= ch3_q_prompt;

9'h038 : read_data <= ch3_i_late;

9'h039 : read_data <= ch3_q_late;

`else

9'h034 : read_data <= {16'h0, ch3_i_early};

9'h035 : read_data <= {16'h0, ch3_q_early};

9'h036 : read_data <= {16'h0, ch3_i_prompt};

9'h037 : read_data <= {16'h0, ch3_q_prompt};

9'h038 : read_data <= {16'h0, ch3_i_late};

9'h039 : read_data <= {16'h0, ch3_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h03A : read_data <= ch3_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h03B : read_data <= {11'h0, ch3_code_val}; // 21 bits

9'h03C : read_data <= {21'h0, ch3_epoch}; // 11 bits

9'h03D : read_data <= {21'h0, ch3_epoch_check};

9'h03E : begin

ch3_epoch_enable <= write & chip_select;

if (write & chip_select) ch3_epoch_load <= write_data[10:0];

end

// channel 4

9'h040 : begin

ch4_prn_key_enable <= write & chip_select;

if (write & chip_select) ch4_prn_key <= write_data[9:0];

end

9'h041 : if (write & chip_select) ch4_carr_nco <= write_data[28:0];

9'h042 : if (write & chip_select) ch4_code_nco <= write_data[27:0];

9'h043 : begin

ch4_slew_enable <= write & chip_select;

if (write & chip_select) ch4_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h044 : read_data <= ch4_i_early;

9'h045 : read_data <= ch4_q_early;

9'h046 : read_data <= ch4_i_prompt;

9'h047 : read_data <= ch4_q_prompt;

9'h048 : read_data <= ch4_i_late;

9'h049 : read_data <= ch4_q_late;

`else

9'h044 : read_data <= {16'h0, ch4_i_early};

9'h045 : read_data <= {16'h0, ch4_q_early};

9'h046 : read_data <= {16'h0, ch4_i_prompt};

9'h047 : read_data <= {16'h0, ch4_q_prompt};

9'h048 : read_data <= {16'h0, ch4_i_late};

9'h049 : read_data <= {16'h0, ch4_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h04A : read_data <= ch4_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h04B : read_data <= {11'h0, ch4_code_val}; // 21 bits

9'h04C : read_data <= {21'h0, ch4_epoch}; // 11 bits

9'h04D : read_data <= {21'h0, ch4_epoch_check};

9'h04E : begin

ch4_epoch_enable <= write & chip_select;

if (write & chip_select) ch4_epoch_load <= write_data[10:0];

end

// channel 5

9'h050 : begin

ch5_prn_key_enable <= write & chip_select;

if (write & chip_select) ch5_prn_key <= write_data[9:0];

end

9'h051 : if (write & chip_select) ch5_carr_nco <= write_data[28:0];

9'h052 : if (write & chip_select) ch5_code_nco <= write_data[27:0];

9'h053 : begin

ch5_slew_enable <= write & chip_select;

if (write & chip_select) ch5_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h054 : read_data <= ch5_i_early;

9'h055 : read_data <= ch5_q_early;

9'h056 : read_data <= ch5_i_prompt;

9'h057 : read_data <= ch5_q_prompt;

9'h058 : read_data <= ch5_i_late;

9'h059 : read_data <= ch5_q_late;

`else

9'h054 : read_data <= {16'h0, ch5_i_early};

9'h055 : read_data <= {16'h0, ch5_q_early};

9'h056 : read_data <= {16'h0, ch5_i_prompt};

9'h057 : read_data <= {16'h0, ch5_q_prompt};

9'h058 : read_data <= {16'h0, ch5_i_late};

9'h059 : read_data <= {16'h0, ch5_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h05A : read_data <= ch5_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h05B : read_data <= {11'h0, ch5_code_val}; // 21 bits

9'h05C : read_data <= {21'h0, ch5_epoch}; // 11 bits

9'h05D : read_data <= {21'h0, ch5_epoch_check};

9'h05E : begin

ch5_epoch_enable <= write & chip_select;

if (write & chip_select) ch5_epoch_load <= write_data[10:0];

end

// channel 6

9'h060 : begin

ch6_prn_key_enable <= write & chip_select;

if (write & chip_select) ch6_prn_key <= write_data[9:0];

end

9'h061 : if (write & chip_select) ch6_carr_nco <= write_data[28:0];

9'h062 : if (write & chip_select) ch6_code_nco <= write_data[27:0];

9'h063 : begin

ch6_slew_enable <= write & chip_select;

if (write & chip_select) ch6_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h064 : read_data <= ch6_i_early;

9'h065 : read_data <= ch6_q_early;

9'h066 : read_data <= ch6_i_prompt;

9'h067 : read_data <= ch6_q_prompt;

9'h068 : read_data <= ch6_i_late;

9'h069 : read_data <= ch6_q_late;

`else

9'h064 : read_data <= {16'h0, ch6_i_early};

9'h065 : read_data <= {16'h0, ch6_q_early};

9'h066 : read_data <= {16'h0, ch6_i_prompt};

9'h067 : read_data <= {16'h0, ch6_q_prompt};

9'h068 : read_data <= {16'h0, ch6_i_late};

9'h069 : read_data <= {16'h0, ch6_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h06A : read_data <= ch6_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h06B : read_data <= {11'h0, ch6_code_val}; // 21 bits

9'h06C : read_data <= {21'h0, ch6_epoch}; // 11 bits

9'h06D : read_data <= {21'h0, ch6_epoch_check};

9'h06E : begin

ch6_epoch_enable <= write & chip_select;

if (write & chip_select) ch6_epoch_load <= write_data[10:0];

end

// channel 7

9'h070 : begin

ch7_prn_key_enable <= write & chip_select;

if (write & chip_select) ch7_prn_key <= write_data[9:0];

end

9'h071 : if (write & chip_select) ch7_carr_nco <= write_data[28:0];

9'h072 : if (write & chip_select) ch7_code_nco <= write_data[27:0];

9'h073 : begin

ch7_slew_enable <= write & chip_select;

if (write & chip_select) ch7_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h074 : read_data <= ch7_i_early;

9'h075 : read_data <= ch7_q_early;

9'h076 : read_data <= ch7_i_prompt;

9'h077 : read_data <= ch7_q_prompt;

9'h078 : read_data <= ch7_i_late;

9'h079 : read_data <= ch7_q_late;

`else

9'h074 : read_data <= {16'h0, ch7_i_early};

9'h075 : read_data <= {16'h0, ch7_q_early};

9'h076 : read_data <= {16'h0, ch7_i_prompt};

9'h077 : read_data <= {16'h0, ch7_q_prompt};

9'h078 : read_data <= {16'h0, ch7_i_late};

9'h079 : read_data <= {16'h0, ch7_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h07A : read_data <= ch7_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h07B : read_data <= {11'h0, ch7_code_val}; // 21 bits

9'h07C : read_data <= {21'h0, ch7_epoch}; // 11 bits

9'h07D : read_data <= {21'h0, ch7_epoch_check};

9'h07E : begin

ch7_epoch_enable <= write & chip_select;

if (write & chip_select) ch7_epoch_load <= write_data[10:0];

end

// channel 8

9'h080 : begin

ch8_prn_key_enable <= write & chip_select;

if (write & chip_select) ch8_prn_key <= write_data[9:0];

end

9'h081 : if (write & chip_select) ch8_carr_nco <= write_data[28:0];

9'h082 : if (write & chip_select) ch8_code_nco <= write_data[27:0];

9'h083 : begin

ch8_slew_enable <= write & chip_select;

if (write & chip_select) ch8_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h084 : read_data <= ch8_i_early;

9'h085 : read_data <= ch8_q_early;

9'h086 : read_data <= ch8_i_prompt;

9'h087 : read_data <= ch8_q_prompt;

9'h088 : read_data <= ch8_i_late;

9'h089 : read_data <= ch8_q_late;

`else

9'h084 : read_data <= {16'h0, ch8_i_early};

9'h085 : read_data <= {16'h0, ch8_q_early};

9'h086 : read_data <= {16'h0, ch8_i_prompt};

9'h087 : read_data <= {16'h0, ch8_q_prompt};

9'h088 : read_data <= {16'h0, ch8_i_late};

9'h089 : read_data <= {16'h0, ch8_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h08A : read_data <= ch8_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h08B : read_data <= {11'h0, ch8_code_val}; // 21 bits

9'h08C : read_data <= {21'h0, ch8_epoch}; // 11 bits

9'h08D : read_data <= {21'h0, ch8_epoch_check};

9'h08E : begin

ch8_epoch_enable <= write & chip_select;

if (write & chip_select) ch8_epoch_load <= write_data[10:0];

end

// channel 9

9'h090 : begin

ch9_prn_key_enable <= write & chip_select;

if (write & chip_select) ch9_prn_key <= write_data[9:0];

end

9'h091 : if (write & chip_select) ch9_carr_nco <= write_data[28:0];

9'h092 : if (write & chip_select) ch9_code_nco <= write_data[27:0];

9'h093 : begin

ch9_slew_enable <= write & chip_select;

if (write & chip_select) ch9_code_slew <= write_data[10:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h094 : read_data <= ch9_i_early;

9'h095 : read_data <= ch9_q_early;

9'h096 : read_data <= ch9_i_prompt;

9'h097 : read_data <= ch9_q_prompt;

9'h098 : read_data <= ch9_i_late;

9'h099 : read_data <= ch9_q_late;

`else

9'h094 : read_data <= {16'h0, ch9_i_early};

9'h095 : read_data <= {16'h0, ch9_q_early};

9'h096 : read_data <= {16'h0, ch9_i_prompt};

9'h097 : read_data <= {16'h0, ch9_q_prompt};

9'h098 : read_data <= {16'h0, ch9_i_late};

9'h099 : read_data <= {16'h0, ch9_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h09A : read_data <= ch9_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h09B : read_data <= {11'h0, ch9_code_val}; // 21 bits

9'h09C : read_data <= {21'h0, ch9_epoch}; // 11 bits

9'h09D : read_data <= {21'h0, ch9_epoch_check};

9'h09E : begin

ch9_epoch_enable <= write & chip_select;

if (write & chip_select) ch9_epoch_load <= write_data[10:0];

end

// status

9'h0E0 : begin // get status and pulse status_flag to clear status

read_data <= {30'h0, status}; // only 2 status bits, therefore need to pad 29ms bits

status_read <= read & chip_select; // pulse status flag to clear status register

end

9'h0E1 : begin // get new_data

read_data <= {12'h0,new_data}; // one new_data bit per channel, need to pad other bits

// pulse the new data flag to clear new_data register

new_data_read <= read & chip_select;

// make sure the flag is not cleared if a dump is aligned to new_data_read

dump_mask[0] <= ch0_dump;

dump_mask[1] <= ch1_dump;

dump_mask[2] <= ch2_dump;

dump_mask[3] <= ch3_dump;

dump_mask[4] <= ch4_dump;

dump_mask[5] <= ch5_dump;

dump_mask[6] <= ch6_dump;

dump_mask[7] <= ch7_dump;

dump_mask[8] <= ch8_dump;

dump_mask[9] <= ch9_dump;

dump_mask[10] <= ch10_dump;

dump_mask[11] <= ch11_dump;

dump_mask[12] <= ch12_dump;

dump_mask[13] <= ch13_dump;

dump_mask[14] <= ch14_dump;

dump_mask[15] <= ch15_dump;

dump_mask[16] <= ch16_dump;

dump_mask[17] <= ch17_dump;

dump_mask[18] <= ch18_dump;

dump_mask[19] <= ch19_dump;

end

9'h0E2 : begin // PPS tic count read

read_data <= {28'h0,pps_tic_count}; // 4 bits of TIC count

end

// control

9'h0F0 : sw_rst <= write & chip_select; // software reset

9'h0F1 : if (write & chip_select) prog_tic_div <= write_data[24:0]; // program TIC

9'h0F2 : if (write & chip_select) prog_accum_int <= write_data[17:0]; // program ACCUM_INT

9'h0F3 : if (write & chip_select) prog_pps_div <= write_data[17:0]; // program PPS

9'h0F4 : begin

tic_delay_enable <= write & chip_select;

if (write & chip_select) tic_delay_value <= write_data[31:0];

end

9'h0F5 : begin

pps_tic_enable <= write & chip_select;

if (write & chip_select) pps_tic_load <= write_data[3:0];

end

// channel 10

9'h100 : begin

ch10_prn_key_enable <= write & chip_select;

if (write & chip_select) ch10_prn_key <= write_data[10:0];

end

9'h101 : if (write & chip_select) ch10_carr_nco <= write_data[28:0];

9'h102 : if (write & chip_select) ch10_code_nco <= write_data[27:0];

9'h103 : begin

ch10_slew_enable <= write & chip_select;

if (write & chip_select) ch10_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h104 : read_data <= ch10_i_early;

9'h105 : read_data <= ch10_q_early;

9'h106 : read_data <= ch10_i_prompt;

9'h107 : read_data <= ch10_q_prompt;

9'h108 : read_data <= ch10_i_late;

9'h109 : read_data <= ch10_q_late;

`else

9'h104 : read_data <= {16'h0, ch10_i_early};

9'h105 : read_data <= {16'h0, ch10_q_early};

9'h106 : read_data <= {16'h0, ch10_i_prompt};

9'h107 : read_data <= {16'h0, ch10_q_prompt};

9'h108 : read_data <= {16'h0, ch10_i_late};

9'h109 : read_data <= {16'h0, ch10_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h10A : read_data <= ch10_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h10B : read_data <= {9'h0, ch10_code_val}; // 23 bits

9'h10C : read_data <= {21'h0, ch10_epoch}; // 11 bits

9'h10D : read_data <= {21'h0, ch10_epoch_check}; // 11 bits

9'h10E : begin

ch10_epoch_enable <= write & chip_select;

if (write & chip_select) ch10_epoch_load <= write_data[10:0];

end

// channel 11

9'h110 : begin

ch11_prn_key_enable <= write & chip_select;

if (write & chip_select) ch11_prn_key <= write_data[10:0];

end

9'h111 : if (write & chip_select) ch11_carr_nco <= write_data[28:0];

9'h112 : if (write & chip_select) ch11_code_nco <= write_data[27:0];

9'h113 : begin

ch11_slew_enable <= write & chip_select;

if (write & chip_select) ch11_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h114 : read_data <= ch11_i_early;

9'h115 : read_data <= ch11_q_early;

9'h116 : read_data <= ch11_i_prompt;

9'h117 : read_data <= ch11_q_prompt;

9'h118 : read_data <= ch11_i_late;

9'h119 : read_data <= ch11_q_late;

`else

9'h114 : read_data <= {16'h0, ch11_i_early};

9'h115 : read_data <= {16'h0, ch11_q_early};

9'h116 : read_data <= {16'h0, ch11_i_prompt};

9'h117 : read_data <= {16'h0, ch11_q_prompt};

9'h118 : read_data <= {16'h0, ch11_i_late};

9'h119 : read_data <= {16'h0, ch11_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h11A : read_data <= ch11_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h11B : read_data <= {9'h0, ch11_code_val}; // 23 bits

9'h11C : read_data <= {21'h0, ch11_epoch}; // 11 bits

9'h11D : read_data <= {21'h0, ch11_epoch_check};

9'h11E : begin

ch11_epoch_enable <= write & chip_select;

if (write & chip_select) ch11_epoch_load <= write_data[10:0];

end

// channel 12

9'h120 : begin

ch12_prn_key_enable <= write & chip_select;

if (write & chip_select) ch12_prn_key <= write_data[10:0];

end

9'h121 : if (write & chip_select) ch12_carr_nco <= write_data[28:0];

9'h122 : if (write & chip_select) ch12_code_nco <= write_data[27:0];

9'h123 : begin

ch12_slew_enable <= write & chip_select;

if (write & chip_select) ch12_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h124 : read_data <= ch12_i_early;

9'h125 : read_data <= ch12_q_early;

9'h126 : read_data <= ch12_i_prompt;

9'h127 : read_data <= ch12_q_prompt;

9'h128 : read_data <= ch12_i_late;

9'h129 : read_data <= ch12_q_late;

`else

9'h124 : read_data <= {16'h0, ch12_i_early};

9'h125 : read_data <= {16'h0, ch12_q_early};

9'h126 : read_data <= {16'h0, ch12_i_prompt};

9'h127 : read_data <= {16'h0, ch12_q_prompt};

9'h128 : read_data <= {16'h0, ch12_i_late};

9'h129 : read_data <= {16'h0, ch12_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h12A : read_data <= ch12_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h12B : read_data <= {9'h0, ch12_code_val}; // 23 bits

9'h12C : read_data <= {21'h0, ch12_epoch}; // 11 bits

9'h12D : read_data <= {21'h0, ch12_epoch_check};

9'h12E : begin

ch12_epoch_enable <= write & chip_select;

if (write & chip_select) ch12_epoch_load <= write_data[10:0];

end

// channel 13

9'h130 : begin

ch13_prn_key_enable <= write & chip_select;

if (write & chip_select) ch13_prn_key <= write_data[10:0];

end

9'h131 : if (write & chip_select) ch13_carr_nco <= write_data[28:0];

9'h132 : if (write & chip_select) ch13_code_nco <= write_data[27:0];

9'h133 : begin

ch13_slew_enable <= write & chip_select;

if (write & chip_select) ch13_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h134 : read_data <= ch13_i_early;

9'h135 : read_data <= ch13_q_early;

9'h136 : read_data <= ch13_i_prompt;

9'h137 : read_data <= ch13_q_prompt;

9'h138 : read_data <= ch13_i_late;

9'h139 : read_data <= ch13_q_late;

`else

9'h134 : read_data <= {16'h0, ch13_i_early};

9'h135 : read_data <= {16'h0, ch13_q_early};

9'h136 : read_data <= {16'h0, ch13_i_prompt};

9'h137 : read_data <= {16'h0, ch13_q_prompt};

9'h138 : read_data <= {16'h0, ch13_i_late};

9'h139 : read_data <= {16'h0, ch13_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h13A : read_data <= ch13_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h13B : read_data <= {9'h0, ch13_code_val}; // 23 bits

9'h13C : read_data <= {21'h0, ch13_epoch}; // 11 bits

9'h13D : read_data <= {21'h0, ch13_epoch_check};

9'h13E : begin

ch13_epoch_enable <= write & chip_select;

if (write & chip_select) ch13_epoch_load <= write_data[10:0];

end

// channel 14

9'h140 : begin

ch14_prn_key_enable <= write & chip_select;

if (write & chip_select) ch14_prn_key <= write_data[10:0];

end

9'h141 : if (write & chip_select) ch14_carr_nco <= write_data[28:0];

9'h142 : if (write & chip_select) ch14_code_nco <= write_data[27:0];

9'h143 : begin

ch14_slew_enable <= write & chip_select;

if (write & chip_select) ch14_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h144 : read_data <= ch14_i_early;

9'h145 : read_data <= ch14_q_early;

9'h146 : read_data <= ch14_i_prompt;

9'h147 : read_data <= ch14_q_prompt;

9'h148 : read_data <= ch14_i_late;

9'h149 : read_data <= ch14_q_late;

`else

9'h144 : read_data <= {16'h0, ch14_i_early};

9'h145 : read_data <= {16'h0, ch14_q_early};

9'h146 : read_data <= {16'h0, ch14_i_prompt};

9'h147 : read_data <= {16'h0, ch14_q_prompt};

9'h148 : read_data <= {16'h0, ch14_i_late};

9'h149 : read_data <= {16'h0, ch14_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h14A : read_data <= ch14_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h14B : read_data <= {9'h0, ch14_code_val}; // 23 bits

9'h14C : read_data <= {21'h0, ch14_epoch}; // 11 bits

9'h14D : read_data <= {21'h0, ch14_epoch_check};

9'h14E : begin

ch14_epoch_enable <= write & chip_select;

if (write & chip_select) ch14_epoch_load <= write_data[10:0];

end

// channel 15

9'h150 : begin

ch15_prn_key_enable <= write & chip_select;

if (write & chip_select) ch15_prn_key <= write_data[10:0];

end

9'h151 : if (write & chip_select) ch15_carr_nco <= write_data[28:0];

9'h152 : if (write & chip_select) ch15_code_nco <= write_data[27:0];

9'h153 : begin

ch15_slew_enable <= write & chip_select;

if (write & chip_select) ch15_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h154 : read_data <= ch15_i_early;

9'h155 : read_data <= ch15_q_early;

9'h156 : read_data <= ch15_i_prompt;

9'h157 : read_data <= ch15_q_prompt;

9'h158 : read_data <= ch15_i_late;

9'h159 : read_data <= ch15_q_late;

`else

9'h154 : read_data <= {16'h0, ch15_i_early};

9'h155 : read_data <= {16'h0, ch15_q_early};

9'h156 : read_data <= {16'h0, ch15_i_prompt};

9'h157 : read_data <= {16'h0, ch15_q_prompt};

9'h158 : read_data <= {16'h0, ch15_i_late};

9'h159 : read_data <= {16'h0, ch15_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h15A : read_data <= ch15_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h15B : read_data <= {9'h0, ch15_code_val}; // 23 bits

9'h15C : read_data <= {21'h0, ch15_epoch}; // 11 bits

9'h15D : read_data <= {21'h0, ch15_epoch_check};

9'h15E : begin

ch15_epoch_enable <= write & chip_select;

if (write & chip_select) ch15_epoch_load <= write_data[10:0];

end

// channel 16

9'h160 : begin

ch16_prn_key_enable <= write & chip_select;

if (write & chip_select) ch16_prn_key <= write_data[10:0];

end

9'h161 : if (write & chip_select) ch16_carr_nco <= write_data[28:0];

9'h162 : if (write & chip_select) ch16_code_nco <= write_data[27:0];

9'h163 : begin

ch16_slew_enable <= write & chip_select;

if (write & chip_select) ch16_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h164 : read_data <= ch16_i_early;

9'h165 : read_data <= ch16_q_early;

9'h166 : read_data <= ch16_i_prompt;

9'h167 : read_data <= ch16_q_prompt;

9'h168 : read_data <= ch16_i_late;

9'h169 : read_data <= ch16_q_late;

`else

9'h164 : read_data <= {16'h0, ch16_i_early};

9'h165 : read_data <= {16'h0, ch16_q_early};

9'h166 : read_data <= {16'h0, ch16_i_prompt};

9'h167 : read_data <= {16'h0, ch16_q_prompt};

9'h168 : read_data <= {16'h0, ch16_i_late};

9'h169 : read_data <= {16'h0, ch16_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h16A : read_data <= ch16_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h16B : read_data <= {9'h0, ch16_code_val}; // 23 bits

9'h16C : read_data <= {21'h0, ch16_epoch}; // 11 bits

9'h16D : read_data <= {21'h0, ch16_epoch_check};

9'h16E : begin

ch16_epoch_enable <= write & chip_select;

if (write & chip_select) ch16_epoch_load <= write_data[10:0];

end

// channel 17

9'h170 : begin

ch17_prn_key_enable <= write & chip_select;

if (write & chip_select) ch17_prn_key <= write_data[10:0];

end

9'h171 : if (write & chip_select) ch17_carr_nco <= write_data[28:0];

9'h172 : if (write & chip_select) ch17_code_nco <= write_data[27:0];

9'h173 : begin

ch17_slew_enable <= write & chip_select;

if (write & chip_select) ch17_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h174 : read_data <= ch17_i_early;

9'h175 : read_data <= ch17_q_early;

9'h176 : read_data <= ch17_i_prompt;

9'h177 : read_data <= ch17_q_prompt;

9'h178 : read_data <= ch17_i_late;

9'h179 : read_data <= ch17_q_late;

`else

9'h174 : read_data <= {16'h0, ch17_i_early};

9'h175 : read_data <= {16'h0, ch17_q_early};

9'h176 : read_data <= {16'h0, ch17_i_prompt};

9'h177 : read_data <= {16'h0, ch17_q_prompt};

9'h178 : read_data <= {16'h0, ch17_i_late};

9'h179 : read_data <= {16'h0, ch17_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h17A : read_data <= ch17_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h17B : read_data <= {9'h0, ch17_code_val}; // 23 bits

9'h17C : read_data <= {21'h0, ch17_epoch}; // 11 bits

9'h17D : read_data <= {21'h0, ch17_epoch_check};

9'h17E : begin

ch17_epoch_enable <= write & chip_select;

if (write & chip_select) ch17_epoch_load <= write_data[10:0];

end

// channel 18

9'h180 : begin

ch18_prn_key_enable <= write & chip_select;

if (write & chip_select) ch18_prn_key <= write_data[10:0];

end

9'h181 : if (write & chip_select) ch18_carr_nco <= write_data[28:0];

9'h182 : if (write & chip_select) ch18_code_nco <= write_data[27:0];

9'h183 : begin

ch18_slew_enable <= write & chip_select;

if (write & chip_select) ch18_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h184 : read_data <= ch18_i_early;

9'h185 : read_data <= ch18_q_early;

9'h186 : read_data <= ch18_i_prompt;

9'h187 : read_data <= ch18_q_prompt;

9'h188 : read_data <= ch18_i_late;

9'h189 : read_data <= ch18_q_late;

`else

9'h184 : read_data <= {16'h0, ch18_i_early};

9'h185 : read_data <= {16'h0, ch18_q_early};

9'h186 : read_data <= {16'h0, ch18_i_prompt};

9'h187 : read_data <= {16'h0, ch18_q_prompt};

9'h188 : read_data <= {16'h0, ch18_i_late};

9'h189 : read_data <= {16'h0, ch18_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h18A : read_data <= ch18_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h18B : read_data <= {9'h0, ch18_code_val}; // 23 bits

9'h18C : read_data <= {21'h0, ch18_epoch}; // 11 bits

9'h18D : read_data <= {21'h0, ch18_epoch_check};

9'h18E : begin

ch18_epoch_enable <= write & chip_select;

if (write & chip_select) ch18_epoch_load <= write_data[10:0];

end

// channel 19

9'h190 : begin

ch19_prn_key_enable <= write & chip_select;

if (write & chip_select) ch19_prn_key <= write_data[10:0];

end

9'h191 : if (write & chip_select) ch19_carr_nco <= write_data[28:0];

9'h192 : if (write & chip_select) ch19_code_nco <= write_data[27:0];

9'h193 : begin

ch19_slew_enable <= write & chip_select;

if (write & chip_select) ch19_code_slew <= write_data[11:0];

end

`ifdef ENABLE_32BIT_ACCUMULATOR

9'h194 : read_data <= ch19_i_early;

9'h195 : read_data <= ch19_q_early;

9'h196 : read_data <= ch19_i_prompt;

9'h197 : read_data <= ch19_q_prompt;

9'h198 : read_data <= ch19_i_late;

9'h199 : read_data <= ch19_q_late;

`else

9'h194 : read_data <= {16'h0, ch19_i_early};

9'h195 : read_data <= {16'h0, ch19_q_early};

9'h196 : read_data <= {16'h0, ch19_i_prompt};

9'h197 : read_data <= {16'h0, ch19_q_prompt};

9'h198 : read_data <= {16'h0, ch19_i_late};

9'h199 : read_data <= {16'h0, ch19_q_late};

`endif

`ifdef ENABLE_CARRIER_PHASE_MEASUREMENT

9'h19A : read_data <= ch19_carrier_val; // 32 bits

`endif // ENABLE_CARRIER_PHASE_MEASUREMENT

9'h19B : read_data <= {9'h0, ch19_code_val}; // 23 bits

9'h19C : read_data <= {21'h0, ch19_epoch}; // 11 bits

9'h19D : read_data <= {21'h0, ch19_epoch_check};

9'h19E : begin

ch19_epoch_enable <= write & chip_select;

if (write & chip_select) ch19_epoch_load <= write_data[10:0];

end

default : read_data <= 0;

endcase // case(address)

end

end

// process to create a two clk wide dump_mask pulse

always @ (posedge clk)

begin

if (!rstn)

dump_mask_2 <= 0;

else

dump_mask_2 <= dump_mask;

end

// process to reset the status register after a read

// also create accum_int signal that is cleared after status read

always @ (posedge clk)

begin

if (!rstn || status_read)

begin

status <= 0;

accum_int <= 0;

end

else

begin

if (tic_enable)

begin

status[0] <= 1;

end

if (accum_enable_s)

begin

status[1] <= 1;

accum_int <= 1;

end

end

end

// process to reset the new_data register after a read

// set new data bits when channel dumps occur

always @ (posedge clk)

begin

if (!rstn || new_data_read)

begin

new_data <= dump_mask | dump_mask_2;

end

else

begin

if (ch0_dump)

new_data[0] <= 1;

if (ch1_dump)

new_data[1] <= 1;

if (ch2_dump)

new_data[2] <= 1;

if (ch3_dump)

new_data[3] <= 1;

if (ch4_dump)

new_data[4] <= 1;

if (ch5_dump)

new_data[5] <= 1;

if (ch6_dump)

new_data[6] <= 1;

if (ch7_dump)

new_data[7] <= 1;

if (ch8_dump)

new_data[8] <= 1;

if (ch9_dump)

new_data[9] <= 1;

if (ch10_dump)

new_data[10] <= 1;

if (ch11_dump)

new_data[11] <= 1;

if (ch12_dump)

new_data[12] <= 1;

if (ch13_dump)

new_data[13] <= 1;

if (ch14_dump)

new_data[14] <= 1;

if (ch15_dump)

new_data[15] <= 1;

if (ch16_dump)

new_data[16] <= 1;

if (ch17_dump)

new_data[17] <= 1;

if (ch18_dump)

new_data[18] <= 1;

if (ch19_dump)

new_data[19] <= 1;

end // else: !if(!rstn || new_data_read)

end // always @ (posedge clk)