PS(处理器子系统)内部的互联结构包含了多个交换机,用于通过AXI点对点通道连接系统资源。这些通道负责在主机和从机客户端之间进行地址、数据和响应事务通信。该互联结构负责管理多个待处理的事务,并且为Arm CPU设计了低延迟路径,同时为PL(可编程逻辑)主控制器提供了高吞吐量和缓存一致的数据路径。

简单来说,这种互联结构在处理器子系统中起到了桥梁作用,它确保了各种系统资源之间的高效通信,并且针对不同的使用场景(如CPU或PL主控制器)进行了优化,以提供最佳的性能和效率。

1 互联

互联作为数据通信的主要机制,具有一系列关键特性。

1.1 互联是基于AXI高性能数据通道交换机

①Snoop控制单元(SCU)

Zynq系列器件中的SCU的地址过滤功能允许它根据地址信息来选择性地转发数据。当数据从AXI从端口流入时,SCU会检查数据的地址,并根据预设的规则或配置来决定是否将数据转发到AXI主端口。这有助于维护缓存一致性,确保不同处理器或设备访问同一内存位置时数据的正确性。

②L2缓存控制器

Zynq系列器件中L2缓存控制器的一个重要特性是其地址过滤功能。这一功能使得L2缓存控制器在从它的AXI从端口到AXI主端口的流量传输上表现得像一个开关。具体来说,当CPU需要访问某个数据时,L2缓存控制器会首先检查这个数据的地址是否在L2缓存中。如果地址匹配,控制器就会直接从L2缓存中读取数据并送给CPU处理,从而避免了从主内存中读取数据的较慢过程。如果地址不匹配,即数据不在L2缓存中,控制器则会从主内存中读取数据,并同时将这个数据块调入L2缓存中,以便后续的快速访问。

因此,L2缓存控制器管理L2缓存的访问和操作,优化数据访问速度,减少处理器对主存的依赖。

1.2 基于Arm NIC-301的互联交换机

①中央互联

作为整个系统的中心,连接和管理所有其他互联。

②对从设备的主互联

为从设备(如存储器或外设)提供与主设备(如处理器)的通信通道。

负责将来自中央互联的低速到中速流量切换到M_AXI_GP端口、I/O外设(IOP)以及其他块。它起到一个桥梁的作用,将中央互联与这些目标端口和组件连接起来,实现数据的传输和共享。

③对主设备的从互联

允许主设备(如处理器)与从设备(如存储器或外设)进行通信。

从互联侧将来自S_AXI_GP端口、DevC和DAP的低速到中速流量切换到中央互联。与主互联类似,从互联也扮演着桥梁的角色,将数据从源端口和组件传输到中央互联,进而实现与其他部分的通信。

④存储器互联

优化对存储器的访问,提高数据传输效率。

负责将来自AXI_HP端口的高速流量切换到DDR DRAM和片上RAM(通过另一个互联)。作为系统内存访问的关键通道,内存互联确保了处理器和其他主设备能够高效、快速地访问DDR DRAM和片上RAM中的数据。

⑤OCM互联

针对片上存储器(OCM)的特定优化互联。

负责将来自中央互联和内存互联的高速流量进行切换。OCM(片上存储器)是一种集成在处理器或系统芯片上的高速存储器,用于存储关键数据和指令,以加快访问速度。

⑥AHB和APB桥

允许AXI接口与其他总线标准(如AHB和APB)进行互操作。

1.3 PS-PL接口

PS-PL接口在Zynq-7000 SoC中扮演着连接处理系统(PS)和可编程逻辑(PL)的关键角色。具体来说,PS-PL接口包括多个信号线,用于实现PS和PL之间的数据传输、共享内存、中断控制等功能。

PS和PL之间通过多个AXI接口实现连接。这些AXI接口包括:

①加速器一致性端口(AXI_ACP)

在PL中的一个缓存一致从端口,连接到PS APU的一致性从端口,确保处理器和加速器之间的缓存数据一致性。

AXI_ACP为可编程逻辑主机提供了低延迟访问,并与L1和L2高速缓存具有可选一致性。从系统角度来看,ACP接口与APU CPU的连接性相似。由于这种紧密的连通性,在APU块之外,ACP直接参与资源竞争。

②AXI_HP

在PL中的四个高性能、高带宽从端口,它们在PS AXI互联上成为主端口,用于处理大量或高优先级的数据传输。

AXI_HP接口提供了PL(可编程逻辑)总线主设备到DDR和OCM(片上存储器)的高带宽数据路径。每个AXI_HP接口都包括两个FIFO缓冲区,分别用于读写流量。PL到存储器的互连将高速AXI_HP端口路由到两个DDR存储器端口或OCM。AXI_HP接口也被称为AFI(AXI FIFO接口),以强调其缓冲功能。

这些接口的主要设计目的是在PL主设备和PS存储器(包括DDR和片上RAM)之间提供一个高吞吐量的数据路径。

③AXI_GP

四个通用端口(两个主端口和两个从端口),用于处理一般的数据传输任务,提供更大的灵活性和可扩展性。

AXI_GP接口主要用于连接外部存储器或其他外设。其特性丰富,包括支持标准AXI协议、具有固定的32位数据总线宽度,以及主端口ID宽度为12位等。主端口具有发送8次读取和8次写入的能力,而从端口ID宽度为6位,并具备接受8次读取和8次写入的能力。

在性能上,AXI_GP接口直接连接到中央互联区的端口,然后再由中央互联区连接到OCM interconnect和存储器接口。与精心设计的AXI_HP接口不同,AXI_GP接口没有使用任何额外的FIFO缓冲。这意味着其性能受限于主互联和从互联的端口,因此并不旨在实现高性能。这些接口主要用于一般用途。

此外,连接到AXI通用端口(S_AXI_GP[1:0])的PL总线主控制器可以访问PS I/O外设,但无法访问CPU私有总线寄存器。这一特性使得AXI_GP接口在Zynq SoC的系统架构中发挥着特定的作用,为外部设备和PS I/O外设提供了灵活且高效的通信机制。

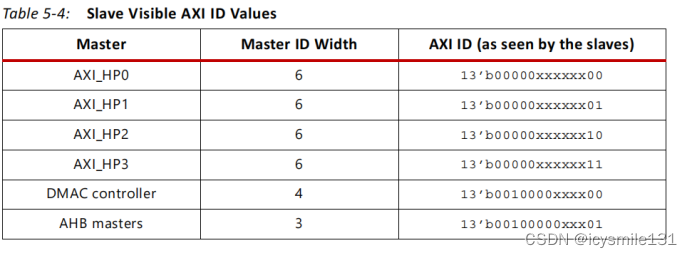

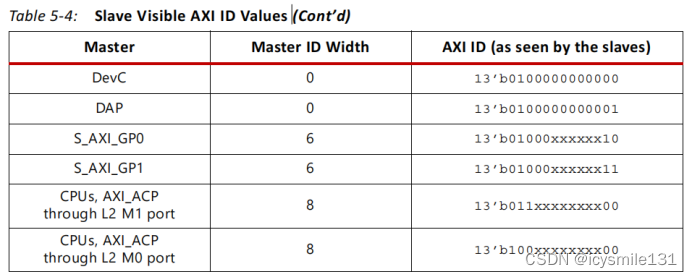

2 AXI ID

AXI ID是AXI(Advanced Extensible Interface)协议中的一个关键组成部分,用于标识和管理总线上的事务。

AXI ID是一个13位的标识符,其结构从最高有效位(MSB)到最低有效位(LSB)如下:

①三位用于标识互联的类型(如central、主机、从机等)。

②八位由主机提供,其宽度由所有主机中AXI ID的最大宽度确定。这意味着不同的主机可能有不同的AXI ID宽度,但在一个系统中,AXI ID的总位数是固定的(这里是13位),因此,如果某个主机使用较少的位数,那么它的AXI ID可能会在高位填充零。

③两位用于标识已识别互联的从机接口。

表5-4列出了从机能观察到的所有可能的AXI ID值。

4611

4611

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?