Xilinx FIFO Generator IP核是一个经过全面验证的先入先出(FIFO)内存队列,专为需要按顺序存储和检索的应用而设计。该IP核为所有FIFO配置提供了优化解决方案,并在利用最小资源的同时实现最大性能(高达500MHz)。通过Vivado Design Suite提供,还可以自定义宽度、深度、状态标志、内存类型以及写/读端口纵横比。

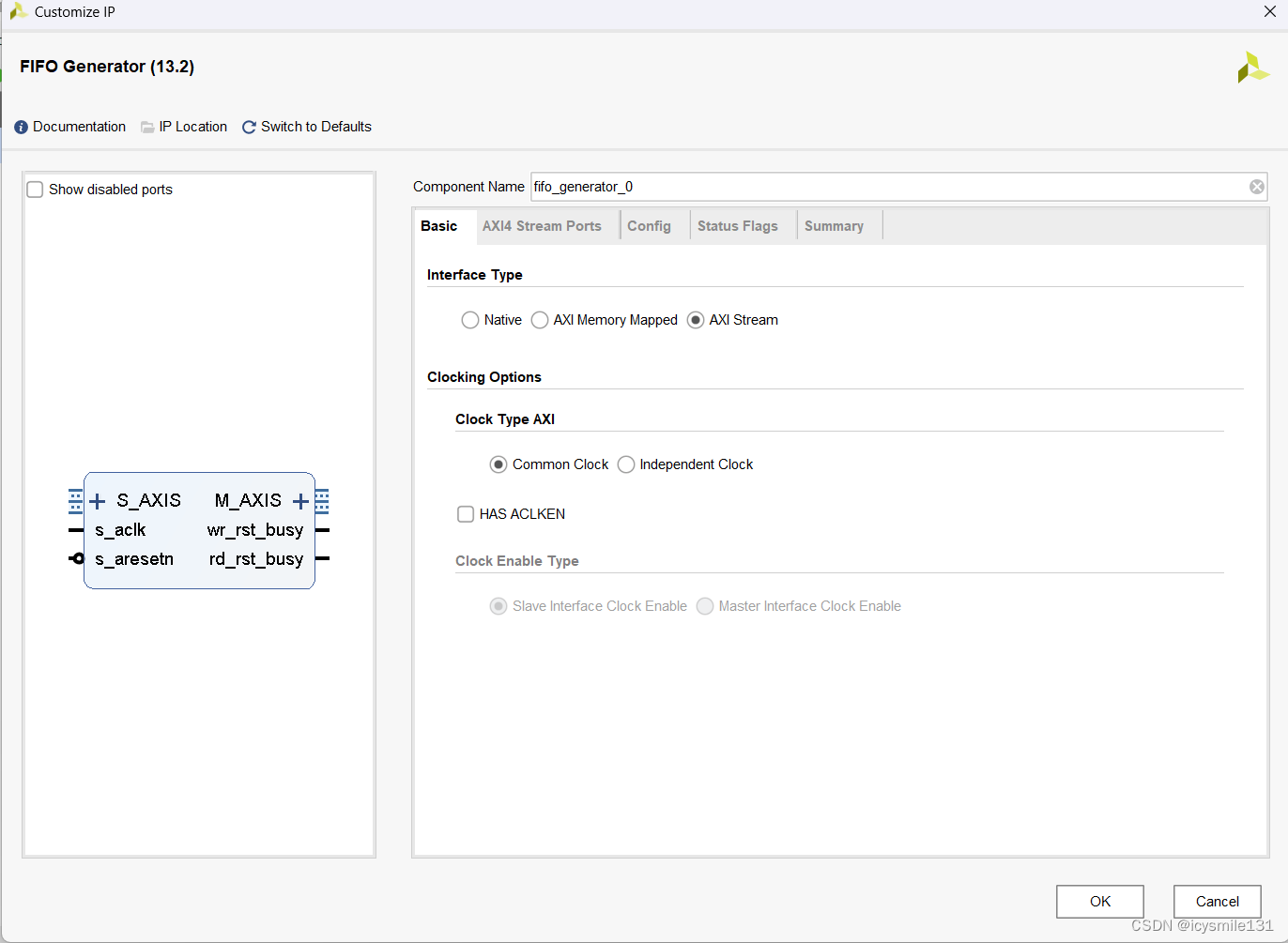

在Vivado Design Suite中需要使用FIFO Generate IP核时,打开Vivado后,在IP Catalog 中搜索FIFO,找到FIFO Generator IP核,双击或点击右键的Customize IP…来打开该IP核,如下图所示。

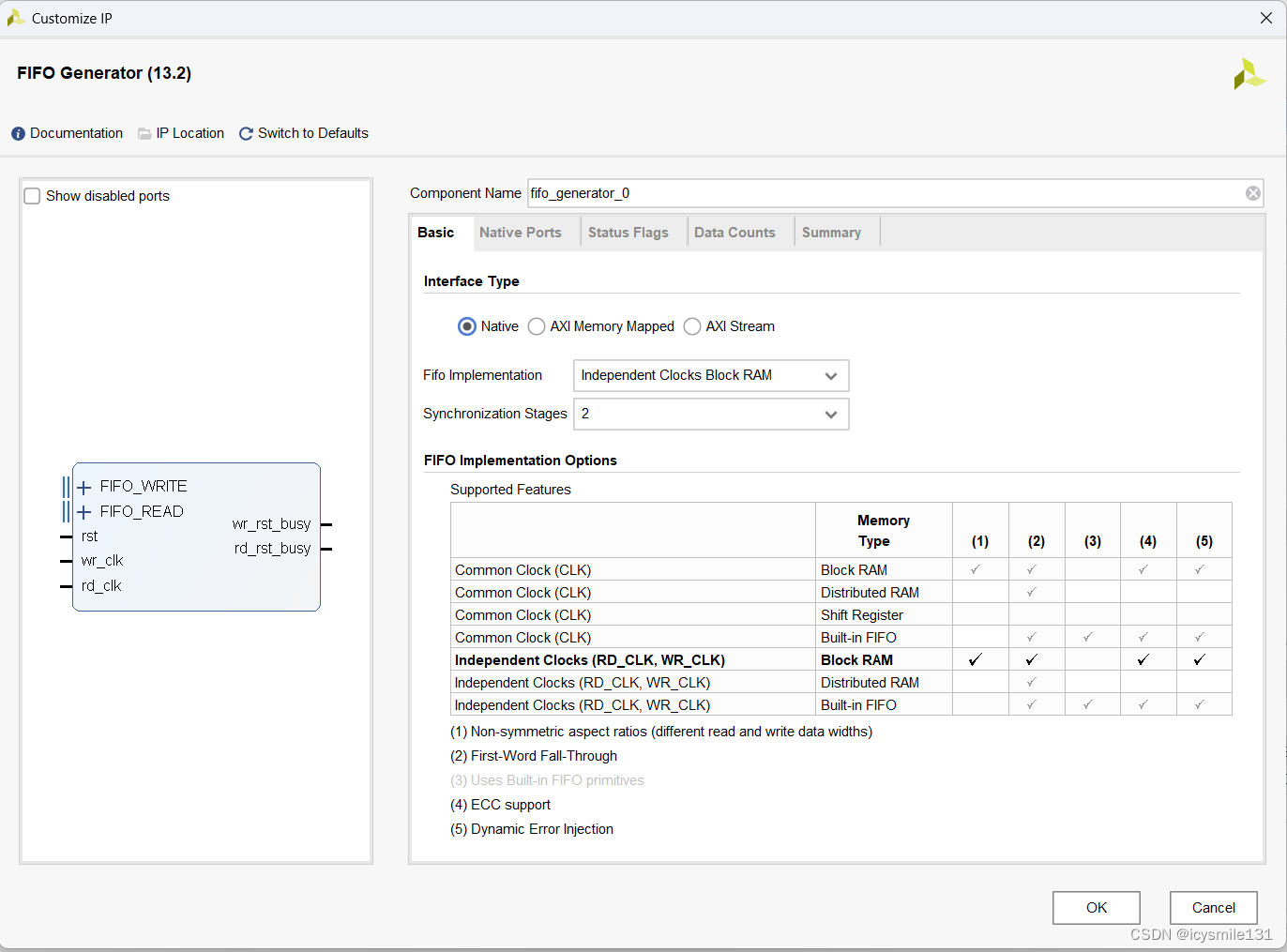

在FIFO Generator IP核的Basic选项页,可以看到该IP核有三种接口类型,分别为Native、AXI Memory Mapped和AXI Stream。

Native接口FIFO内核经过优化,适用于缓冲、数据宽度转换和时钟域解耦应用,提供有序的存储和检索功能。

AXI Memory Mapped接口和AXI4-Stream接口FIFO是从Native接口FIFO派生而来的。

1 Native接口FIFO Implementation

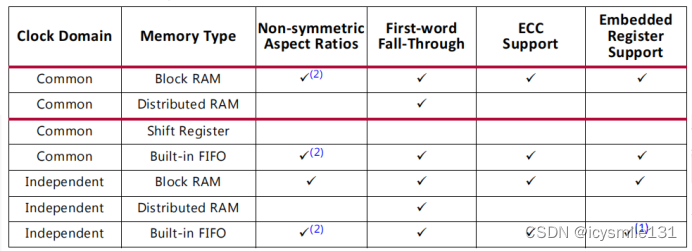

表1-2列出了Native接口支持的内存和时钟配置。

注意:

1、independent clock built-in FIFO 的嵌入式寄存器支持仅适用于UltraScale系列。

2、Xilinx仅针对UltraScale设备支持非对称读写端口比例,并且,在使用built-in FIFO时,非对称配置的最大深度限制为8192。

1.1 Common Clock: Block RAM、Distributed RAM, Shift Register

此实现类别允许您选择块RAM、分布式RAM或移位寄存器,并支持用于写入和读取数据访问的公共时钟。此配置支持的特性集包括非对称长宽比(不同的写入和读取端口宽度)、状态标志(满、几乎满、空和几乎空),以及使用用户定义阈值生成的可编程空和满标志。

此外,还支持可选的握手和错误标志(写入确认、溢出、有效和下溢),以及可选的数据计数,用于提供FIFO中的字数。对于块RAM和分布式RAM实现,您还可以选择核心的同步或异步复位。块RAM FIFO配置还支持ECC。

1.2 Common Clock: Built-in FIFO

此实现选项允许您选择Built-in FIFO,并支持用于写入和读取数据访问的公共时钟。此配置支持的特性包括状态标志(满和空),以及使用用户定义阈值的可选可编程满和空标志(对于7系列设备,可编程满/空标志直接连接到ALMOSTFULL/ALMOSTEMPTY标志)。

此外,还提供可选的握手和错误标志(写入确认、溢出、有效和下溢)。内置FIFO配置还支持内置的ECC功能以及UltraScale设备特有的功能,如非对称长宽比(不同的写入和读取端口宽度)、动态功耗门控和ECC流水线寄存器。

1.3 Independent Clocks: Block RAM and Distributed RAM

此实现选项允许您选择块RAM或分布式RAM,并支持用于写入和读取数据访问的独立时钟域。读取域中的操作与读取时钟同步,写入域中的操作与写入时钟同步。

此类型的FIFO支持的特性集包括非对称长宽比、状态标志,以及使用用户定义阈值生成的可编程满和空标志。可选的读取数据计数和写入数据计数指示器提供了相对于各自时钟域的FIFO中的字数。此外,还提供可选的握手和错误标志(写入确认、溢出、有效和下溢)。块RAM FIFO配置还支持ECC。

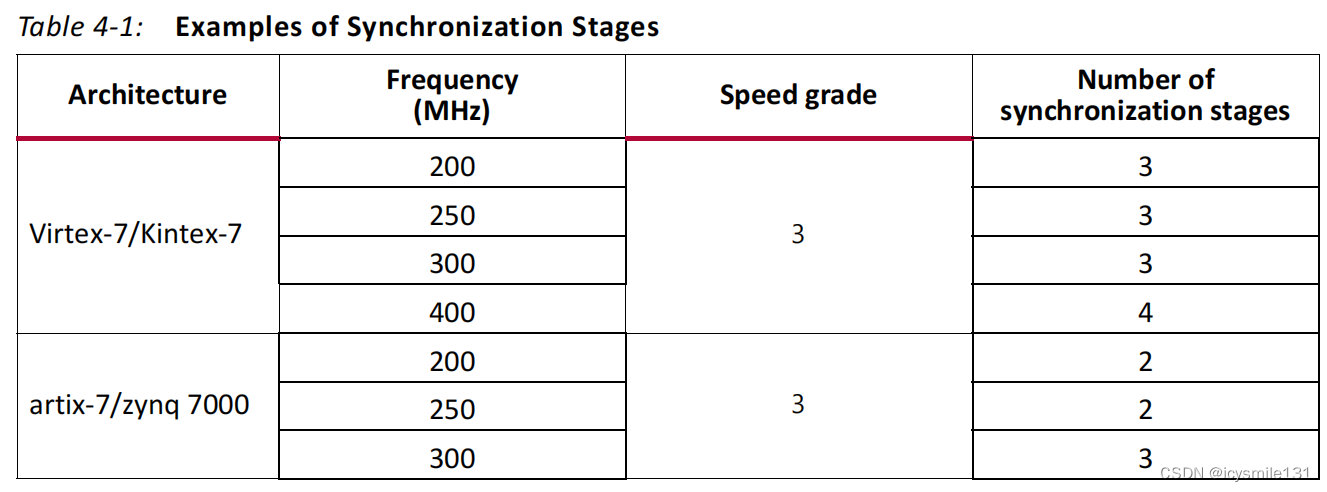

当时用这两种时钟时,Basic选项页会出现Synchronization Stages选项。

Synchronization stages(同步阶段)定义了跨交叉时钟域逻辑的同步器级数。这个设置用于确定在跨越不同时钟域的逻辑中,需要多少个同步器阶段来确保数据的准确性和一致性。在表4-1中,可以找到关于同步阶段和操作频率的示例。

同步器是一种硬件逻辑电路,用于在不同时钟域之间传递信号,以避免由于时钟不同步而导致的数据错误或不一致。通过增加同步器的级数,可以提高信号传递的可靠性和稳定性,但也会增加硬件的复杂性和成本。

因此,在选择同步阶段数时,需要根据具体的应用场景和需求进行权衡。如果时钟域之间的差异较大,或者对数据的一致性和准确性有很高的要求,那么可能需要增加同步器的级数。反之,如果时钟域之间的差异较小,或者对数据的一致性和准确性要求不是特别高,那么可以减少同步器的级数以降低硬件的复杂性和成本。

1.4 Independent Clocks: Built-in FIFO

此实现选项允许您选择Built-inFIFO。读取域中的操作与读取时钟同步,写入域中的操作与写入时钟同步。

此配置支持的特性集包括状态标志(满和空),以及使用用户定义阈值生成的可编程满和空标志(对于7系列设备,可编程满/空标志直接连接到ALMOSTFULL/ALMOSTEMPTY标志)。此外,还提供可选的握手和错误标志(写入确认、溢出、有效和下溢)。Built-in FIFO配置还支持内置的ECC功能以及UltraScale设备特有的功能,如非对称长宽比、动态功耗门控和ECC流水线寄存器。

使用独立时钟的选项允许设计者在复杂的系统中更灵活地管理数据流动,尤其是在读取和写入操作需要独立控制时钟的场景中。此外,这些实现选项还提供了丰富的特性和配置选项,以满足不同应用的需求。ECC的支持增强了数据传输的可靠性,而动态功耗门控等功能则有助于优化系统的功耗性能。

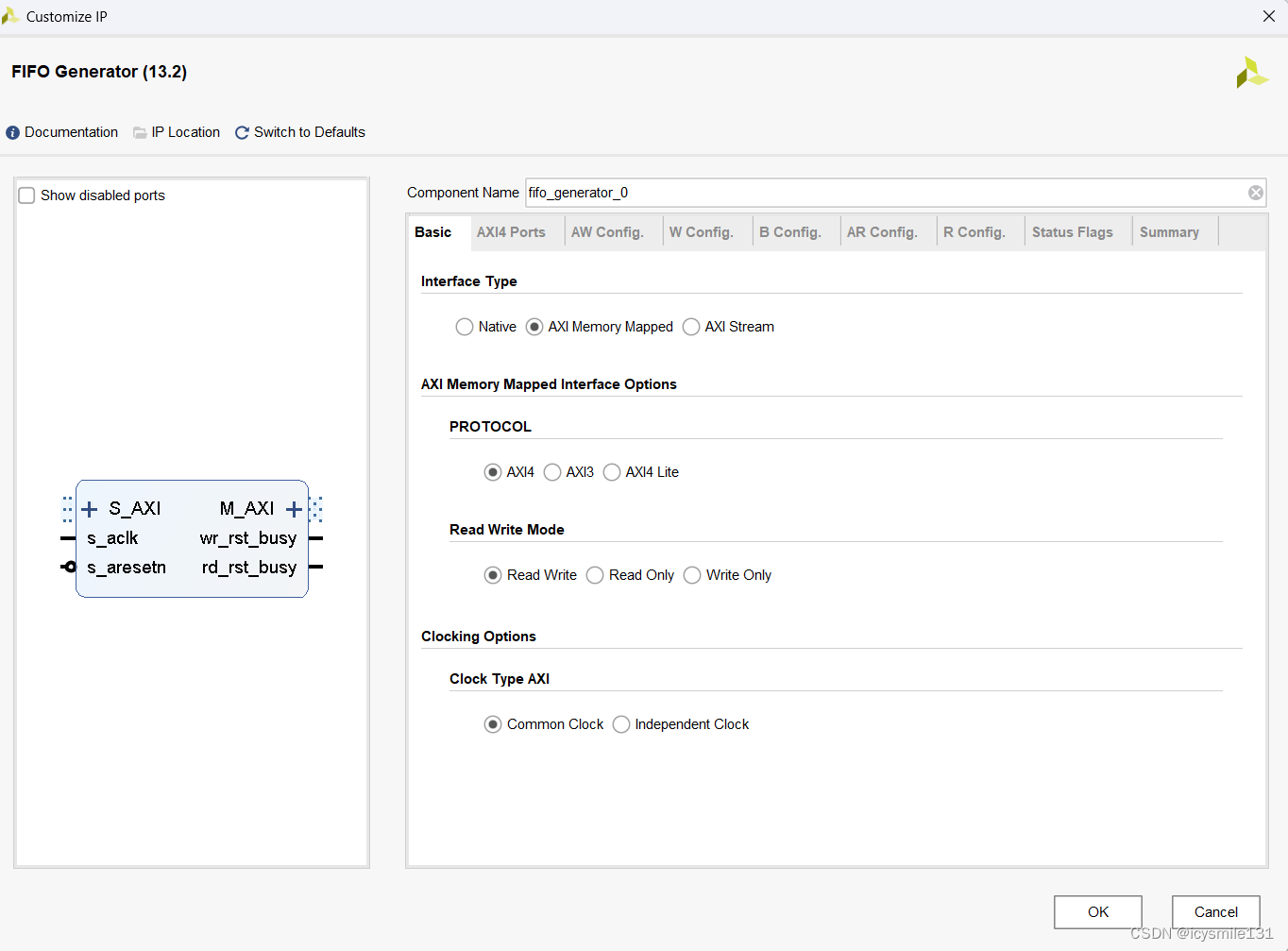

2 AXI Memory Mapped接口

AXI Memory Mapped接口主要有三种协议:AXI4、AXI4-Lite以及AXI3。

AXI4主要面向高性能地址映射通信的需求,是面向地址映射的接口,允许最大256轮的数据突发传输。

AXI4-Lite则是一个轻量级的地址映射单次传输接口,即无突发传输接口,占用很少的逻辑单元。

AXI3用于连接处理器和内存或其他高速外设,是在AXI4之前的一个版本。

每种接口都有其特定的应用场景和优势,根据具体的设计需求,可以选择合适的AXI Memory Mapped接口风格。

读写模式的选择根据具体使用情况而定。

Independent Clock配置允许用户在写端口和读端口上实现独特的时钟域。FIFO Generator IP核负责处理时钟域之间的同步,对相位和频率没有要求。当需要在单个时钟域中进行数据缓冲时,可以选择Common Clock选项,以便FIFO Generator IP核生成一个针对单个时钟优化的IP核。

3 AXI-Stream接口

AXI-Stream是一种高效、简单的数据传输协议,主要用于高吞吐量的数据流传输场景。相比于传统的AXI总线,AXI-Stream总线更加简单和轻量级。它通过无需地址的方式,将数据从一个模块传输到另一个模块,特别适用于需要高速数据传输的应用场景。

Independent Clock配置允许用户在写端口和读端口上实现独特的时钟域。

当需要在单个时钟域中进行数据缓冲时,选择Common Clock选项。

HAS ACLKEN用于选择Clock Enable Type。

**Slave接口时钟使能(Slave Interface Clock Enable)**功能允许AXI主设备以AXI从设备接口(或FIFO的写入端)的分频速率运行。在这种情况下,时钟使能信号是单时钟宽度的,并且是同步的,它确保了主设备和从设备之间的时钟同步,从而避免了数据丢失或传输错误等问题。

具体来说,Slave接口时钟使能机制允许AXI主设备以更加灵活的方式与从设备进行通信。通过调整时钟使能信号的频率,主设备可以在不同的速率下读取或写入数据,从而实现更加高效和灵活的数据传输。这种分频操作特别适用于需要处理大量数据或需要平衡不同设备之间数据传输速率的场景。

**主接口时钟使能(Master Interface Clock Enable)**功能允许AXI从设备以AXI主设备接口(或FIFO的读取端)的分频速率运行。在这种情况下,时钟使能信号是单时钟宽度的,并且是同步的,提高了数据传输的可靠性和稳定性。这种机制确保了数据在传输过程中的准确性和一致性,从而保证了整个系统的正常运行。

通过利用主接口时钟使能功能,AXI从设备可以根据实际需求以较低的速率读取数据,这在某些应用中可能是有利的。例如,当主设备写入数据的速率高于从设备处理数据的速率时,通过降低从设备的读取速率,可以避免数据拥塞或丢失。

1436

1436

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?