当需要在设计中使用自定义IP时,可以通过为IP核的各种参数指定值来进行定制。以下是一般步骤的概述:

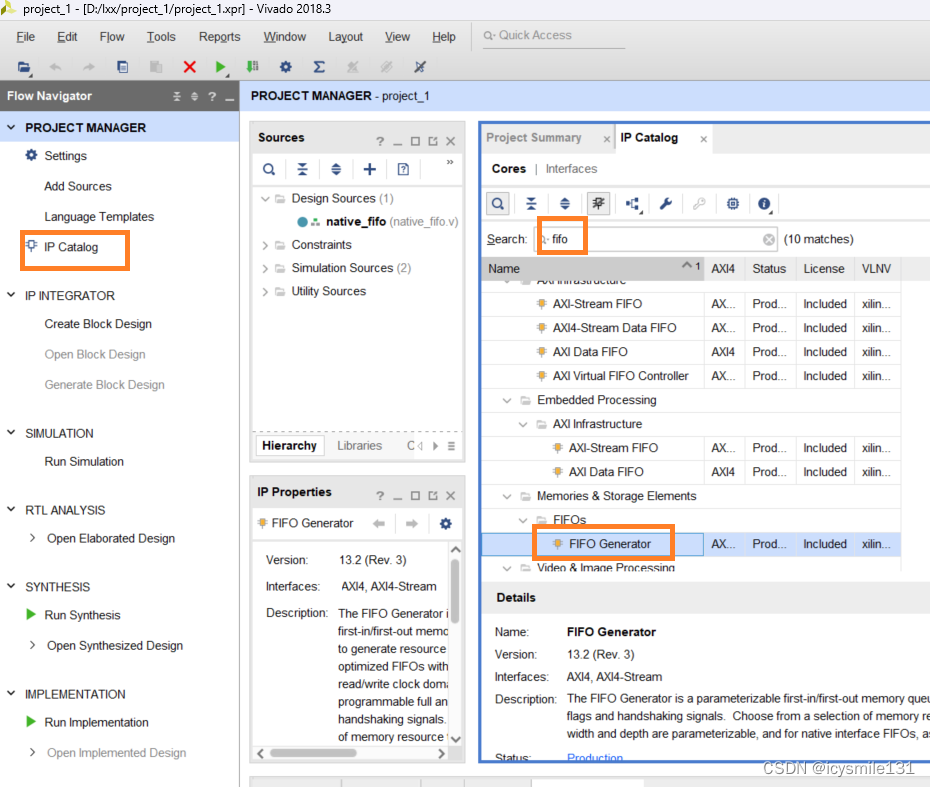

首先是从IP catalog中选择IP核。

然后双击这个选定的IP核,打开一个定制向导或参数设置窗口。或在工具栏或右键菜单中选择“Customize IP”命令,启动定制向导或打开相关参数设置。

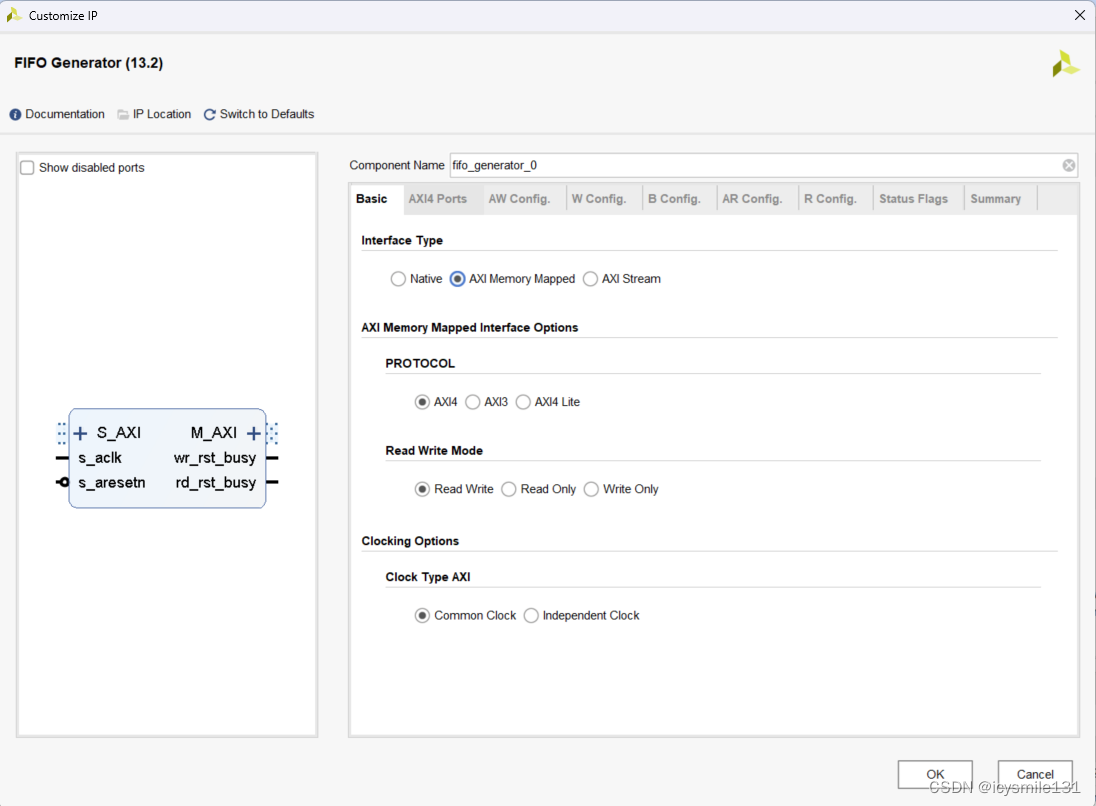

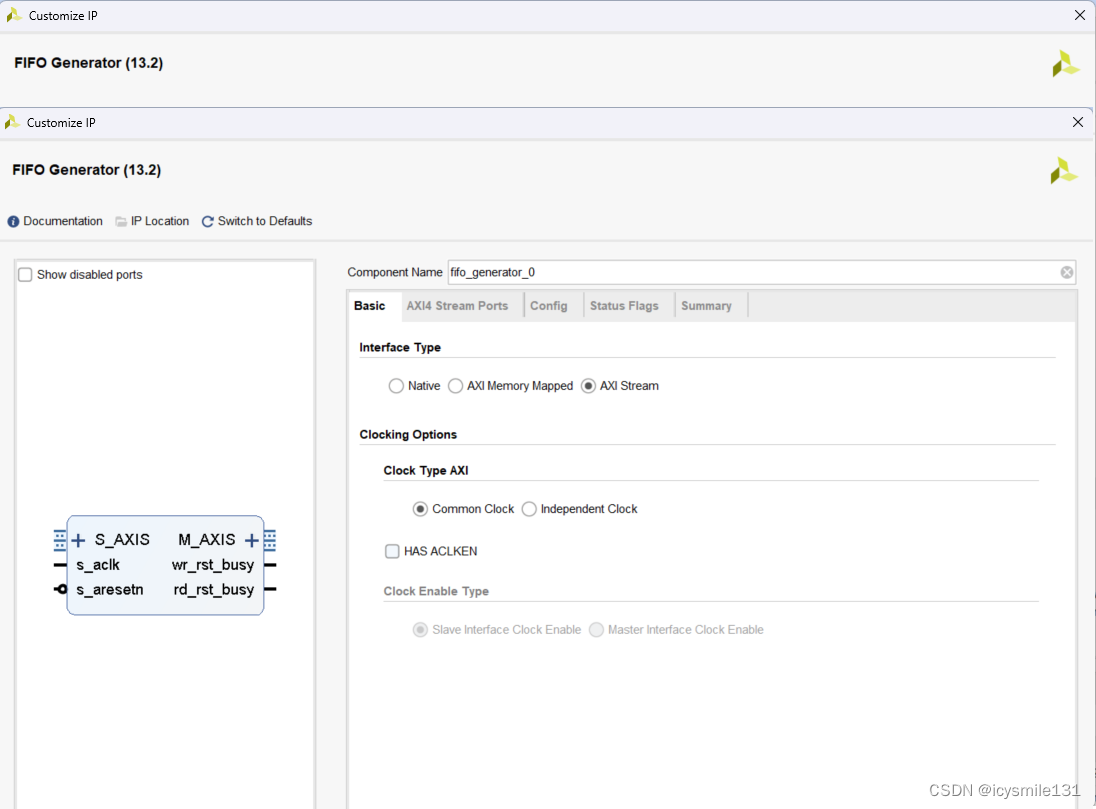

对于AXI memory mapped的FIFO Generator IP核,通常包含多个配置选项卡,以便用户可以根据其应用需求进行定制。以下是一些常见的配置选项卡示例,但请注意,这些可能因Vivado的版本更新而略有变化:

1 Basic Tab

AXI Interface Option

有四种AXI接口样式是可用的:AXI4-Stream、AXI4、AXI3和AXI4-Lite。

Clocking Options

FIFO可以被配置为写操作和读操作使用独立时钟域或公共时钟域。

独立时钟(Independent Clock):允许用户在写端口和读端口上实现独特的时钟域。FIFO Generator IP核负责处理时钟域之间的同步,不需要对时钟的相位和频率有特定的要求。

公共时钟(Common Clocks):当在单个时钟域内进行数据缓冲时,可以选择公共时钟选项。这意味着写端口和读端口都使用相同的时钟信号。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6361

6361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?