在7 Series FPGAs Integrated Block for PCI Express IP核中,PCI的配置空间是一个关键组成部分,它允许对PCIe设备进行配置和管理。

配置管理层维护PCI(Peripheral Component Interconnect) Type 0端点的配置空间,并支持以下功能:

一、 PCI配置空间功能

1 实现PCI配置空间

提供PCI标准定义的配置空间寄存器的实现,包括设备ID、厂商ID、类代码、子类代码等。

2 支持配置空间访问

允许通过软件读取和写入PCI配置空间寄存器的值。

3 电源管理功能

3 实现错误报告和状态功能

提供硬件错误检测机制,并报告给软件层。

提供设备状态信息,如设备是否已启动、是否处于错误状态等。

4 实现数据包处理功能

接收:

配置读和写请求

发送:

- 包含或不包含数据的完成数据包

- 事务层模块(TLM)错误消息

- 用户自定义错误消息

- 电源管理消息/握手协议

5 MSI和INTx中断仿真

提供Message Signaled Interrupts (MSI) 和传统的INTx中断机制,允许设备与处理器通信。

6 在PCI配置空间中实现MSI-X功能结构(可选)

MSI-X提供了更多的中断向量,以支持更复杂的设备。

7 在PCI Express扩展功能空间中实现以下功能(可选)

- 设备序列号:允许设备具有唯一的序列号。

- 虚拟通道功能(仅支持VC0):允许在PCIe设备之间实现多个逻辑通道,以支持不同的服务质量(QoS)需求。

- Xilinx定义的厂商特定功能结构:提供循环回控制和状态等特定于Xilinx的功能。

8 在PCI Express扩展配置空间中实现以下功能(可选)

- 高级错误报告(AER)功能结构:提供了更高级的硬件错误报告功能,包括错误来源、错误严重性等信息。

-

可调整基地址寄存器(RBAR)功能结构:允许操作系统动态地调整BAR(Base Address Register)的大小,以支持更大的内存映射。

二、 PCI 配置空间组成

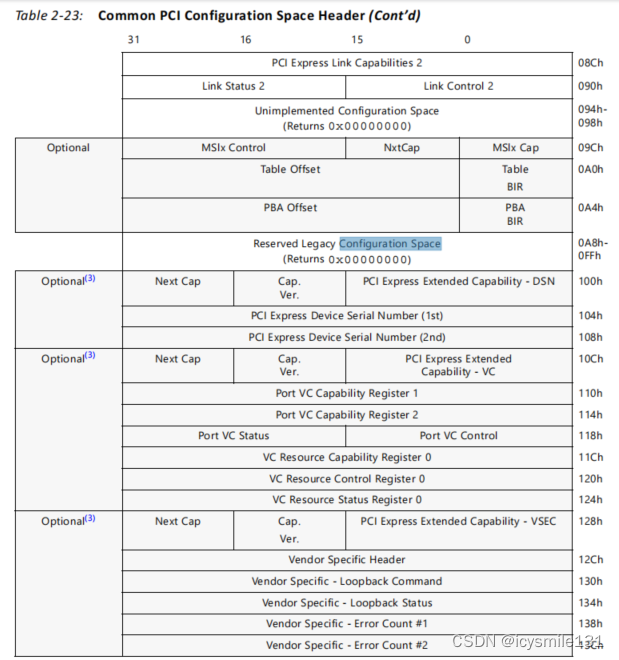

7 Series FPGAs Integrated Block for PCI Express IP核中PCI主要由以下三部分组成:

1. Legacy PCI v3.0 Type 0/1 Configuration Space Header

- Type 0 Configuration Space Header:这是为PCI设备(通常是端点设备)定义的标准配置空间头部。它包含了设备的ID、分类代码、基地址寄存器(BARs)、中断信息等。

- Type 1 Configuration Space Header:这是为PCI-to-PCI桥或根端口定义的配置空间头部。它允许一个PCI总线连接到另一个PCI总线,并提供了桥接所需的信息。

2. Legacy Extended Capability Items

下面是PCI配置空间中的扩展能力字段,用于提供额外的功能或属性。

- PCIe Capability Item:定义了PCIe设备的基本能力,包括设备类型、链接速度、链接宽度等。

- Power Management Capability Item:定义了设备的电源管理功能。

- Message Signaled Interrupt (MSI) Capability Item:MSI是PCI和PCIe中用于中断的一种机制,它允许设备使用消息而不是传统的INTx引脚来请求中断。

- MSI-X Capability Item:MSI-X是MSI的扩展,它允许设备有更多的中断向量和更高的灵活性。

该IP核可以实现最多四个遗留的扩展能力项(如上),地址从0xA8到0xFF的遗留扩展能力空间是保留的或用户可定义的(仅限于端点配置)。这部分空间可用于实现特定的用户功能或厂商自定义功能。如果该IP核没有实现某个可选的能力结构,那么该位置的地址是保留的。如果未使用这部分空间,当读取这个地址范围时,IP核将返回0x00000000。如果您在0xA8到0xFF的范围内实现了用户定义的寄存器,那么这部分空间必须在用户应用程序中实现。此外,对于该范围内未在用户应用程序中实现的任何地址,您也需要负责返回0x00000000。

3. PCIe Extended Capabilities

下面是PCIe特有的扩展能力字段,为PCIe设备提供了更多的功能和属性。

- Device Serial Number Extended Capability Structure:提供了设备的唯一序列号。

- Virtual Channel Extended Capability Structure:允许PCIe设备之间的虚拟通道,用于优化数据传输。

- Vendor Specific Extended Capability Structure:这是为特定厂商定义的扩展能力,允许厂商为其设备添加自定义功能。

- Advanced Error Reporting Extended Capability Structure:提供了高级错误报告功能,用于检测、报告和恢复PCIe错误。

- Resizable BAR Extended Capability Structure:允许设备动态调整其基地址寄存器(BAR)的大小,以优化某些类型的数据传输。

IP核实现了最多三个PCIe扩展能力(可选)。剩余的PCIe扩展能力空间可用于您自己的实现。您可以使用的空间的起始地址取决于实现了哪五个可选的PCIe扩展能力(如果有的话)。如果您在这个空间中实现了寄存器,您可以选择这个空间的起始位置,并且这部分空间必须在用户应用程序中实现。

注:

-

在Xilinx的Vivado IDE中,根据用户所做的不同选择,MSI能力结构的布局可能会有所不同。MSI是PCI Express设备用于通知主机系统(如CPU)其需要服务的一种方式,而不是使用传统的中断线。

-

在端点配置中,当被查询返回

0x00000000(即全零)时,表示该字段未使用或不支持某个特定的功能。 -

PCI Express设备的配置空间不仅包含基本的256字节(00h-FFh),还包括一个扩展的配置空间(100h-FFFh),其中可以包含各种可选的能力结构。

三、用户实现的配置空间

PCIe IP核允许用户在其应用程序中可选地实现PCI配置空间或PCIe扩展配置空间中的寄存器。用户应用程序必须为这些空间内的所有地址返回配置完成(Config Completions)。

1 PCI配置空间

如果用户选择在PCI配置空间的0xA8到0xFF范围内实现寄存器,可以在IP核生成过程中定义要实现的地址区域的起始地址。

用户应用程序负责生成从用户定义的起始地址到PCI配置空间末尾(0xFF)的所有配置读写操作的完成(Completions)。对于该范围内未实现的寄存器,配置读取操作应以数据为0x00000000的完成来响应,而配置写入操作应以成功的完成来响应。

例如,如果要实现地址范围0xC0到0xCF,则有几个地址范围需要根据访问方式进行不同的处理。下表提供了这个示例的更多详细信息。

| Address Range | Configuration Writes | Configuration Reads |

| 0x00 to 0xBF | IP核自动响应 | IP核自动响应 |

| 0xC0 to 0xCF | 用户应用程序在成功完成了配置写操作后,返回了一个表示成功完成的响应。 | 用户应用程序返回与寄存器相关的内容或数据 |

| 0xD0 to 0xFF | 用户应用程序在成功完成了配置写操作后,返回了一个表示成功完成的响应。 | 用户应用程序返回0x00000000 |

2 PCI Express扩展配置空间

PCI Express扩展配置空间的起始地址,作为用户可选实现的区域,取决于您在IP核中启用的PCI Express扩展功能。以下是关于PCI Express扩展配置空间用户实现的一些关键点:

起始地址的选择:

IP核允许您在生成和自定义IP核时选择用户实现的PCI Express扩展配置空间的起始地址,这个空间必须在用户应用程序中实现。

用户应用程序的责任:

对于在此选定范围内但在用户应用程序中未实现的地址,用户应用程序需要为配置读取生成带有0x00000000的Cpld(Completion),并为配置写入生成成功的Cpl(Completion)。

非连续的用户配置空间:

您可以选择实现一个用户配置空间,其起始地址不与IP核实现的最后一个功能结构相邻。

在这种情况下,对于您选择不实现的区域的配置访问,IP核将返回一个带有0x00000000的完成。

在上表的配置示例中,PCI Express扩展配置空间具有以下设置:

- DSN(数据安全网络)功能已启用

- VSEC(Vendor-Specific Extended Capabilities)功能已启用

- 用户实现的PCI Express扩展配置空间已启用

- 用户实现的PCI Express扩展配置空间起始地址为168h

在上述配置中:

- DSN功能占用了从100h到108h的寄存器。

- VSEC功能占用了从10Ch到120h的寄存器。

- 剩余的PCI Express扩展配置空间从地址124h开始,可以用于实现自定义功能。在这个例子中,选择了从168h开始的地址区域来实现寄存器。

- 对于地址从124h到164h的寄存器,IP核会返回包含0x00000000的成功完成(Completion)。这是因为这些地址在用户实现的范围内没有被特别指定。

- 上表仅实现了从168h到47Ch的寄存器。

在这个例子中,对于地址从480h到FFFh的寄存器配置访问,您(用户应用程序)需要负责返回包含0x00000000的成功完成。这是因为这些地址在用户实现的范围内也没有被特别指定,但它们是PCI Express扩展配置空间的一部分。

3572

3572

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?