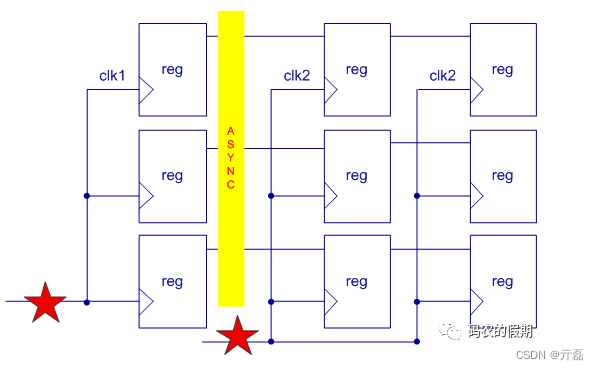

一、基本二级同步结构

源时钟域同步一拍,目的时钟域同步两拍。

二、源时钟域打拍输出信号,与目的时钟域采样之间,是一根线。这根线延迟如果不约束set_max_delay,会存在风险。

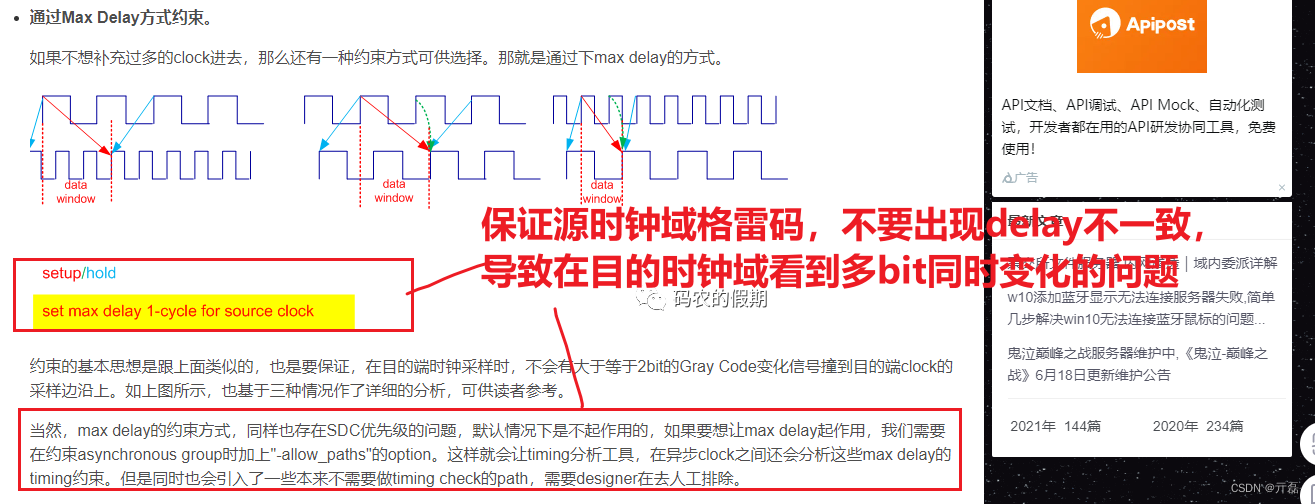

举例,格雷码总线信号,多根线,因为线延迟不一致,导致在目的时钟域采样的时候,有可能存在多bit同时翻转的问题现象。导致读写指针,空满标志判断出错,功能出错。

相关图片,转载来自:《异步fifo_Gray Code异步FIFO的多种约束方式》https://blog.csdn.net/weixin_39950083/article/details/111586325

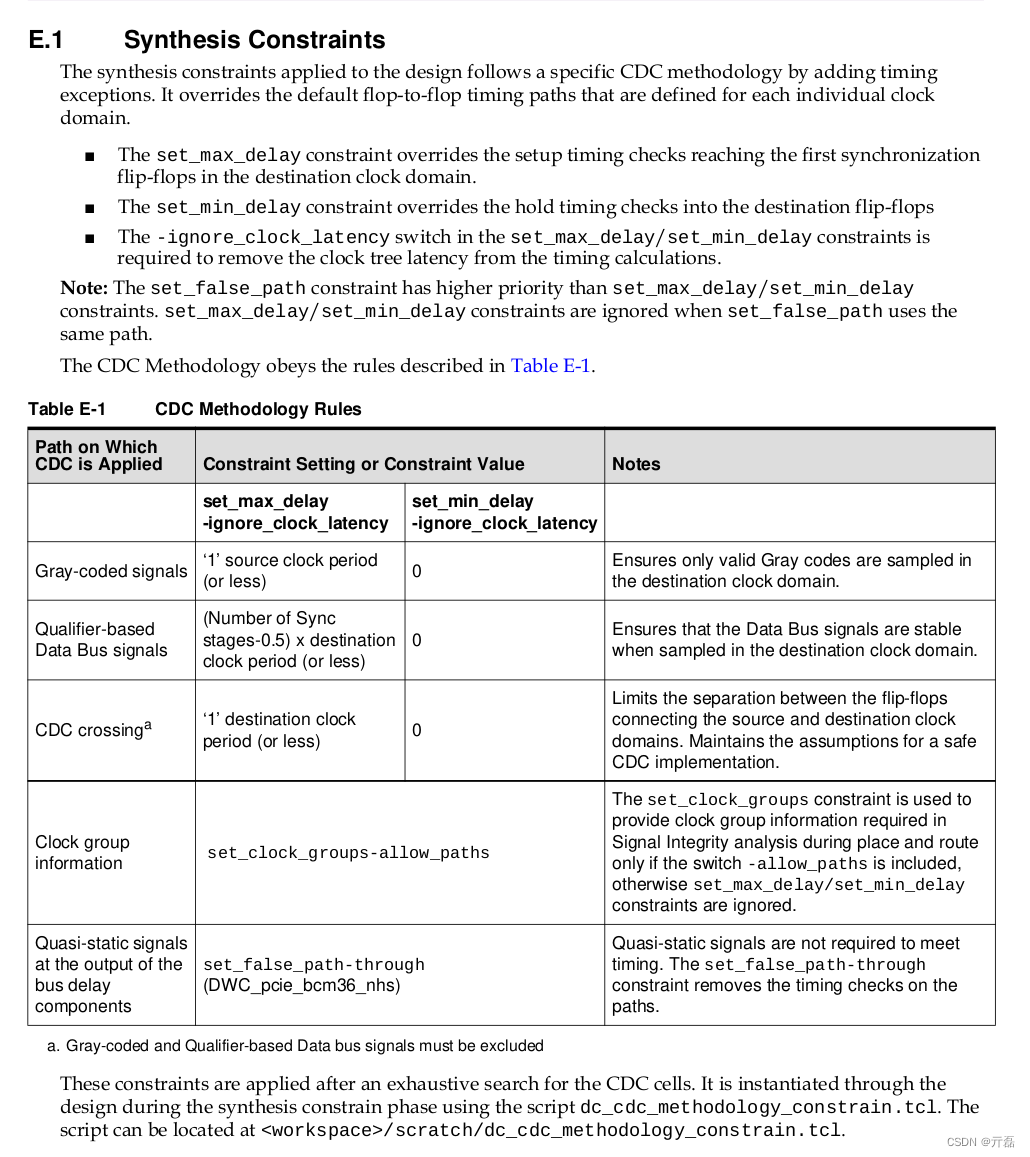

下图参考synopsys IP的设置方法:

配合下图,个人理解下图是有逻辑顺序的。【set_max_delay相比false_path,false_path优先级高】【路径越精确优先级越高】【最好是加余量,比如1T->0.8T】:

- 设置格雷码。set_max_delay 0.8T_source -ignore_clock_latency

- 然后设置静态数据总线信号(有同步的那种)。

- set_max_delay 0.8T_source -ignore_clock_latency先设置不同时钟域之间的set_max_delay 0.8T_destination -ignore_clock_latency。【比如有些数据总线信号/伴随信号,是通过握手同步传递的。注意,相关数据总线信号/伴随信号,也需要设置set_max_delay,否则会握手同步的伴随信号出错】

- 如果综合加上,就要-allow_paths。但是会影响dft设计,项目中还是把set_max_delay单独抓出来在后端STA阶段分析吧。

- 最后一条set_false_path,是去除上面,主要是第1条中的静态信号,保证时序收敛不要有太多过约现象。

161

161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?