前面一节我们学会了创建基于AXI总线的IP,但是对于AXI协议各信号的时序还不太了解。这个实验就是通过SDK和Vivado联合调试观察AXI总线的信号。由于我们创建的接口是基于AXI_Lite协议的,所以我们实际观察到是AXI_Lite协议的信号时序。

具体做法是创建一个基于AXI总线的加法器模块,在Vivado里将AXI总线添加到debug信号里,实际上是用逻辑分析仪探测信号,在SDK端通过debug方式依次写入两个加数,由PL计算出和,我们读出这个和打印到串口,这样AXI总线的读和写就都能观察到了。

板子使用的是zc702。

在观察信号之前我们有必要简单了解AXI是个什么:

AXI总线是一种高性能、高带宽、低延迟的片内总线,AXI协议描述了主从设备数据传输的方式。主设备和从设备通过握手信号建立连接,握手信号包括主机发送的VALID信号,表示数据有效,从机发送的READY信号,表示从机准备好了接收数据。当VALID和READY都有效的时候传输开始。

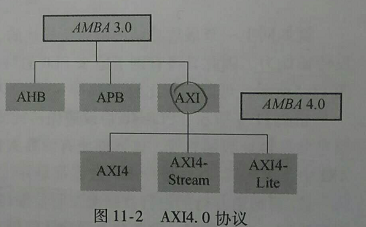

Zynq使用的是AXI协议的4.0版本,由AMBA3.0协议发展而来:

AXI的三种总线各有各的用途:

AXI4支持突发数据传输,主要用于CPU访问存储等需要高速数据交互的场合,相当于原来的AHB协议;

AXI_Lite一次传输单个数据,主要用于访问一些低速外设,相当于原来的APB;

AXI_Stream数据传输不需要地址,主设备直接连续读写数据,主要用于高速流数据的传输,使用起来类似FIFO。

AXI4总线和AXI4-Lite总线具有相同的组成部分:

(1) 读地址通道, 包含ARVALID, ARADDR, ARREADY信号;

(2) 读数据通道, 包含RVALID, RDATA, RREADY, RRESP信号;

(3) 写地址通道, 包含AWVALID, AWADDR, AWREADY信号;

(4) 写数据通道, 包含WVALID, WDATA, WSTRB, WREADY信号;

(5) 写应答通道, 包含BVALID, BRESP, BREADY信号;

(6) 系统通道, 包含: ACLK, ARESETN信号。

帮助记忆:

读地址信号都是以AR开头(A: address; R: read)

写地址信号都是以AW开头(A: address; W: write)

读数据信号都是以R开头(R: read)

写数据信号都是以W开头(W: write&#x

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

916

916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?