数字电路基础知识七) ——Vivado使用Chipscope在线逻辑分析仪Debug

在 https://blog.csdn.net/vivid117/article/details/96508986 和 https://blog.csdn.net/vivid117/article/details/96753878 这两篇文章中提到了使用两种在线逻辑分析进行在线debug的方法。

由于RTL仿真后RTL并不一定完全正确执行,所以可以通过Xilinx自带的在线逻辑分析,在板子运行并查看我们想要的关键信号。

一、使用(make_debug = “true”)形式

- 将(make_debug = “true”)添加到需要观察的信号前面。

(*mark_debug = "true"*) reg [3:0] led_o;

(*mark_debug = "true"*) wire key_cap;

(*mark_debug = "true"*) reg [1:0] key_s = 2'b0;

(*mark_debug = "true"*) reg [1:0] key_s_r = 2'b0;

(*mark_debug = "true"*) wire en_10ms ;

- 在线逻辑分析仪在下面,具体操作步骤参见:

https://blog.csdn.net/vivid117/article/details/96508986

二、使用ILA IP Core 形式

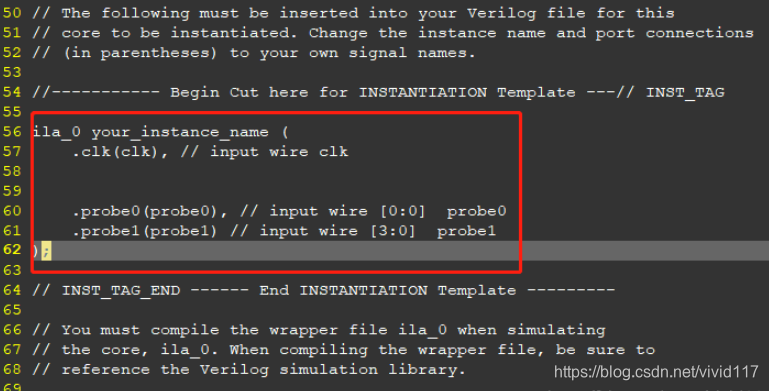

采用Xilinx的 ILA IP core 来实现被观察信号的采集,本质上和之前是一样的。

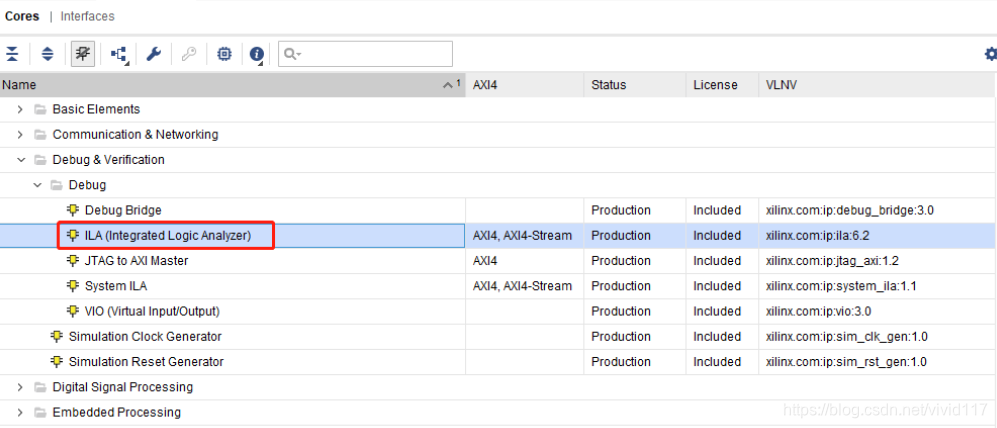

- 在IP catlog中选择,如下:

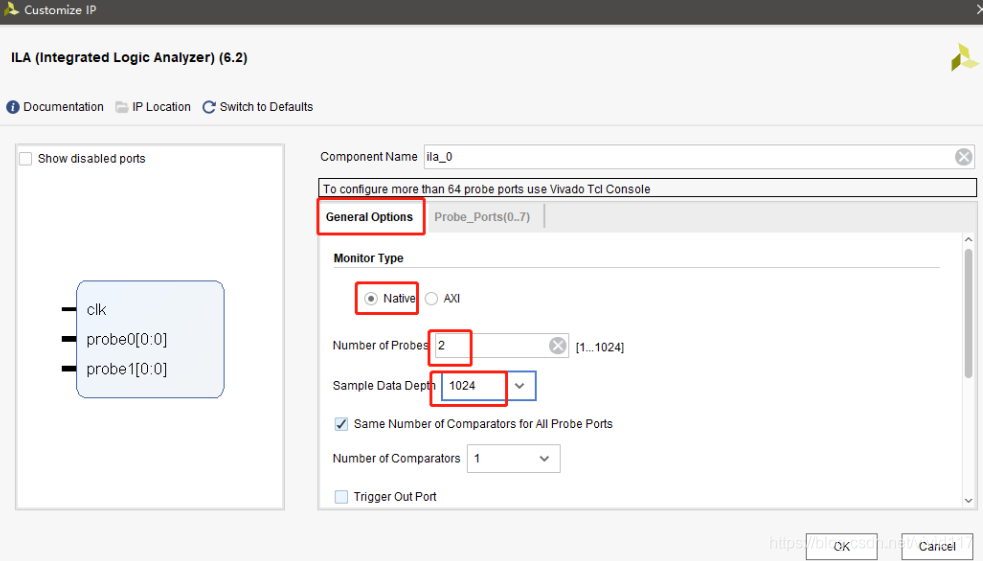

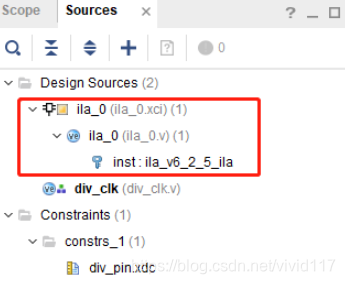

- 设置完成后如下:

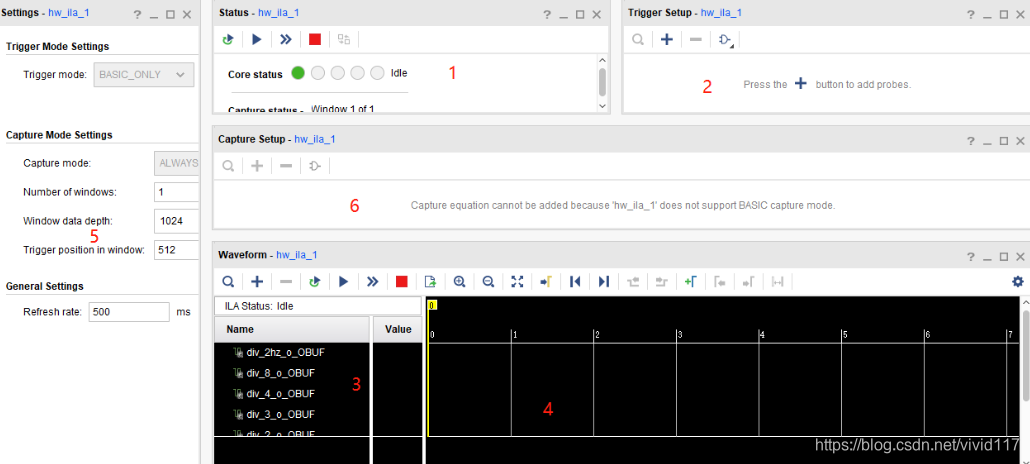

- 在线逻辑分析仪的界面如下

具体操作如下:

https://blog.csdn.net/vivid117/article/details/96753878

本文介绍在Vivado中利用Chipscope在线逻辑分析仪及ILA IP Core进行数字电路调试的两种方法。通过在关键信号前添加(make_debug=true)属性,或使用ILA IP Core采集信号,可在电路运行时实时监测信号状态,有效提升RTL级设计的调试效率。

本文介绍在Vivado中利用Chipscope在线逻辑分析仪及ILA IP Core进行数字电路调试的两种方法。通过在关键信号前添加(make_debug=true)属性,或使用ILA IP Core采集信号,可在电路运行时实时监测信号状态,有效提升RTL级设计的调试效率。

3735

3735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?