有问题的代码:

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output done

);

reg [1:0] state,next_state;

reg [3:0] counter;

//s0 //s1 //s2 //s3

parameter idle=0,data=1,stop=2,finish=3;

always @(posedge clk)

begin

if(reset)

state <= idle;

else

state <= next_state;

end

always @(*)

begin

case(state)

idle :next_state = (!in)?data:idle;

data :next_state = (counter == 7 )?stop:data;

stop: next_state = (in)?finish:stop;

finish: next_state = (!in)?idle:finish;

default:next_state = idle;

endcase

end

always @(posedge clk)

begin

if(state == data)

counter<=counter+1;

else

counter<=0;

end

assign done = (state == stop);

endmodule

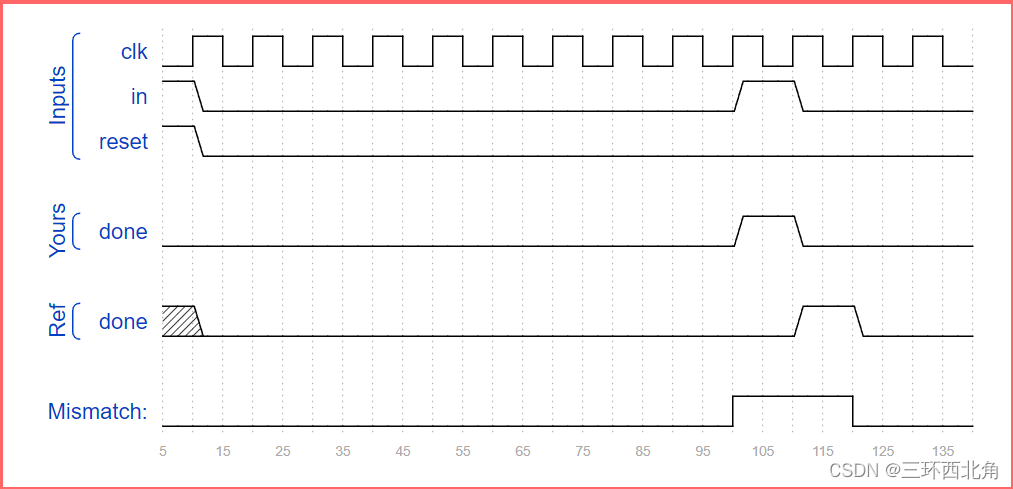

异常测试用例

正确的代码:

https://blog.csdn.net/weixin_45243340/article/details/115789985

module top_module(

input clk,

input in,

input reset, // Synchronous reset

output done

);

parameter S0 = 2'd0,S1= 2'd1,S2= 2'd2,S3 = 2'd3;//S0起始状态,当in拉低时,到S1状态

//S1计数状态,记满8bit,到S2状态

//S2停止状态,如果在预期的情况下没有出现停止位,则FSM必须等待直到找到停止位,然后再尝试接收下一个字节。

//S3停摆状态,没有接收到停止位,done拉低,当in拉高时,跳转到起始状态

reg[1:0] state,next_state;

reg [3:0] counter;

always@(posedge clk)begin

if(reset)begin

state = S0;

end//reste

else begin

state = next_state;

end//else

end

always@(*)begin

case(state)

S0:begin

if(!in)begin

next_state = S1;

end//in = 0

else begin

next_state = S0;

end//in = 1

end

S1:begin

if(counter == 7)begin

next_state = S2;

end//记满8bit

else begin

next_state = S1;

end

end

S2:begin

if(in)begin

next_state = S0;

end//in = 1

else begin

next_state = S3;

end//in = 0

end

S3:begin

if(in)begin

next_state = S0;

end//in = 1

else begin

next_state = S3;

end//in = 0

end

default:next_state = S0;

endcase

end

always@(posedge clk)begin

case(state)

S0:begin

counter <= 0;

done <=0 ;

end

S1:begin

counter <= counter + 1;

end

S2:begin

counter <=0;

if(in)begin

done <= 1;

end//停止位

else begin

done <= 0;

end

end

S3:begin

counter <=0;

done <= 0;

end

default:begin

counter <= 0;

done <=0 ;

end

endcase

end

endmodule

文章描述了一个同步状态机模块top_module的正确代码实现,包括状态转移逻辑和计数器功能。它还提到一个初始有问题的代码版本,并提供了优化后的代码,强调了在状态机设计中处理输入信号和异常情况的重要性。

文章描述了一个同步状态机模块top_module的正确代码实现,包括状态转移逻辑和计数器功能。它还提到一个初始有问题的代码版本,并提供了优化后的代码,强调了在状态机设计中处理输入信号和异常情况的重要性。

368

368

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?