目录

1.时钟资源概述

“全局时钟和第二全局时钟资源”是FPGA同步设计的一个重要概念。合理利用该资源可以改善设计的综合和实现效果;如果使用不当,不但会影响设计的工作频率和稳定性等,甚至会导致设计的综合、实现过程出错。Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源。目前,大型设计一般推荐使用同步时序电路。同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

2.外部时钟输入

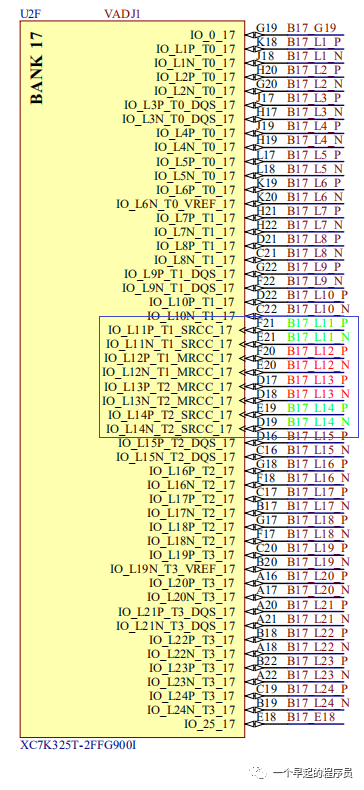

外部时钟输入都要通过差分时钟引脚对(clock-capable)进入FPGA,单端时钟可以用单端输入(P端),具有时钟功能输入的引脚在每个IO bank的SRCC和MRCC,如下图。

3.全局时钟和局部时钟区别

全局时钟和局部时钟使用的资源不一样,全局时钟要靠BUFG驱动,将时钟信号放在时钟树上,保证到整个芯片的任意一个触发器是电延时等长的,局部时钟靠BUFR驱动,只在一个bank内用(使用的第二全局时钟资源)。

BUFG,输入为固定管脚。输出为H型全铜全局高速网络(全局时钟资源)。这样抖动和到任意触发器的延时差最小,这个也就是FPGA做同步设计可以不需要做后仿真的原因。

第二全局时钟资源其实是通过片内的高速行列总线来实现的。而不像全局时钟总线是一条专用总线。第二全局时钟总线是通过软件布线得出的,所以硬指标肯定比不过全局时钟总线的,特别是当你在已经有80%以上的布线率的情况下,可能会出现约束第二时钟资源失败的情况。

1.本文部分素材来源网络,版权归原作者所有,如涉及作品版权问题,请与我联系删除;

2.未经原作者允许不得转载本文内容,否则将视为侵权;

3.转载或者引用本文内容请注明来源及原作者;

4.对于不遵守此声明或者其他违法使用本文内容者,本人依法保留追究权等。

下面是我的个人微信公众号,关注【一个早起的程序员】精彩系列文章每天不断。

本文介绍了FPGA中的时钟资源,包括全局时钟和局部时钟的概念及其差异。全局时钟由BUFG驱动,确保全芯片范围内的时钟延迟和抖动最小,适合同步设计。而局部时钟由BUFR驱动,局限于IObank内。外部时钟输入需通过差分时钟引脚进入FPGA。合理利用这些资源对于FPGA设计的性能至关重要。

本文介绍了FPGA中的时钟资源,包括全局时钟和局部时钟的概念及其差异。全局时钟由BUFG驱动,确保全芯片范围内的时钟延迟和抖动最小,适合同步设计。而局部时钟由BUFR驱动,局限于IObank内。外部时钟输入需通过差分时钟引脚进入FPGA。合理利用这些资源对于FPGA设计的性能至关重要。

4082

4082

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?