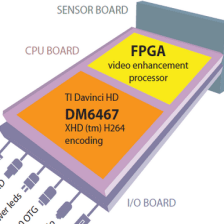

本文档系列是我在实践将神经网络实现到Xilinx 的zynq的FPGA上遇到的问题和解决方法。

背景:FPGA的片上BRAM空间较少,难以实现大量的存储。DDR的内存空间较多,若作为global memory将能实现很多问题。

目的:PS(片上ARM)通过MIG调用DDR

参阅的文档:DS176:Zynq-7000 AP SoC and 7 Series FPGAs Memory Interface Solutions Data Sheet

UG586: zynq-7000 AP Soc and 7 Series Devices Memory Interface Solutions

Xilinx zynq系列FPGA实现神经网络中相关资源评估

FPGA基础知识(六)UG586 Mermoy Interface Solutions

流程中其他步骤:

目录

一、创建工程

1.1 打开vivado, 创建工程,RTL project,板子选择xc7z035ffg676-2

1.2 创建block design

二、创建与定制MIG IP

2.1 添加MIG,双击MIG IP

2.2 默认一个控制器,AXI4接口

2.3 next,选DDR3 SDRAM(SDRAM:Synchronous Dynamic Random Access Memory,同步动态随机存储器,同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。)

2.4 默认设置800MHz时钟,然后修改Memory Part为MT41K256M16XX-125,这个在列表中靠下的位置,看清楚不要选错,Data Width选择32位,其他设置默认

2.5 AXI的Data Width选择64位和PS的HP接口对应,或者32位和GP接口对应。这里的data width表示AXI读与写的通道数

址线读写仲裁选择ROUND_ROBIN( Round Robin:轮询调度, 是一种以轮询的方式依次将一个域名解析到多个IP地址的调度不同服务器的计算方法。),其他默认

2.6 因为刚才选了800MHz和4:1,所以这里的输入时钟选择200MHz,这个时钟是PLL输入的时钟(CLKIN),其他默认

2.7 系统时钟来自于FPGA内部,这里选择No buffer,其他默认

2.8 内部终端电阻选择50欧姆

2.9 开发板是固定的,所以选择fixed pin out

2.10 选择read XDC/UCF,这个是管脚分配的文件,选择开发板默认的DDR管脚分布。

2.11 点击validate之后一直点next,最后accept,generate

三、定制processing system

3.1 加入ZYNQ7 processing system

3.2 双击IP进行配置,先应用开发板的配置(Zedboard),配置起来更快。

3.3 配置MIO,bank0配置为3.3V,bank1配制为1.8V

3.4 检查各个外设是否与MIZ7035的核心板匹配,MIO configuration中,IO peripherals中SD卡,WP信号没用,去掉

3.5 往下,eMMC需要添加SD1接口,CD和WP信号无用,不用添加

3.6 外设复位,GPIO中,ENET上电复位;USB复位在PL上,而这里只能选PS的MIO引脚,所以忽略;没有I2C,取消掉

3.7 DDR配置,Memory Part选择MT41K256M16RE-125,DQS to Clock Delay全部写0,Board Delay全部写0.25

3.8 Block Design,点击run block automation,建立PS的接口

3.9 创建clocking wizard

外部GCLK的100MHz时钟,因为直接接入了时钟引脚,选择Global Buffer

因为PL DDR3的参考时钟配置的是200MHz,这里让MMCM输出200MHz,并将Reset设置为低有效

四、搭建系统

4.1 对clock的接口进行连接

4.2 点击Run Connection Automation进行连接,

时钟选择/mig_7series_0/ui_clk(200MHz)

4.3 重新进行连线

4.4 分配地址

4.5 新建IO 约束文件,新建IO约束文件MIZ7035_IO.xdc,内容如下

create_clock -name clk100m_i -period 10.00 [get_ports clk100m_i]

set_property VCCAUX_IO DONTCARE [get_ports clk100m_i]

set_property IOSTANDARD SSTL15 [get_ports clk100m_i]

set_property PACKAGE_PIN C8 [get_ports clk100m_i]

set_property PACKAGE_PIN H7 [get_ports rst_key]

set_property IOSTANDARD SSTL15 [get_ports rst_key]

set_property PACKAGE_PIN K10 [get_ports init_calib_complete]

set_property IOSTANDARD SSTL15 [get_ports init_calib_complete]

这个文件用于对相应的管脚和板子进行约束,具体化相应的管脚。我们一定要让block design和这里的名称要保持一致。文件完成之后在加入add constraints

4.6 add constrians,create HDL wrapper,Generate output products.,generate

bitstream,生成相应的bit文件。

五、SDK

5.1 file-export-export hardware,需要包括相应的比特流

5.2 打开SDK,我的电脑用vivado直接打开SDK总是死机,所以我们直接打开SDK,目录改到之前vivado的目录下面,创建新的applicaiton project (这里非常需要注意,workspace、BSP、application project是很不同的)

这里注意点击new,添加之前的wrapper进入,wrapper在vivado生成的文件夹的xxx.sdk之中。

5.3 选择memory test(若是加入自己写的testBench就创建空的,然后把c程序拖进去)拖到project文件夹里面

六、用FPGA运行

6.1 编译工程

6.2 连接FPGA,注意要用JTAG线来连,并且也要连USB。

6.3 烧写比特流进入FPGA(FPGA每断电一次,就要重新烧写一次)或者在右键HW创建。

6.4 运行及结果

Xilinx zynq系列FPGA实现神经网络中相关资源评估

FPGA基础知识(六)UG586 Mermoy Interface Solutions

流程中其他步骤:

FPGA基础知识

FPGA基础知识(四)UG902 RTL simulation and export

FPGA基础知识(六)UG586 Mermoy Interface Solutions

vivado HLS硬件化指令

vivado HLS硬件化指令(一)HLS针对循环的硬件优化

vivado HLS硬件化指令(二)HLS针对数组的硬件优化

vivado HLS硬件化指令(三)HLS增大运算吞吐量的硬件优化

FPGA实践教程

631

631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?