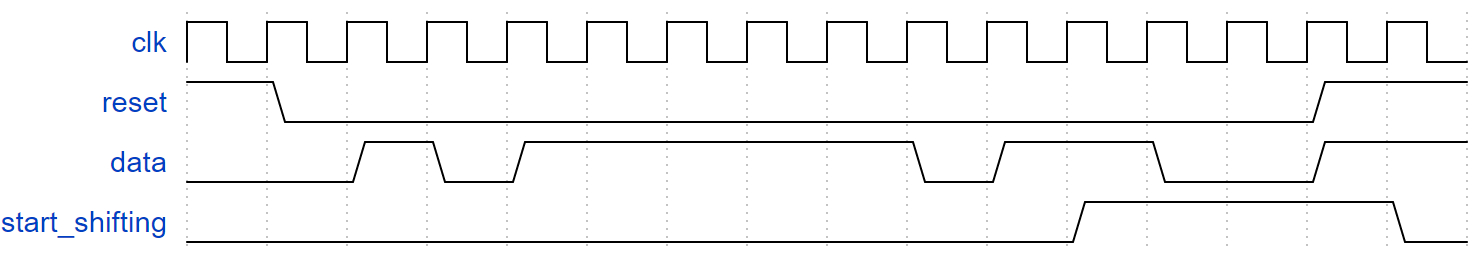

构造一个有限状态机检测data中的1101序列,如果检测到该序列,则将输出一直拉高直到同步复位信号为高。

module top_module (

input clk,

input reset, // Synchronous reset

input data,

output start_shifting);

parameter idle=3'd0;

parameter S0=3'd1;

parameter S1=3'd2;

parameter S2=3'd3;

parameter S3=3'd4;

reg shifting;

reg[2:0] state,next_state;

always@(*) begin

case(state)

idle:begin

next_state=data?S0:idle;

end

S0:begin

next_state=data?S1:idle;

end

S1:begin

next_state=data?S1:S2;

end

构造一个有限状态机检测data中的1101序列,如果检测到该序列,则将输出一直拉高直到同步复位信号为高。module top_module ( input clk, input reset, // Synchronous reset input data, output start_shifting); parameter idle=3'd0; parameter S0=3'd1; parameter S1=3'd2; ...

构造一个有限状态机检测data中的1101序列,如果检测到该序列,则将输出一直拉高直到同步复位信号为高。module top_module ( input clk, input reset, // Synchronous reset input data, output start_shifting); parameter idle=3'd0; parameter S0=3'd1; parameter S1=3'd2; ...

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6640

6640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?