数字IC后端设计实现面试问答

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

最近知识星球官方一直在做技术更新维护,似乎已经有一周时间了,导致了很多星友无法发帖提问,包括小编也无法发表任何主题,对此小编深表抱歉。在官方维护这段时间,各位星友可以私信提问(小编微信:ic-backend2018)。需要进数字 IC 后端技术交流微信群的,也可以先加小编微信,然后邀请进入。

对于此次的官方升级事件,小编更明白了一个道理,别人的平台是不靠谱的,不可控因素太多,自己的平台才是最可靠,最靠谱的。因此清明长假期间小编又在筹划搭建一个集问答系统(星球付费内容会慢慢迁移过来),技术交流论坛,技术干货分享,行业新闻动态为一体的综合性技术交流论坛。

另外,今年秋招也要开始了吧。小编今年打算帮助 5 位朋友找到他们理想中的工作,可以提供一对一的线上或者线下咨询指导服务。当然是有偿提供服务的,有需求的朋友可以私信。

好了,今天在高铁上就跟大家分享几道数字 IC 后端的面试题目。希望对各位求职,日常工作有所帮助。

1. report_clock_timing 和 report_timing 命令的理解

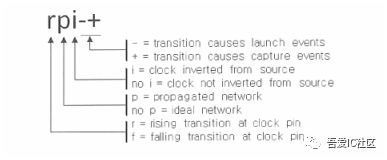

下面这个命令是 ICC/ICC2/PT 中非常常用的一个命令。主要用来 debug 和分析时钟树质量。请问,后面的 condition code 的含义?

这个命令还可以将 clock tree 展开,从而可以将该条 clock tree 在 layout 上高亮出来,更为直观地分析时钟树。

report_clock_timing -type latency –clock [get_clocks CLK1] -to [get_pins DFF1/CLK]

值得注意的是,这个命令是不考虑 OCV 即整体 path 上的 delay 值是不含 derating 值。

而 report_timing –to [get_pins DFF1/D] 则是考虑 OCV 效应的。很多粉丝经常咨询为何时钟树的 log 文件上显示 clock skew 就 60ps 左右,而从报出来的 timing path 上看 local skew 高达 200ps 左右。主要原因还是没搞懂这两个命令的区别和联系。

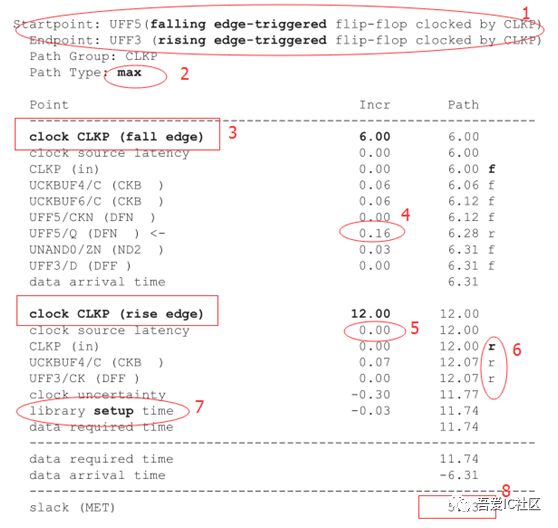

下面这个 report 是通过 report_timing 报出来的一条 path,图中标出的八个地方是特别需要关注的点,作为一个数字后端工程师一看到这样的 report,就要一眼就能看出这条 timing path 是从一个负沿的寄存器到另外一个正沿寄存器的数据端的 setup 检查,而且是属于half cycle 的 timing check,且时钟周期 T=12ns。其他标出的地方希望大家都能搞明白。

总之,要想学会 debug 分析问题,首先得懂工具,理解工具的行为。否则就像无头苍蝇,没有方向,碰到问题无从下手。一定要学会抓住主要矛盾,快速找到问题的线索,从而快速解决问题。

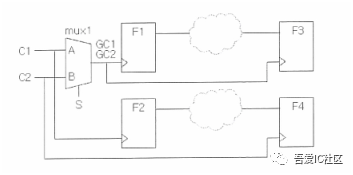

2. 请为为下面的电路结构编写 SDC 约束文件。其中 C1 为系统工作时钟,C2 为测试时钟。C1 的周期为 1.5ns,C2 的周期为 2.0ns。

Alias cgc “create_generated_clock”

首先需要定义两个时钟 C1 和 C2。

create_clock -name C1 -period 1.5 [get_ports C1]

create_clock -name C2 -period 2.0 [get_ports C2]

其次,在 MUX 的输出端再定义两个 generated 时钟,GC1 和 GC2。

cgc -name GC1 -source [get_pins mux1/A] [get_pins mux1/Z] -combinational

cgc -name GC2 -source [get_pins mux1/B] [get_pins mux1/Z] –combinational -add

最后声明时钟之间的关系,通过 set_clock_group 来实现(早期是通过 set_false_path 来实现的)。

set_clock_group -physically_exclusive -group GC1 -group GC2

set_clock_group -logically_exclusive -group C1 -group C2

留个思考题。两个时钟,设置 false_path 和 asyn group,它们的区别和联系是什么?(这道题是当年公司招数字后端 manager 时出的)

3. 做 cts 时没有做 balance 的设置,之后发现有两条时钟 global skew 很大,超过 1,同时 latency 很大。检查了步骤: 1,报了 local skew, 最大 1,最小 - 1, 可以肯定 cts 没有长好 2,报了 net fanout,发现好多地方超过了 50,这应该是前端给的网表有问题 3,报了时钟结构, 出问题的两条确实 cell 比较多,但是 level 不多,只有 16 级左右。 4,退回到 place,发现 place 之后,global skew 就很大了。place 阶段长 tree 了请问最可能哪步出了问题,另外 place 阶段能控制不长 tree 么?怎么设置?

-

可以通过 report_clock_timing -type -to 来分别报下最长和最短的两条 path。

-

前端不会帮你解 fanout 的,place 阶段会解的,除非你设置 set_ideal_network 了。

-

时钟树级数多少不能说明问题,这个和 design 相关。需要分析这两条有问题的时钟树是否是被别人拖长?还是因为窄 channel?等等。。。

-

place 阶段不会长 tree 的,都是 ideal 的。正常 flow 默认都不会长 tree 的,icc/icc2 有个变量会做 trial cts,那是用了 CCD 的选项。

ICC 使用 CCD 时设置命令参考如下:

set_concurrent_clock_and_data_strategy-ignore_boundary_path_timing true -add_to_existing_float_pins true-adjust_boundary_registers true

report_concurrent_clock_and_data_strategy

set skew_opt_optimize_clock_gates true

set update_clock_latency_consider_float_pin_delays true

clock_opt-only_psyn -concurrent_clock_and_data -area_recovery -congestion-no_clock_route -power

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有165位星球成员,感谢这 165 位童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。(星球的门票即将调整到 228 元 / 年,有需求的朋友趁早上车,**目前价格已经提高至 208 元 / 年,折算每天需要六毛钱 **)

很久没放出公众号链接了,很多芯朋友表示找不到关注入口。赶紧扫码或者长按图片关注起来吧!(其实点击文章顶部蓝色文字即可快速关注哦)

273

273

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?