大家在跑完物理验证calibre DRC之后,会发现DRC里面存在一种G4:M7i的DRC违例,这种违例一般都是出现在memory的边界。今天教大家如何利用脚本来批量处理这一类DRC问题的解决。

首先,我们需要把calibre的DRC结果读取到innovus里面来,具体的方法参考下面这份教程。

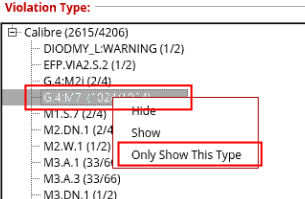

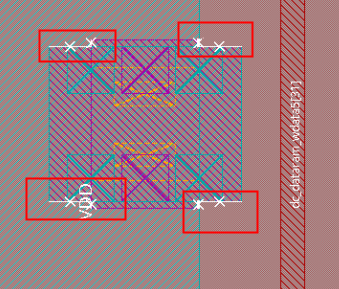

按照上面教程提供的方法加载了calibre drc报告之后,我们可以点击G4:M7i,然后鼠标右键点击一下,在点击Only Show This Type,这样整个版图上就只剩下这个类型的DRC高亮,方便我们判断问题的位置。

数字IC后端设计实现之Innovus自动修复Min Step DRC Violation方案

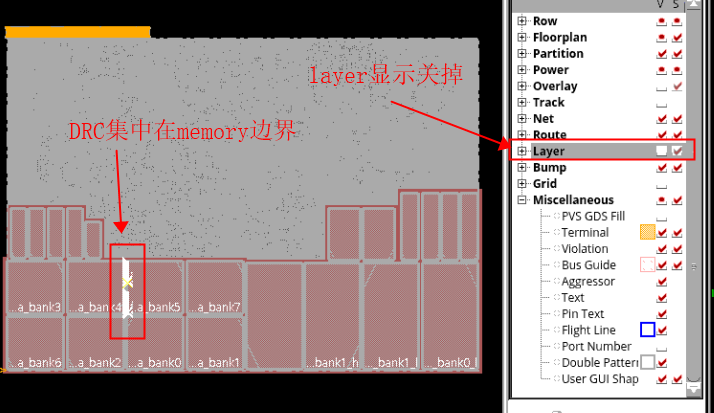

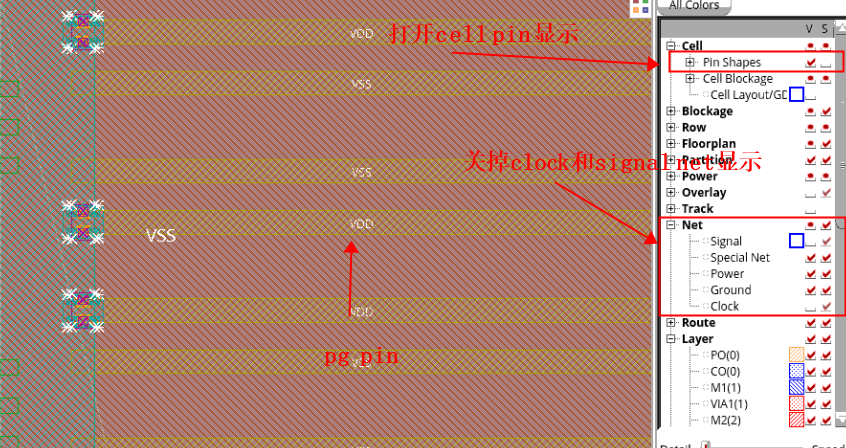

大家可以按照下面的layer设置,只保留pg的net显示,可以看到这个drc问题的详细情况。

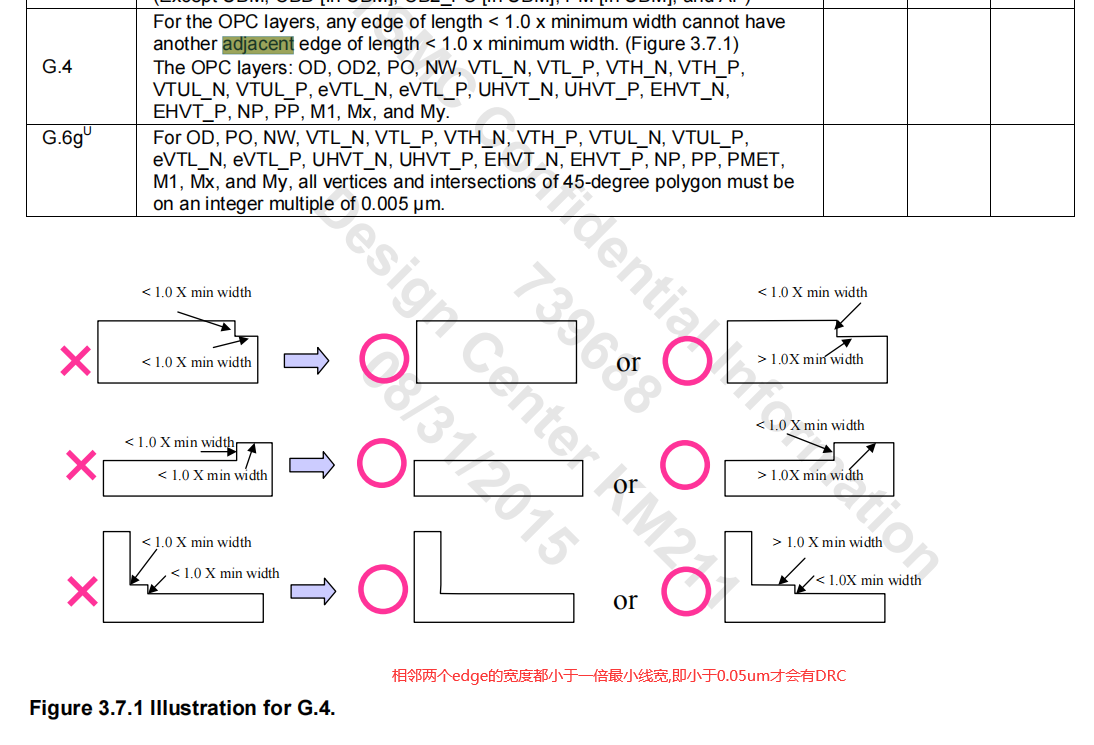

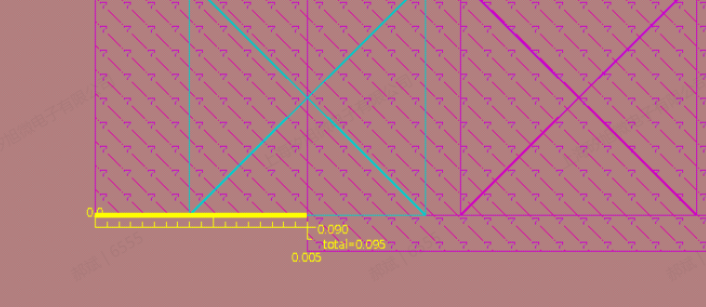

这个DRC的规则可以看下面这份教程,其核心的要点就是凹槽里面必须要有一个边需要大于最小线宽

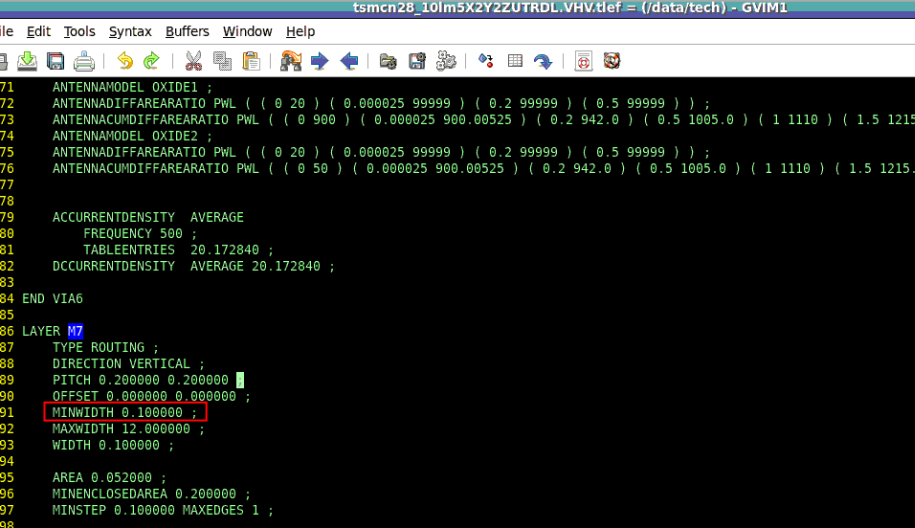

而这一层是M7层,通过tlef文件可以查到M7层的最小线宽是0.1um,而可以量到这个via凹槽里面最长边也才0.9um,这个显然就不满足最小线宽的要求的,所以会报DRC Violation。

数字IC后端物理验证PV | TSMC 12nm Calibre Base Layer DRC案例解析

而解决这个问题一般我们都是选择把这个via删掉就可以,因为memory身上一般都有足够的via来保证供电,边上这些via并不影响实际的供电情况。下面就是具体的脚本

set drc_boxes [dbget [dbget top.markers.userType G.4:M7i -p].box]

foreach box $drc_boxes {

deselectAll

select_obj [ dbQuery -area $box -objType sViaInst]

editDelete -selected

}

我们可以通过markers.userType这个属性去获取G.4:M7i这个DRC的具体坐标,然后再通过dbQuery这个命令在每个坐标上去获取坐标上的sViaInst,只要是pg上的via,都属于sViaInst。同时dbQuery这个命令,指定坐标的时候,只要我们指定的object跟这个坐标有一点搭边,都会被输出,然后我们就可以选择这些pg via,用editDelete -selected命令把这些via全部删除。

最后的效果如下图所示,via7就被删掉了,这样再输出gds去检查DRC,就不会再报G4:M7i这个问题了。

2427

2427

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?