https://www.xilinx.com/video/hardware/using-the-non-project-batch-flow.html --video

https://github.com/byu-cpe/BYU-Computing-Tutorials/wiki

https://cloud.tencent.com/developer/article/1169476

没有post_route_phys_opt_design

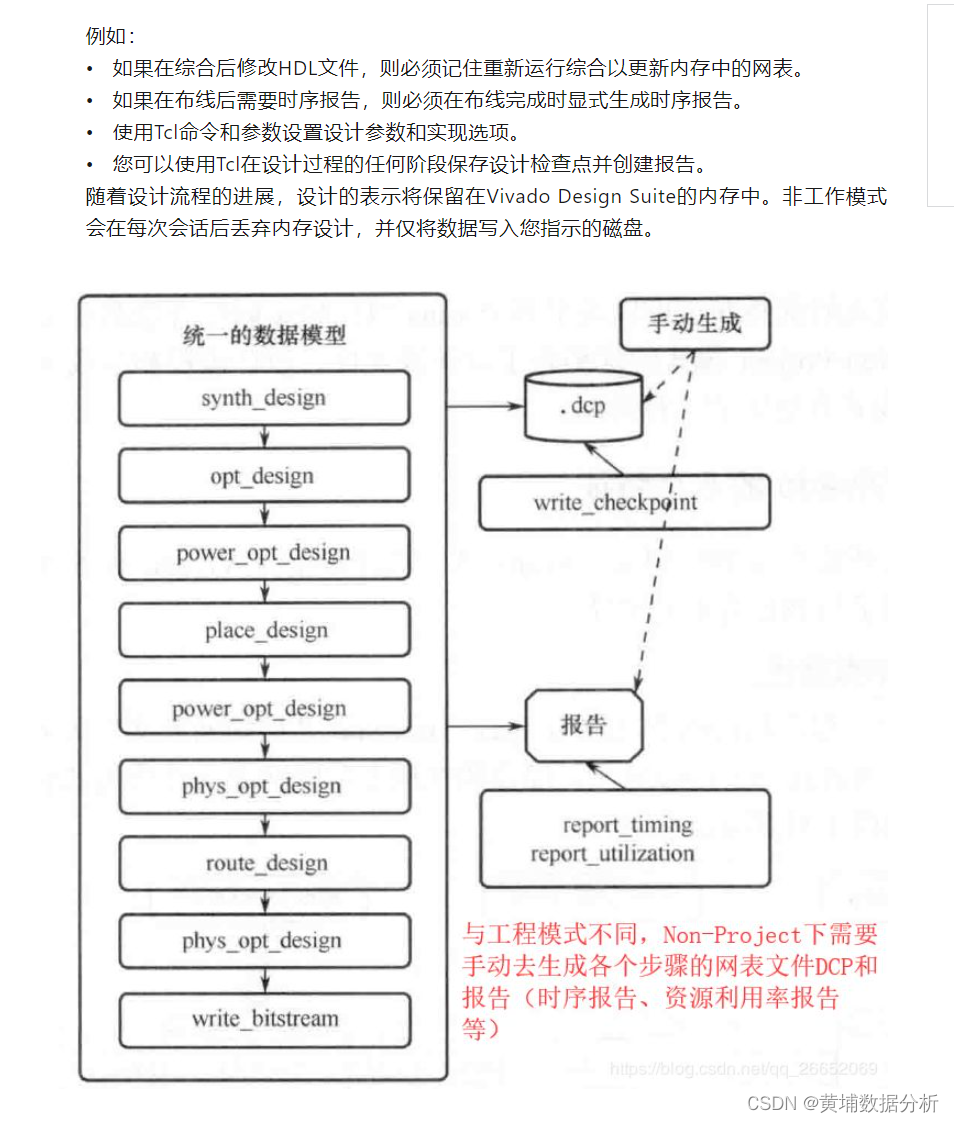

为了更加快捷的完成non-project的tcl内容,我们可以先把wavegen工程进行Synthsis和Implementation,在wavegen.runs下面会生成synth_1和impl_1的两个目录,这两个目录都有wavegen.tcl,我们可以直接将里面的有用内容copy出来,用来创建non-project的tcl,具体操作就不展开细讲了,直接把最终的tcl文件展示出来,就很很容易理解了:

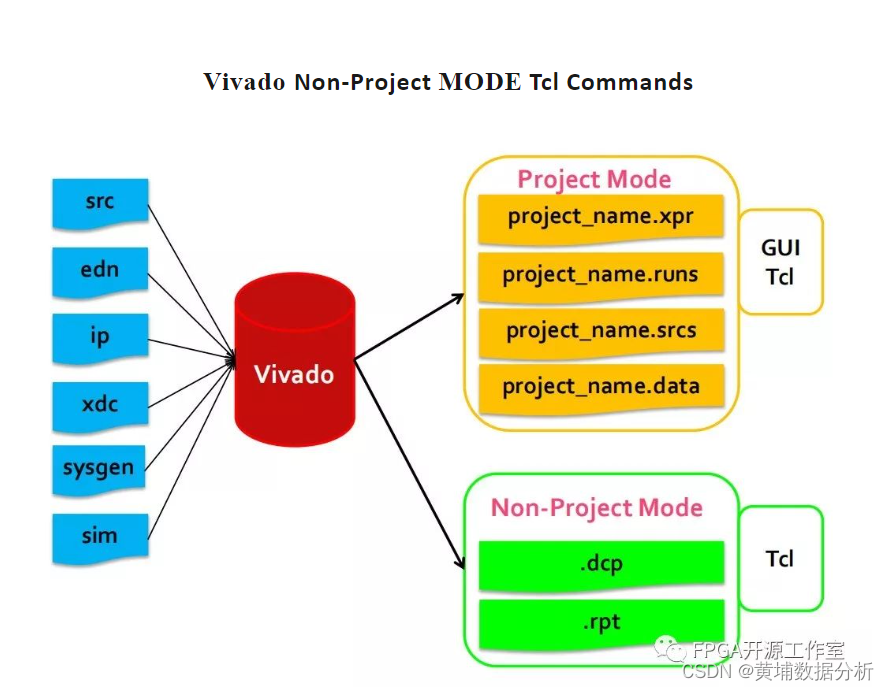

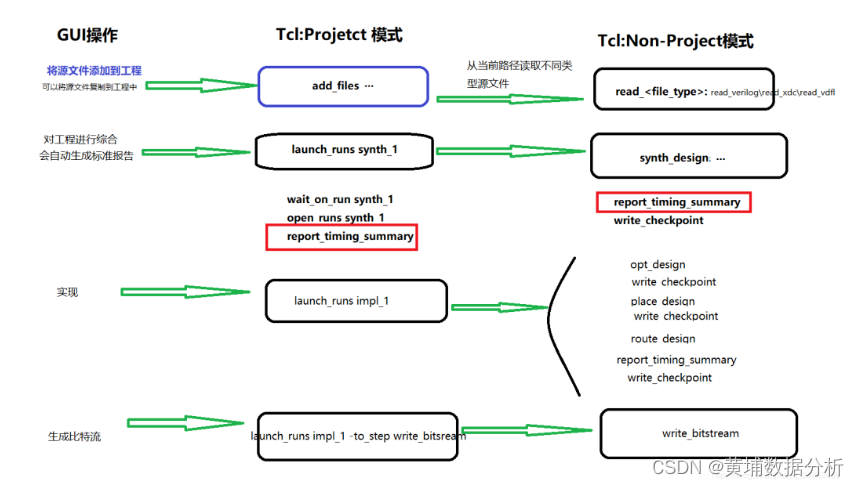

project 和non-project 模式的tcl大部分不一样

从中间开始跑tcl

open_checkpoint synth.dcp

opt_design

place_design

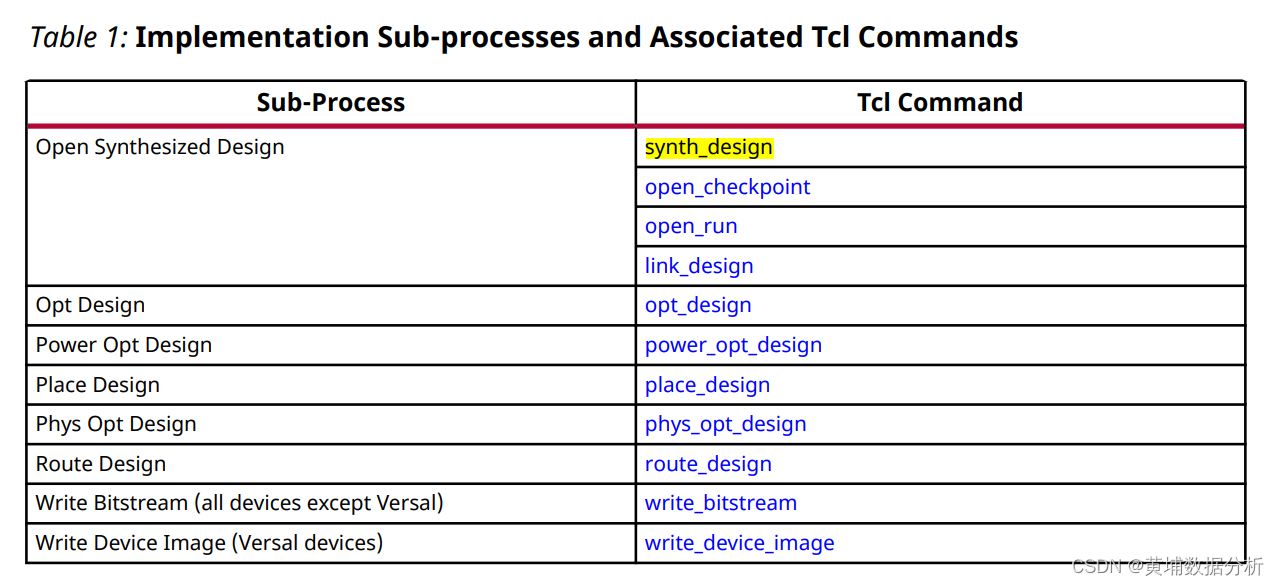

route_design

可以,但要注意的是如果包含OOC的IP,综合后的synth dcp还不够,需要在opt_design之前和IP dcp一起做link_design。如果你之前就是综合完直接跑opt_design,那是OK的。

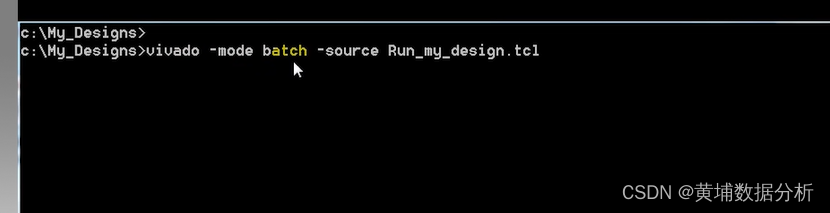

run_my_design.tcl

demo

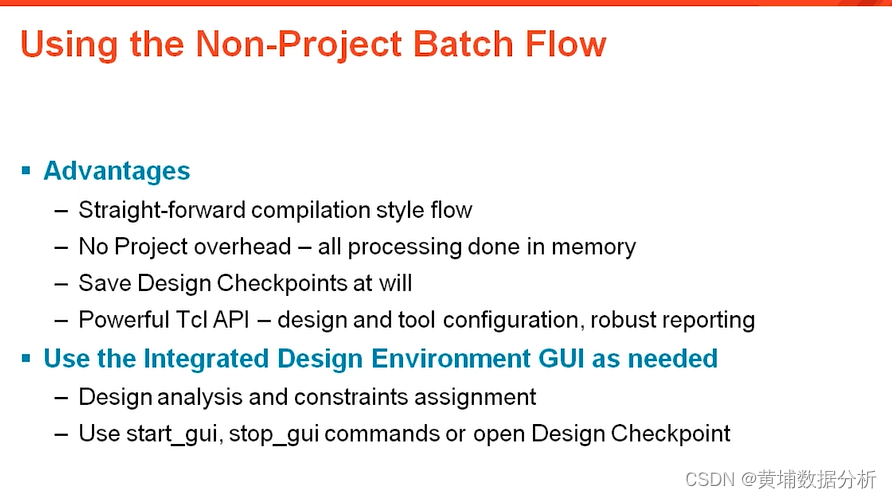

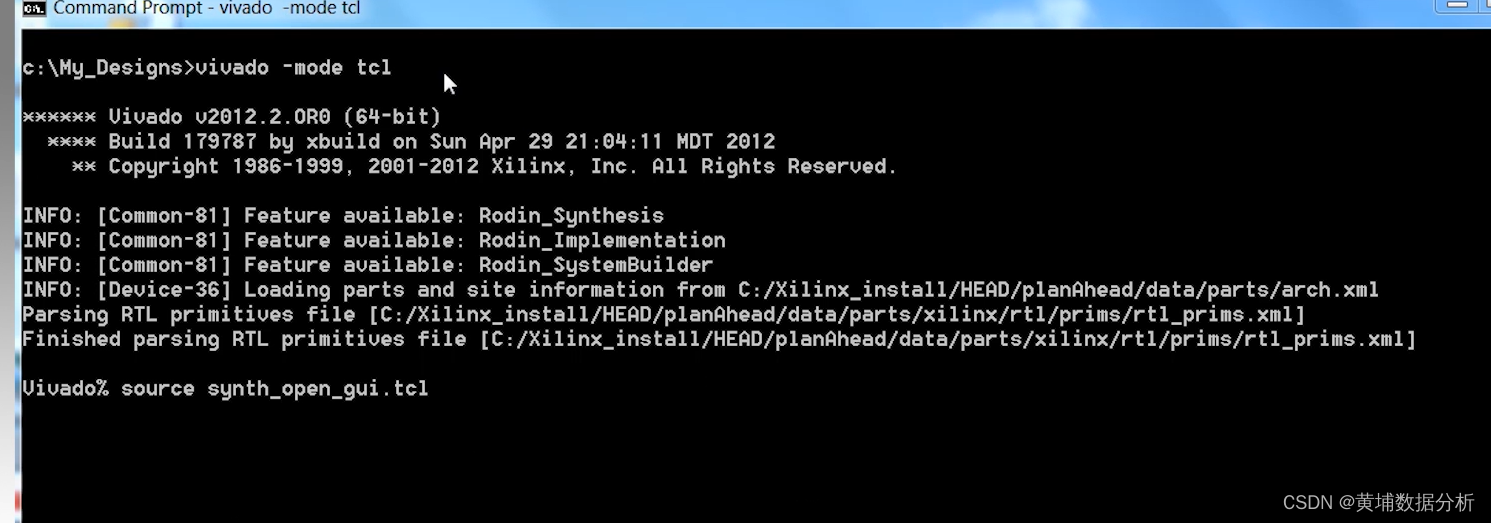

交互模式 start_gui stop_gui

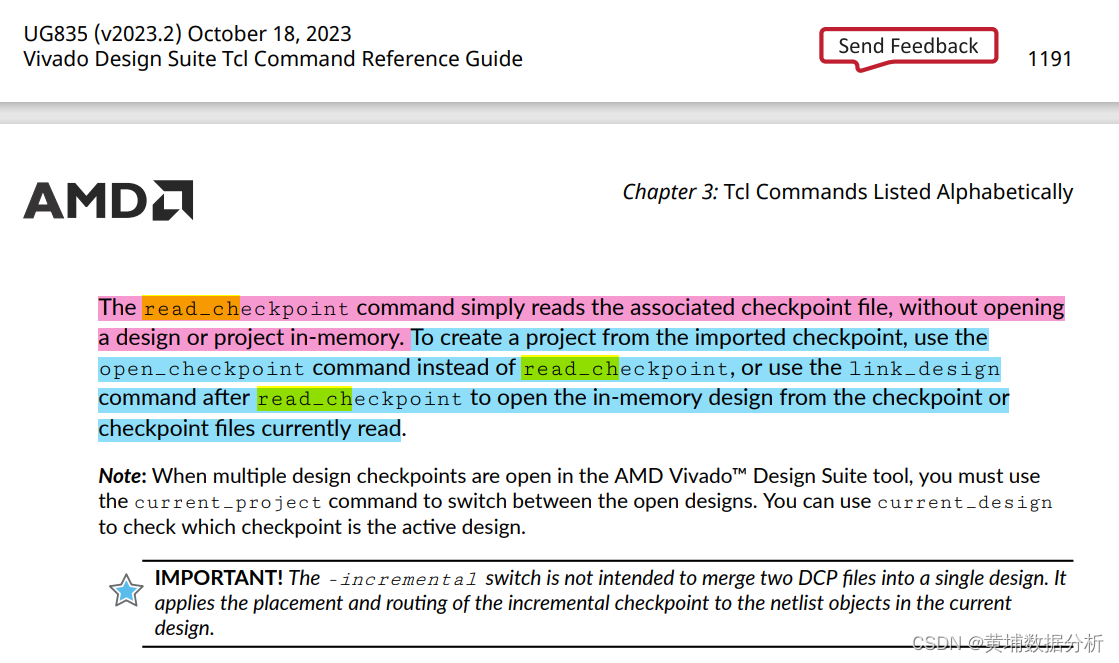

read_checkpoint VS open_checkpoint

read_checkpoint:

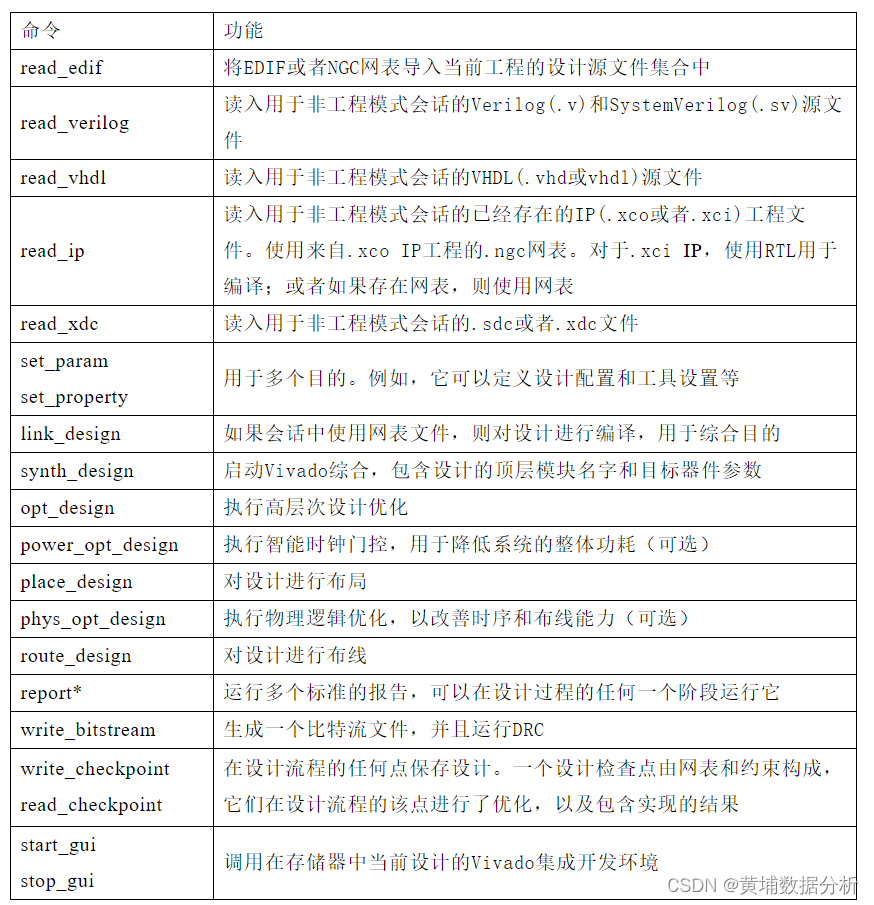

该命令用于简单读取dcp文件,并不会打开设计或者in-memory工程,如果需要打开设计,则需要使用命令link_design,举例如下:

read_checkpoint C:/Data/checkpoint.dcp

link_design -name Test1

如果在一个vivado tool中打开了多个dcp文件,则需要使用current_project命令来切换设计。

current_project project2

可以通过get_projects来查看当前已经打开的projects。

get_projects

open_checkpoint:

打开一个dcp文件,并创建一个新的in-memory工程并立即用dcp文件内容对其进行初始化。

open_checkpoint C:/Data/state1/checkpoint.dcp -part xc7k325tffg900-2

write_hw_platform 指定pdi

要包含实现后的 PDI,write_hw_platform 要求此 PDI 文件存在于 project.runs/impl_1/ 目录内。如果在布局布线进程中,未在该文件夹内生成实现后 PDI,那么它将不包含在 XSA 中。

在此情况下,您可在运行 write_hw_platform 前使用以下命令来更改默认 PDI 查找路径。

set_property platform.full_pdi_file path_to_post_impl.pdi [current_project]

demo

# 还有问题

set part xcvc1902-vsva2197-2MP-e-S

set_part $part

set_param general.maxthreads 8

# set dir

set outputDir ./my_design_output

file mkdir $outputDir

# create_project -force -dir $TOP_UNIT_DIR -name $TOP_UNIT -part $PART

# import files

# read_verilog -sv xxx.sv

# read_verilog [ glob ./sources_1/imports/new/*.v ]

read_verilog ./../src/hdl/design_1_wrapper.v

read_xdc ./../src/xdc/vck190_top.xdc

#read_bd ./../src/bd/design_1.bd

#

set_property IP_REPO_PATHS ../iprepos/ [current_fileset ]

update_ip_catalog

source ../src/bd/design_1.tcl

generate_target all [get_files ./src/bd/design_1/design_1.bd]

read_verilog ./src/bd/design_1/synth/design_1.v

# run synth & impl

synth_design -top design_1_wrapper -part $part -flatten rebuilt -retiming 1

write_checkpoint -force $outputDir/post_synth

report_utilization -file $outputDir/post_synth_util.rpt

report_timing -sort_by group -max_paths 5 -path_type summary -file $outputDir/post_synth_timing.rpt

opt_design -directive Explore

power_opt_design

place_design

write_checkpoint -force $outputDir/post_place

phys_opt_design

route_design

write_checkpoint -force $outputDir/post_route

#Generate Reports

#

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/cpu_imp_netlist.v

write_xdc -no_fixed_only -force $outputDir/cpu_imp.xdc

#Generate Bit File

#

#

write_bitstream - file $outputDir/design.pdi

write_hw_platform -fixed -force -file $outputDir/my.xsa

# 参考

# ======================================================== //

# FileName : build.tcl

# Author : Zhang Haijun

# Version : v1.0

# Discription : vivado -mode batch -source build.tcl

# ======================================================== //

#!/usr/bin/tclsh

set_param general.maxthreads 8

set_part xcku035-fbva900-2-e

# read files

read_verilog /home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/clogb2.vh

read_verilog -library xil_defaultlib {

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/clk_div.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/clk_gen.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/clkx_bus.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/cmd_parse.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/dac_spi.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/debouncer.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/lb_ctl.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/meta_harden.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/out_ddr_flop.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/reset_bridge.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/resp_gen.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/rst_gen.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/samp_gen.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/samp_ram.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/to_bcd.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/uart_baud_gen.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/uart_rx.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/uart_rx_ctl.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/uart_tx.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/uart_tx_ctl.v

/home/henry/fpga/wavegen/wavegen.srcs/sources_1/imports/Sources/kintexu/wave_gen.v

}

# read ip

read_ip -quiet /home/henry/fpga/wavegen/wavegen.srcs/sources_1/ip/clk_core/clk_core.xci

read_ip -quiet /home/henry/fpga/wavegen/wavegen.srcs/sources_1/ip/char_fifo/char_fifo.xci

# read constraints

read_xdc /home/henry/fpga/wavegen/wavegen.srcs/constrs_1/imports/xcku035-fbva900-2-e/wave_gen_timing.xdc

read_xdc /home/henry/fpga/wavegen/wavegen.srcs/constrs_1/imports/xcku035-fbva900-2-e/wave_gen_pins.xdc

# generate ips

generate_target all [get_ips]

# synthesize design

synth_design -top wave_gen -part xcku035-fbva900-2-e

write_checkpoint -force -noxdef synth.dcp

# opt_design

opt_design

write_checkpoint -force opt.dcp

# place design

place_design

write_checkpoint -force placed.dcp

phys_opt_design

write_checkpoint -force physopt.dcp

# route design

route_design

write_checkpoint -force routed.dcp

report_timing_summary -max_paths 10 -report_unconstrained -file wave_gen_timing_summary_routed.rpt -pb wave_gen_timing_summary_routed.pb -rpx wave_gen_timing_summary_routed.rpx -warn_on_violation

#write bitfile

write_bitstream -force ./wave_gen.bit

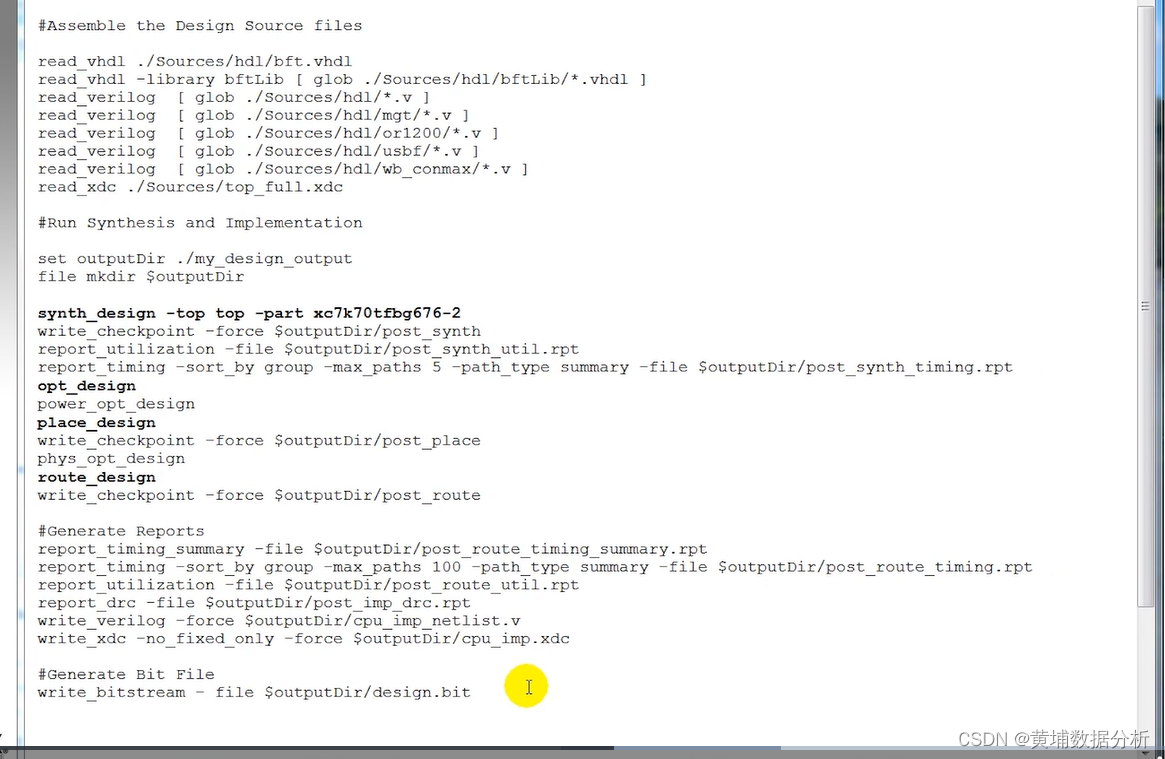

#Following is an example of a Non-Project Mode script, which reads in various source files:

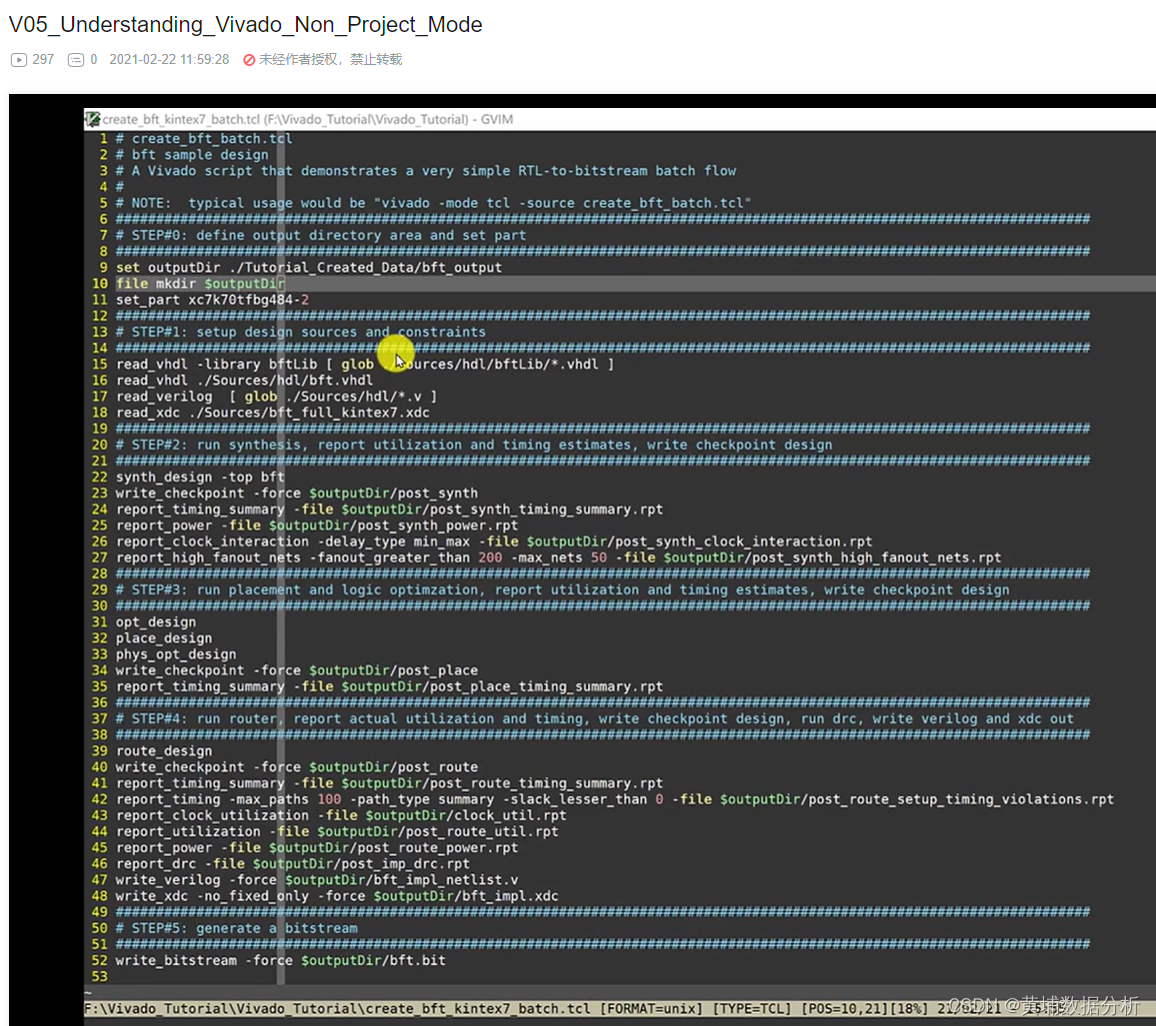

# create_bft_batch.tcl

# bft sample design

# A Vivado script that demonstrates a very simple RTL-to-bitstream batch flow

#

# NOTE: typical usage would be "vivado -mode tcl -source create_bft_batch.tcl"

#

# STEP#0: define output directory area.

#

set outputDir ./Tutorial_Created_Data/bft_output

file mkdir $outputDir

#

# STEP#1: setup design sources and constraints

#

read_vhdl -library bftLib [ glob ./Sources/hdl/bftLib/*.vhdl ]

read_vhdl ./Sources/hdl/bft.vhdl

read_verilog [ glob ./Sources/hdl/*.v ]

read_xdc ./Sources/bft_full.xdc

#

# STEP#2: run synthesis, report utilization and timing estimates, write checkpoint

design

#

synth_design -top bft -part xc7k70tfbg484-2 -flatten rebuilt

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

#

# STEP#3: run placement and logic optimzation, report utilization and timing

estimates, write checkpoint design

#

opt_design

place_design

phys_opt_design

write_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

#

# STEP#4: run router, report actual utilization and timing, write checkpoint design,

run drc, write verilog and xdc out

#

route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -sort_by group -max_paths 100 -path_type summary -file

$outputDir/post_route_timing.rpt

report_clock_utilization -file $outputDir/clock_util.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/bft_impl_netlist.v

write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

#

# STEP#5: generate a bitstream

#

write_bitstream -force $outputDir/bft.bit

#2.1定义文件输出位置

set outputDir ./output

file mkdir $outputDir

set_part xc7k160tfbg676-2

##########2.2 加入设计文件和约束

read_verilog [ glob ./sources_1/imports/new/*.v ]

read_ip [ glob ./sources_1/ip/PLL50MTo100M/*.xci]

read_ip [ glob ./sources_1/ip/Pll50MTo148M5Drg90/*.xci]

read_ip [ glob ./sources_1/ip/vio_0/*.xci]

read_xdc [ glob ./constrs_1/imports/new/*.xdc ]

##############2.3 进行综合,报告利用率,时序检测,写DCP文件

synth_design -top VS2Top

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

report_clock_interaction -delay_type min_max -file $outputDir/post_synth_clock_interaction.rpt

report_high_fanout_nets -fanout_greater_than 200 -max_nets 50 -file $outputDir/post_synth_high_fanout_nets.rpt

#######2.4 布局和逻辑优化,报告,时序检测,写DCP

opt_design

place_design

phys_opt_design

write_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

##########2.5 布线和逻辑优化,报告,时序检测,写DCP,DRC检查,xdc锁定

route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -max_paths 100 -path_type summary -slack_lesser_than 0 -file $outputDir/post_route_setup_timing_violations.rpt

report_clock_utilization -file $outputDir/clock_util.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/project_impl_netlist.v

write_xdc -no_fixed_only -force $outputDir/project_impl.xdc

#产生比特流

write_bitstream -force $outputDir/VS2Top.bit

# build settings

set design_name "pong"

set arch "xc7"

set board_name "arty"

set fpga_part "xc7a35ticsg324-1L"

# set reference directories for source files

set lib_dir [file normalize "./../../../../lib"]

set origin_dir [file normalize "./../../"]

# read design sources

read_verilog -sv "${lib_dir}/clock/xc7/clock_480p.sv"

read_verilog -sv "${lib_dir}/essential/debounce.sv"

read_verilog -sv "${origin_dir}/${arch}/top_${design_name}.sv"

read_verilog -sv "${origin_dir}/simple_480p.sv"

read_verilog -sv "${origin_dir}/simple_score.sv"

# read constraints

read_xdc "${origin_dir}/${arch}/${board_name}.xdc"

# synth

synth_design -top "top_${design_name}" -part ${fpga_part}

# place and route

opt_design

place_design

route_design

# write bitstream

write_bitstream -force "${origin_dir}/${arch}/${design_name}.bit"

# A Vivado script that demonstrates a very simple RTL-to-bitstream batch flow

#

# NOTE: typical usage would be "vivado -mode tcl -source create_bft_batch.tcl"

#

# STEP#0: define output directory area.

#

set outputDir ./out/output

file mkdir $outputDir

# STEP#1: setup design sources and constraints

#

read_vhdl -library work [ glob ./src/*.vhd ]

read_xdc [ glob ./src/*.xdc ]

set_property PART xc7z015clg485-2 [current_project]

# Set project properties

set obj [current_project]

set_property "default_lib" "xil_defaultlib" $obj

set_property "part" "xc7z015clg485-2" $obj

set_property "simulator_language" "Mixed" $obj

set_property "target_language" "VHDL" $obj

#set ip repository path

set_property IP_REPO_PATHS ./ip_rep [current_fileset ]

update_ip_catalog

# create the BD-Design

source setup_bd.tcl

generate_target all [get_files .srcs/sources_1/bd/design_1/design_1.bd]

read_vhdl -library work [ glob .srcs/sources_1/bd/design_1/hdl/design_1.vhd ]

# STEP#2: run synthesis, report utilization and timing estimates, write checkpoint design

#

synth_design -top system_top -part xc7z015clg485-2 -flatten rebuilt

write_checkpoint -force $outputDir/post_synth

report_timing_summary -file $outputDir/post_synth_timing_summary.rpt

report_power -file $outputDir/post_synth_power.rpt

# STEP#3: run placement and logic optimzation, report utilization and timing estimates, write checkpoint design

#

opt_design

place_design

phys_opt_design

write_checkpoint -force $outputDir/post_place

report_timing_summary -file $outputDir/post_place_timing_summary.rpt

# STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out

#

route_design

write_checkpoint -force $outputDir/post_route

report_timing_summary -file $outputDir/post_route_timing_summary.rpt

report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt

report_clock_utilization -file $outputDir/clock_util.rpt

report_utilization -file $outputDir/post_route_util.rpt

report_power -file $outputDir/post_route_power.rpt

report_drc -file $outputDir/post_imp_drc.rpt

write_verilog -force $outputDir/bft_impl_netlist.v

write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

# STEP#5: generate a bitstream

#

write_bitstream -force $outputDir/bft.bit

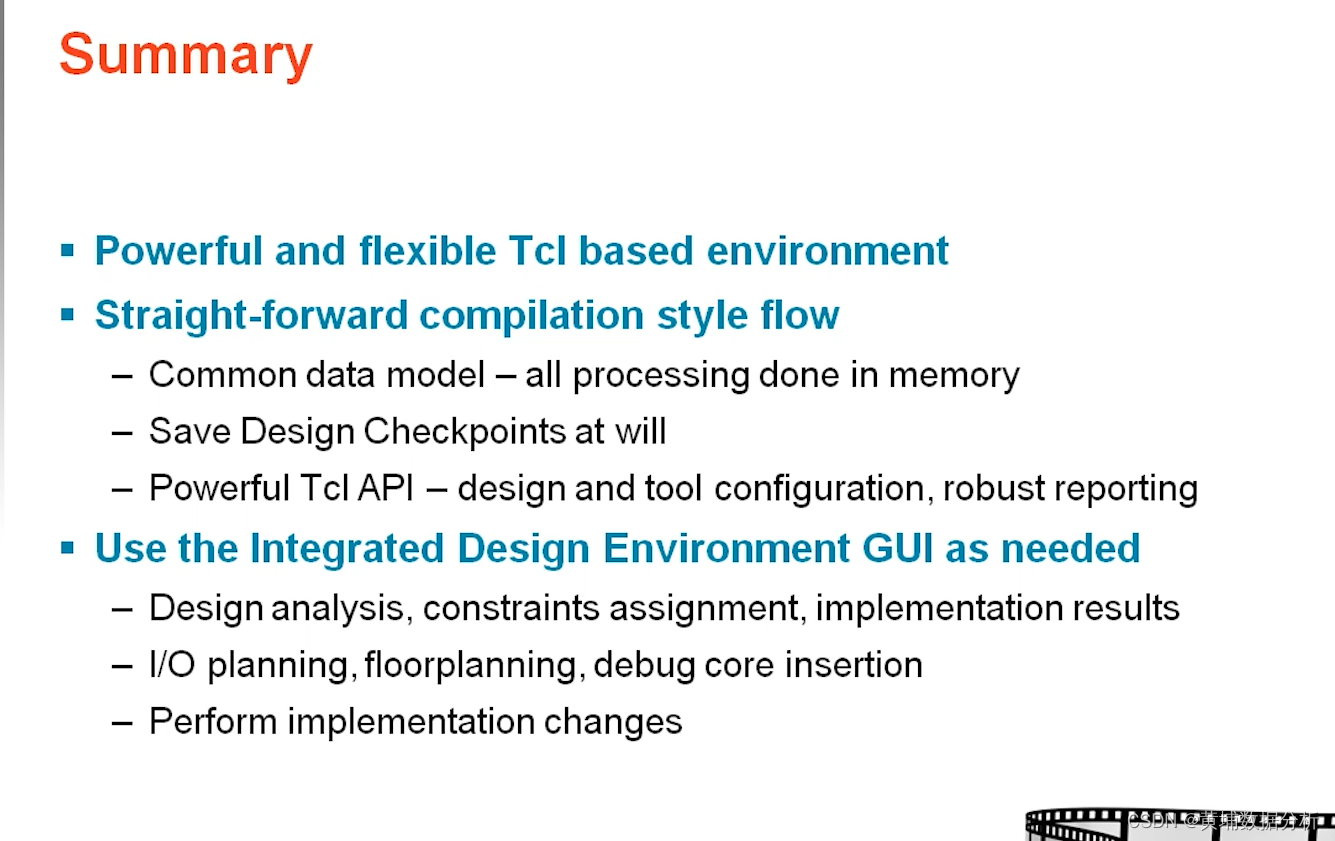

本文详细介绍了如何在Vivado中使用非项目模式批量流程,涉及从Synthesis到PhysicalOptimization,包括使用wavegen工程的合成和实施结果创建自定义TCL脚本,以及各个设计阶段的关键步骤和注意事项。

本文详细介绍了如何在Vivado中使用非项目模式批量流程,涉及从Synthesis到PhysicalOptimization,包括使用wavegen工程的合成和实施结果创建自定义TCL脚本,以及各个设计阶段的关键步骤和注意事项。

1059

1059

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?