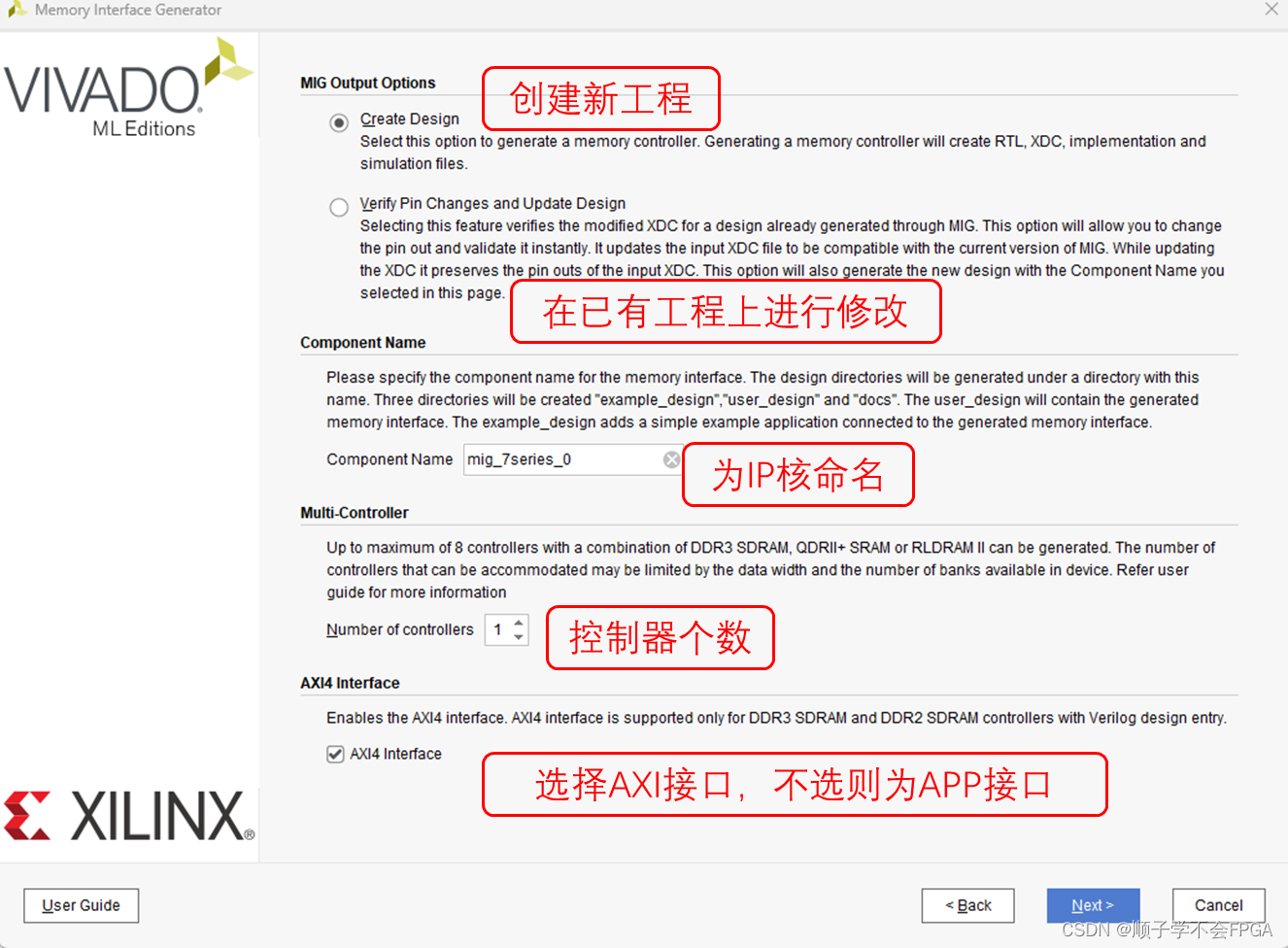

一、MIG IP核配置详解

1、第一页

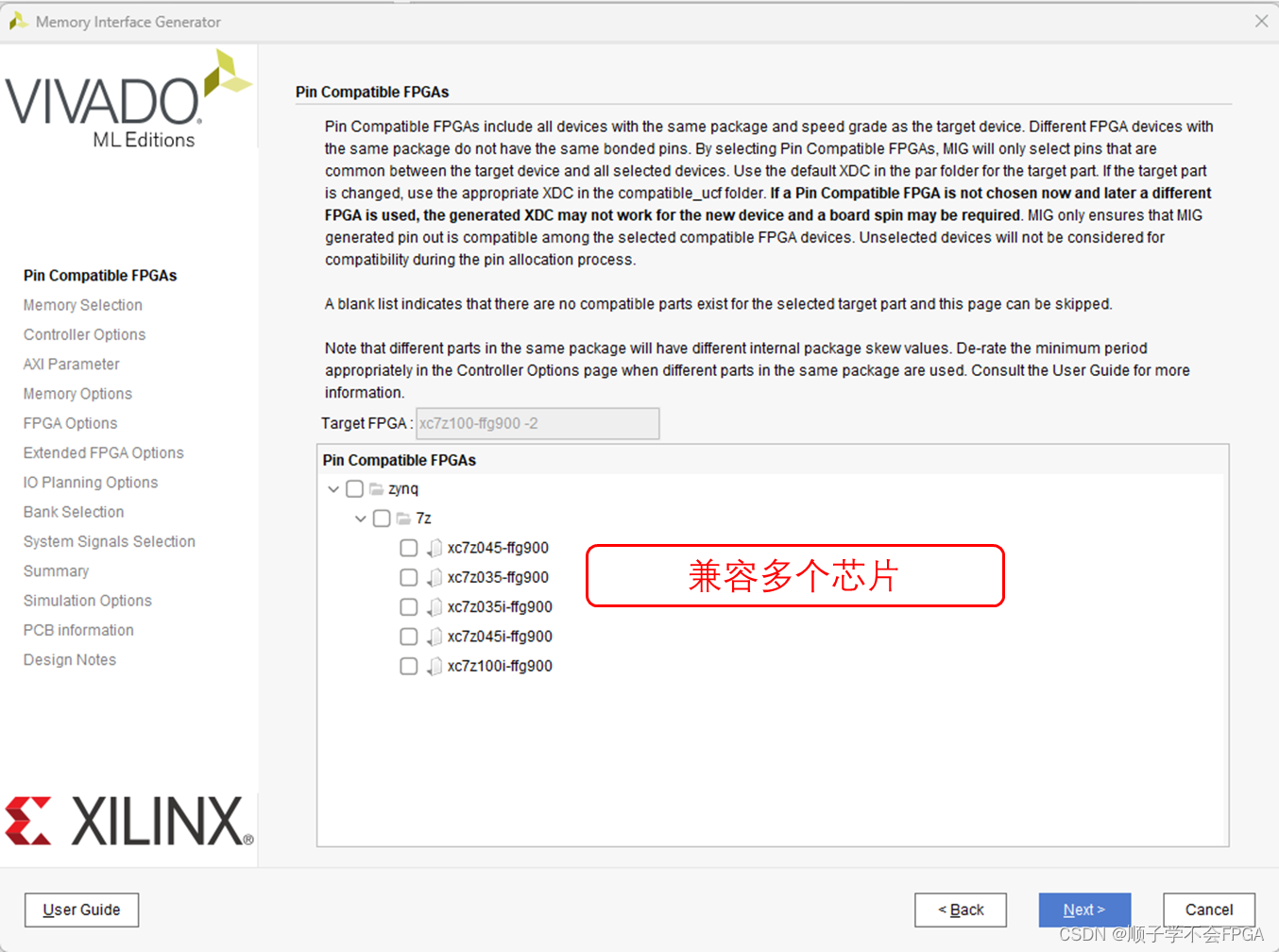

2、第二页

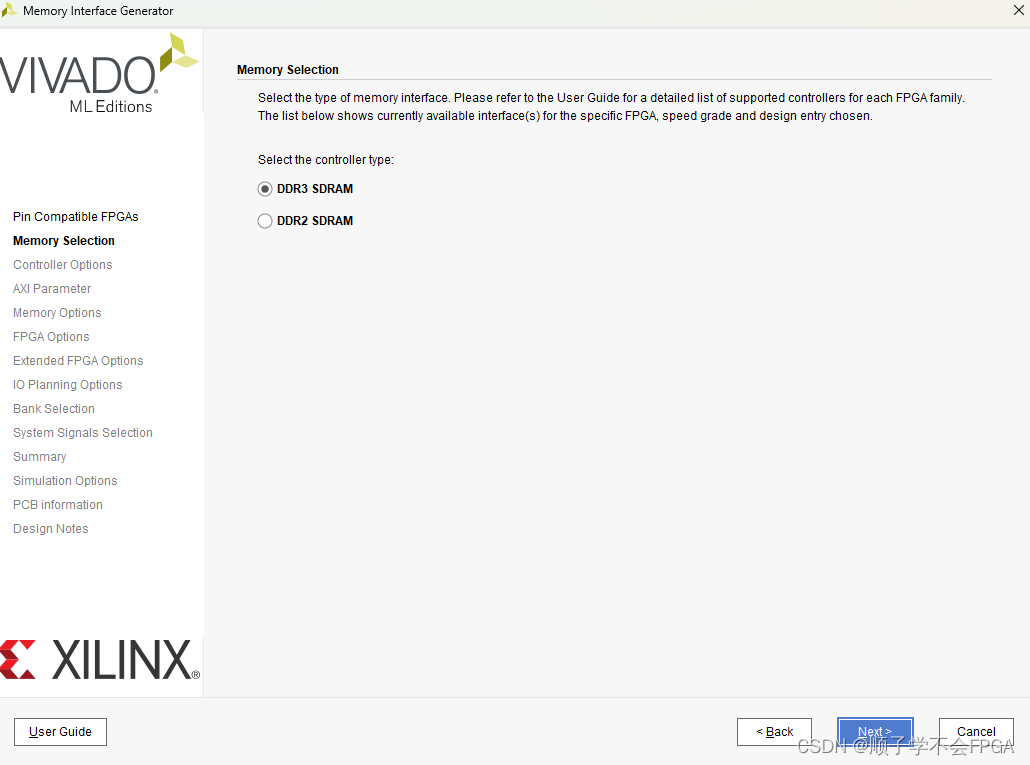

3、第三页

类型选择DDR3

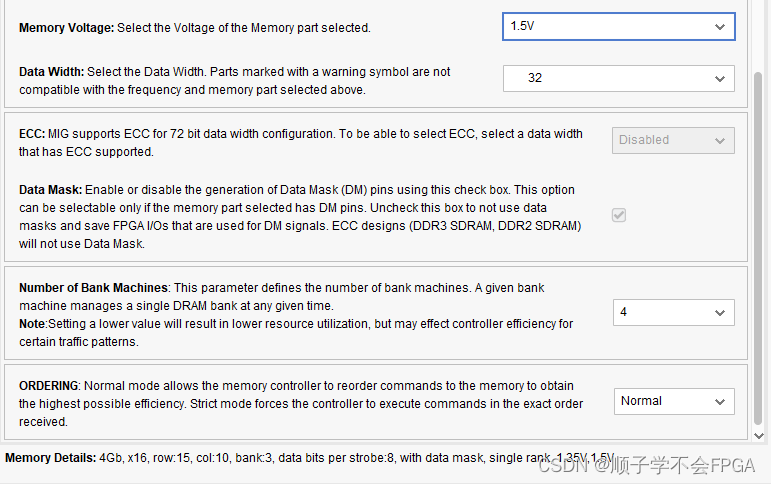

4、第四页

Clock Period:DDR3芯片运行的时钟速率,该数值的范围和FPGA芯片以及具体速度类型有关系。我使用的是XC7Z100,可以支持1250ns,即800Mhz。这个时钟是由MIG IP和产生的,并输出给DDR3物理芯片使用,它关系到DDR3的运行带宽,我使用的FPGA板卡有俩颗DDR3芯片,数据位宽分别是16bit,一共为32bit,由于双沿采样,数据速率是时钟速率的俩倍,即1600Mhz,带宽为1600Mhz * 32bit。

PHY to Controller Clock Ratio:DDR3物理芯片运行时钟与MIG IP核用户端(FPGA)的时钟之比,此处DDR3时钟为800Mhz,所以MIG IP 核用户时钟(ui_clk)为200Mhz,一般来说有2:1和4:1俩种,高速传输只适合4:1,要求低时延为2:1,当DDR3频率较高时,默认4:1。

VCCAUX_IO:FPGA高性能BANK的供电电压,取决于MIG控制器的频率。

Memory Type:默认选Components,表示用的直接是内存颗粒,

Memory Part:DDR3芯片型号,一般来说只要芯片容量和接口位宽一致都是兼容的,也可以点击下面的按钮自己创建一个Part

Memory Voltage:DDR3电压,默认就行

Data Width:数据位宽

续图:

ECC:ECC校验使能,72bit位宽才能使用。是一种用于检测和纠正存储器中数据错误的技术。在 DDR(Double Data Rate,双倍数据速率)中,ECC 校验通常用于对内存中的数据进行检测和修复。

Data Mask:数据掩码功能,数据管脚屏蔽使能,没用过。。。

Number of Bank Machines:Bank Machines的数量用来对具体的每个或某几个bank单独控制的,选择多了控制效率会高,占用资源也会多。(不理解这句话,默认即可)

ORDERING:决定MIG控制器是否可以对它收到的指令进行重新排序,normal则是允许。

5、第五页

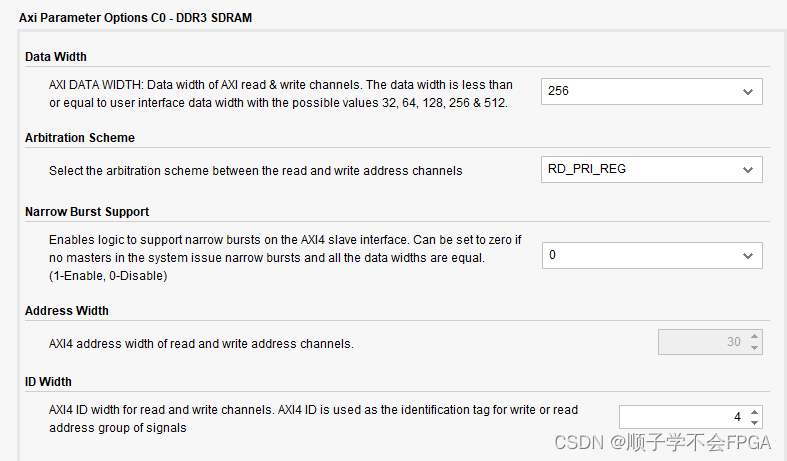

Data Width:AXI接口数据位宽,DDR3接口位宽是32,用户时钟是DDR3时钟1/4,再加上双沿采样缘故,所以最大是32 * 8 = 256,当然可以选择更小。

6、第六页

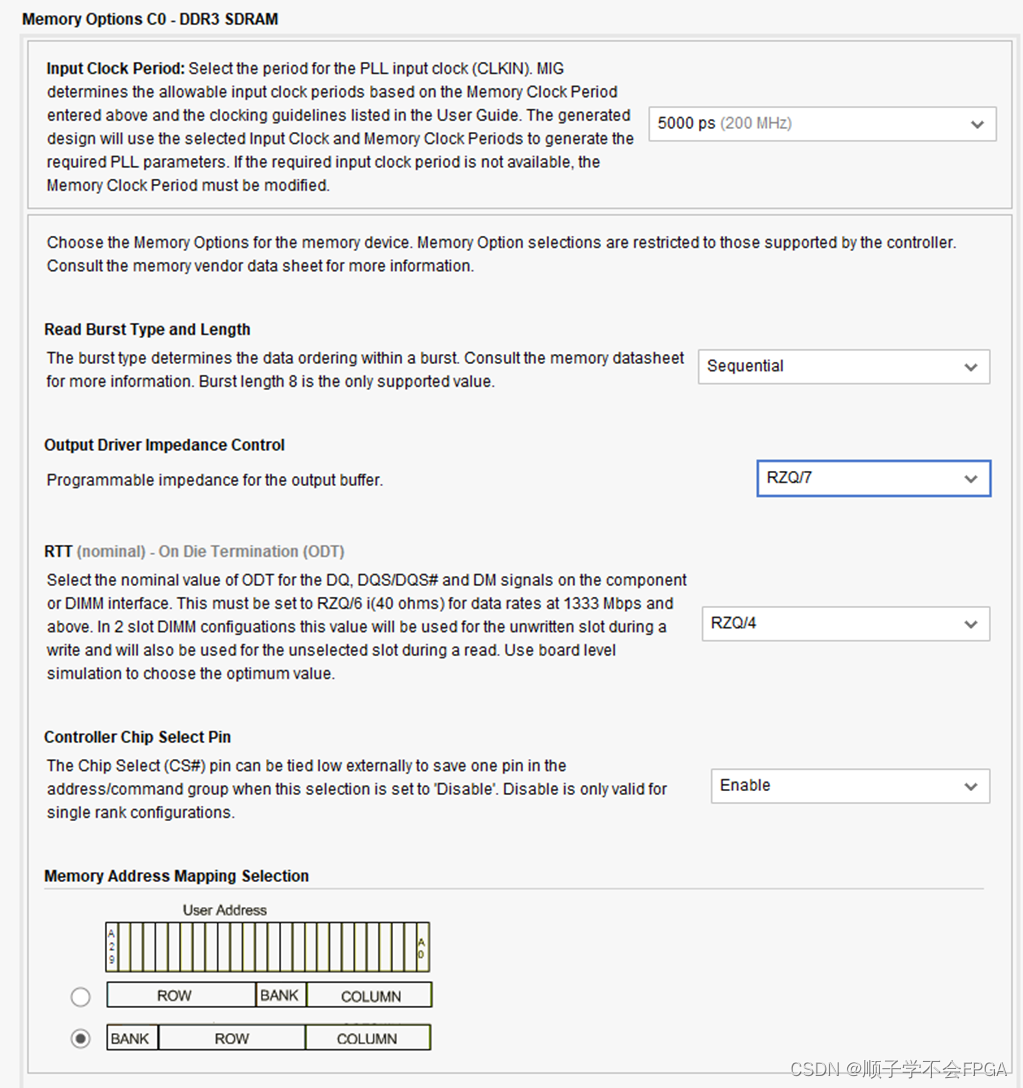

Input Clock Period:MIG IP核的系统输入时钟周期,该时钟是FPGA内部产生提供给MIG的,一般都是200Mhz,因为参考时钟要求是200Mhz,刚好一起用了

突发类型:顺序突发

输出阻抗:默认,这里RZQ表示240ohms,RZQ/4就是60ohms

终结电阻:默认

寻址方式:先bank地址,然后行地址,然后列地址

7、第七页

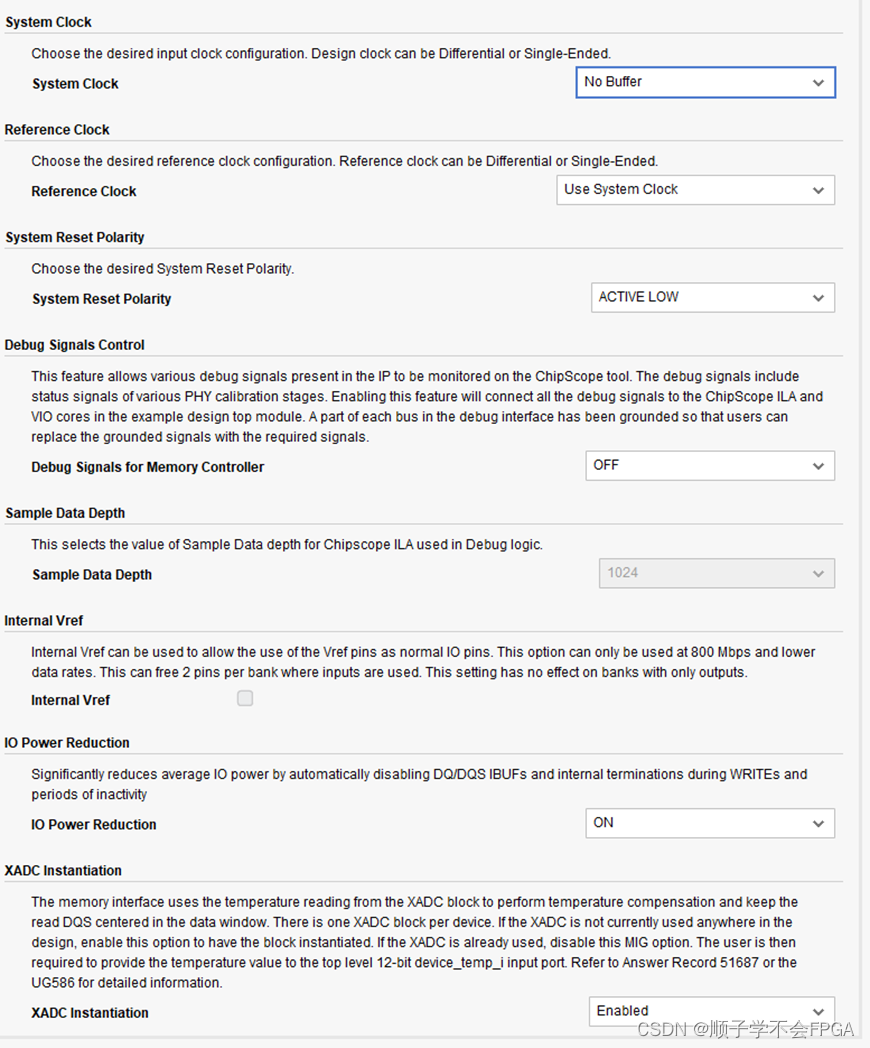

System Clock:MIG IP核输入时钟,由FPGA提供,这里选择no buffer,因为在FPGA内部逻辑里,将接入的晶振差分时钟通过MMCM转为了单端时钟信号然后给MIG,MMCM自带buffer,所以无需buffer,当然也可以直接选择差分时钟,将差分时钟线直接接到MIG。

Reference Clock:参考时钟,该时钟要求输入200Mhz,我们起面将系统时钟System Clock选为了200Mhz,刚好直接用即可。

系统复位电平:选择默认低电平有效

Debug single control:控制MIG是否将一些调试信号引出,它会自动添加ILA,这里就先不需要了

剩下的不知道,之简单看看这个介绍吧。。

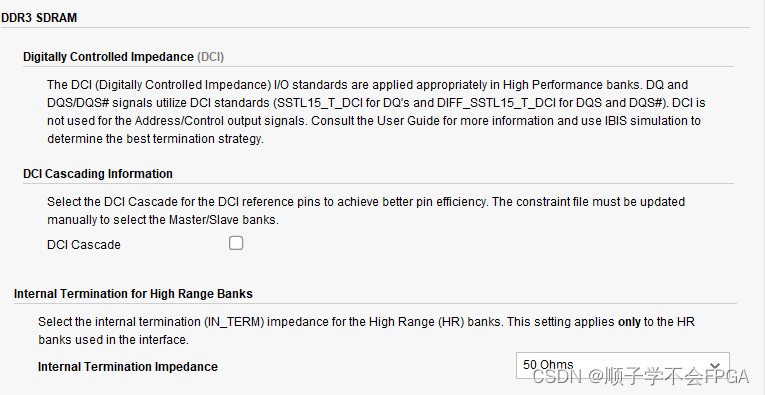

8、第八页

全是默认,都看不懂。。。

DCI:估计是什么动态调整管脚阻抗的

9、第九页

这页就是分配引脚,第一种是通过bank进行分配,第二种是手动配置或者直接引入已有xdc文件

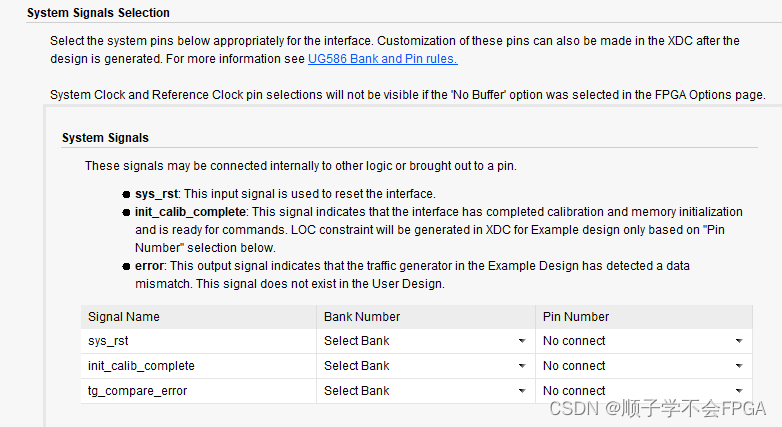

10、第十页

如果要将这三信号引出到管脚上就自己选一下就行,一般提供给FPGA内部逻辑使用,所以不连接就行。

sys_rst:高电平有效的复位信号

init_calib_complete:表示DDR3初始化完成信号,高电平有效

tg_compare_error:数据出错指示信号

剩下的一路NEXT。

二、MIG仿真

仿真时使用example design的仿真文件,然后自己写一个AXI读写模块即可。

不会AXI的小伙伴移步:https://blog.csdn.net/m0_56222647/article/details/136459976

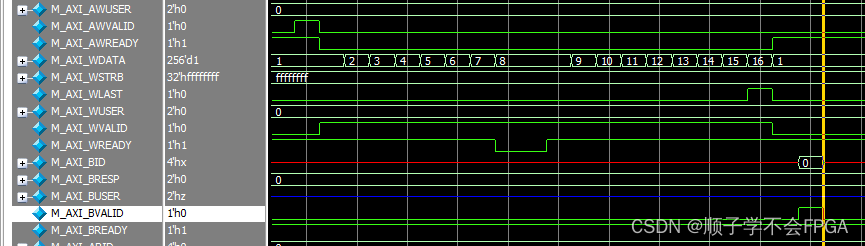

写数据:

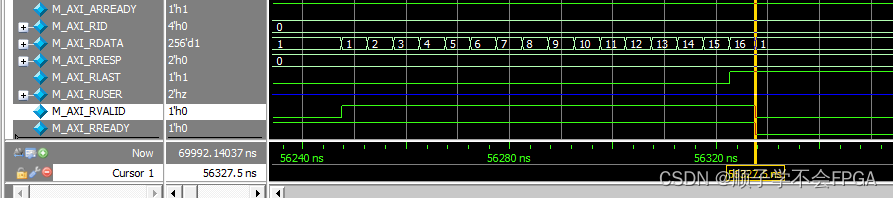

读数据:

4281

4281

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?