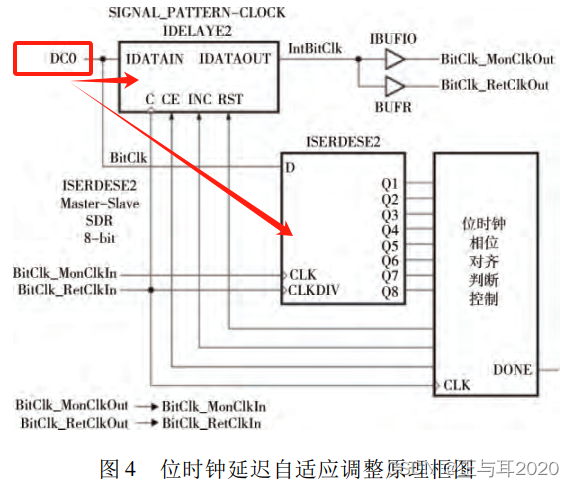

背景:在AD9653应用中,学习了《一种基于片同步技术的高速ADC与FPGA互连方法_韩琦》文章里面关于DCO自动移位模块,目前是实现动态调整DCO相位,保证采集DAT的正中间。本来在V7板子上,通过idelaye2+iserdese2组合实现了DCO自动移位功能,但是公司用了KU+的FPGA,没有idelaye2,而是idelay3,此时发现idelaye3+iserdese3组合不能延时时钟,原因IDELAYE3无法直接布线到全局时钟缓存,见手册《UG472》和《DS183》,很多资料也写了idelaye3不能延时时钟

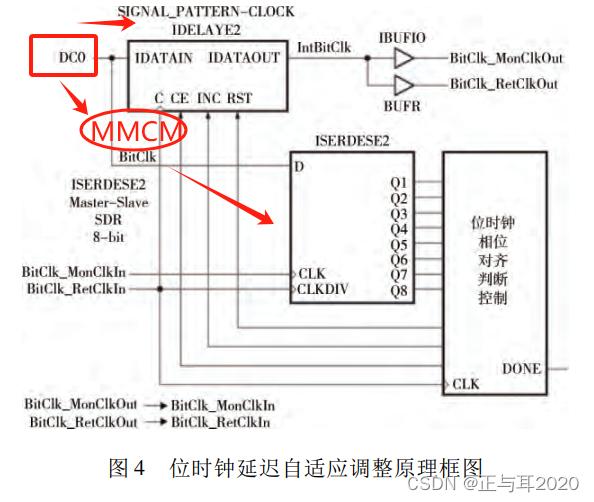

DCO自动移位模块:idelaye2+iserdese2组合如图

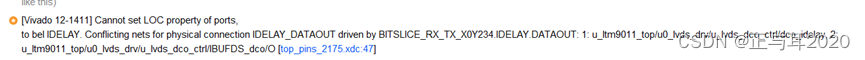

遇到问题1--布线失败:升级到idelaye3+iserdese3组合,VIVADO报错:布线冲突

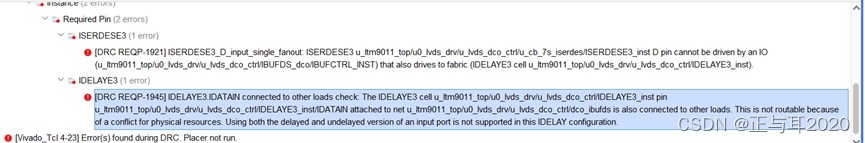

打开原理图:

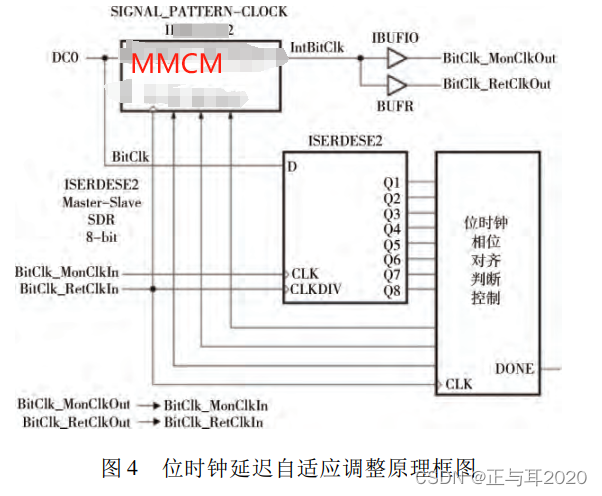

解释:综合阶段,DCO可以一分为二,给idelaye3和iserdese3,但是实现阶段,布线失败了,于是,我想到了加MMCM,方案就是这样的:

这种方案,布线通过了,仿真也没有问题,但是实际上板子调试时,发现idelaye3并没有生效,不管idelaye3怎么移,iserdese3输出一直是FF。。。。。。

解决:放弃idelaye3,不用idelaye3移时钟,最终选择了MMCM替代idelaye3,方案如图

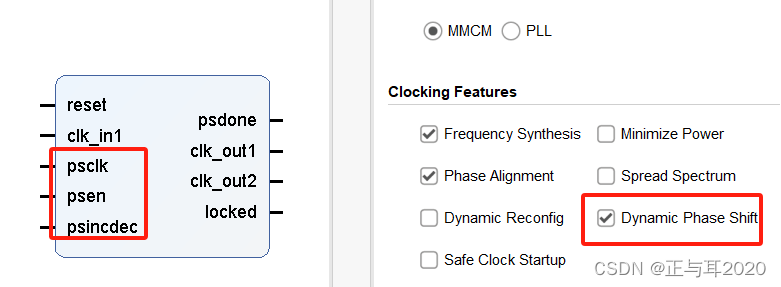

原因:MMCM自带了PS接口,可以对时钟相位进行精准调节

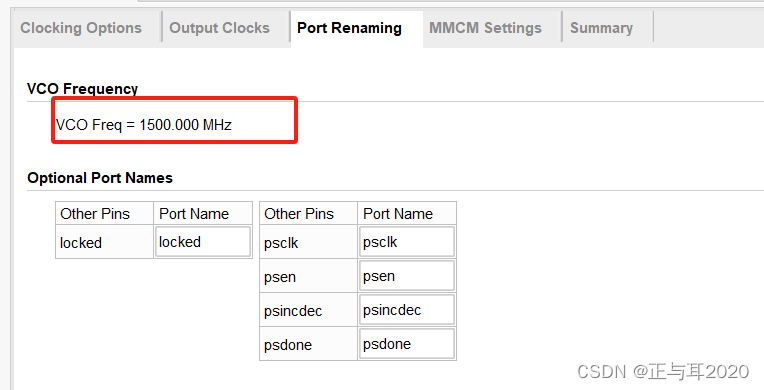

核心:psen&psdone每拉高一次,相位移动VCO/56ns. VCO是MMCM的VCO,可以自定义也可以用默认值,如图

本文讲述了在AD9653应用中,作者面临idelaye3+iserdese3组合无法有效调整DCO相位的问题,转向使用MMCM作为替代方案,因为MMCM具有PS接口能精确调节时钟相位。最终,作者发现MMCM的PS功能解决了实际应用中的时钟移位问题。

本文讲述了在AD9653应用中,作者面临idelaye3+iserdese3组合无法有效调整DCO相位的问题,转向使用MMCM作为替代方案,因为MMCM具有PS接口能精确调节时钟相位。最终,作者发现MMCM的PS功能解决了实际应用中的时钟移位问题。

7306

7306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?