IP核(IP Core)

ISE中有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

1. 打开ISE软件,新建工程:

File -> New project,然后填入工程名及工程路径

2. 工程设置,根据FPGA板子设置

3. 加入设计文件,在Design一栏中的Hierarchy中右键,选择New source->Verilog Module,填入文件名;此处也可通过Add source添加verilog设计模块。

4. 添加ip核,如上,选择New source->IP(CORE……),填入IP核文件名,然后根据功能或者名称选择相应的IP核,接着会跳到IP核参数设置界面,根据相应的功能进行选择和设置IP核。此处以添加PLL分频为例:

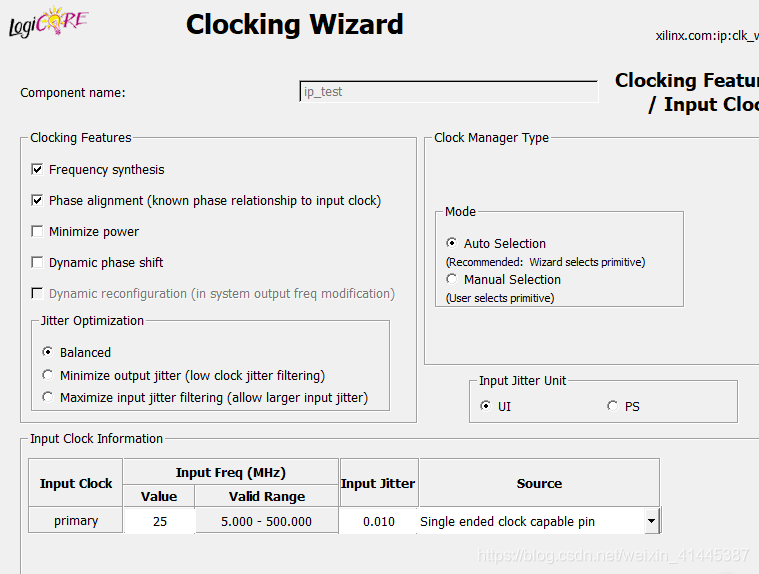

在IP核中选择:clocking wizard

然后进行配置

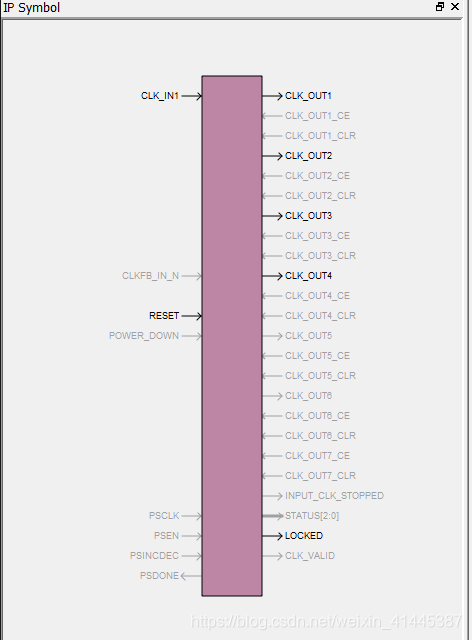

配置的时候可以看到自己配置的引脚及功能:芯片框图如上图:

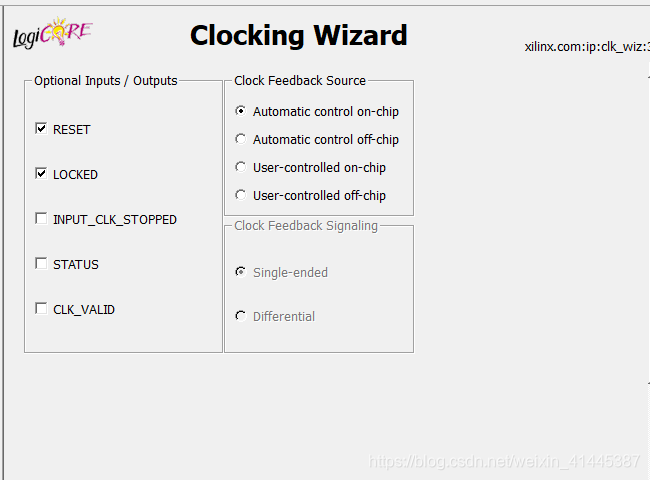

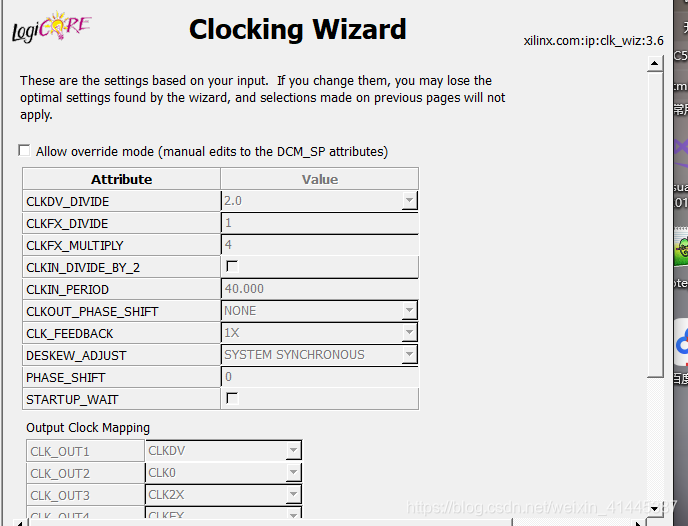

对芯片进行具体配置

引脚功能配置:

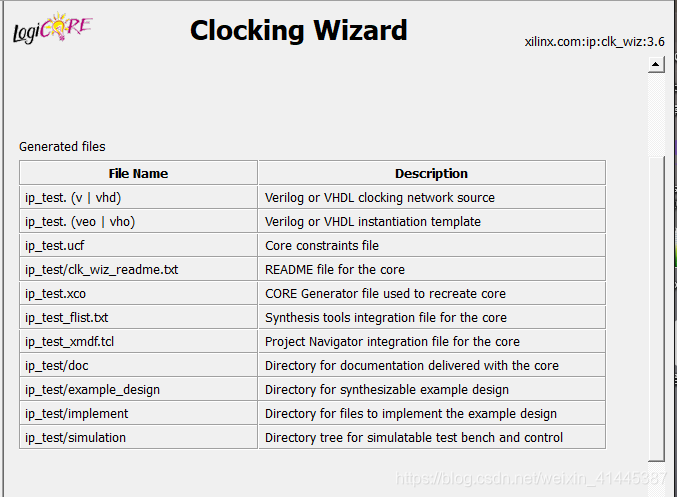

具体文件的描述:

实例化:

打开.veo文件,将实例化模板进行复制,进行配置引脚即可。

7159

7159

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?