Test pattern management 测试向量管理

生成最佳的pattern

#使用

create_patterns

#时会默认将所有的fault 类型加入到consider中;执行大量的设计分析和DRC;

#创建所有必要的pattern 类型

#监控pattern的生成(包括实时的coverage pattern count 以及执行时间等) 如果必要会修改参数

#如果必要 自动运行top_up的方式

##使用

report_patterns

#报告当前生成pattern的信息; 你可以展示所有pattern的信息 或者使用

-pattern_index

#选择单个的pattern去报告

#如果你使用

set_pattern_filtering

#创建了一个临时的subset

#那么此时report的pattern只是集合中的pattern;

##使用

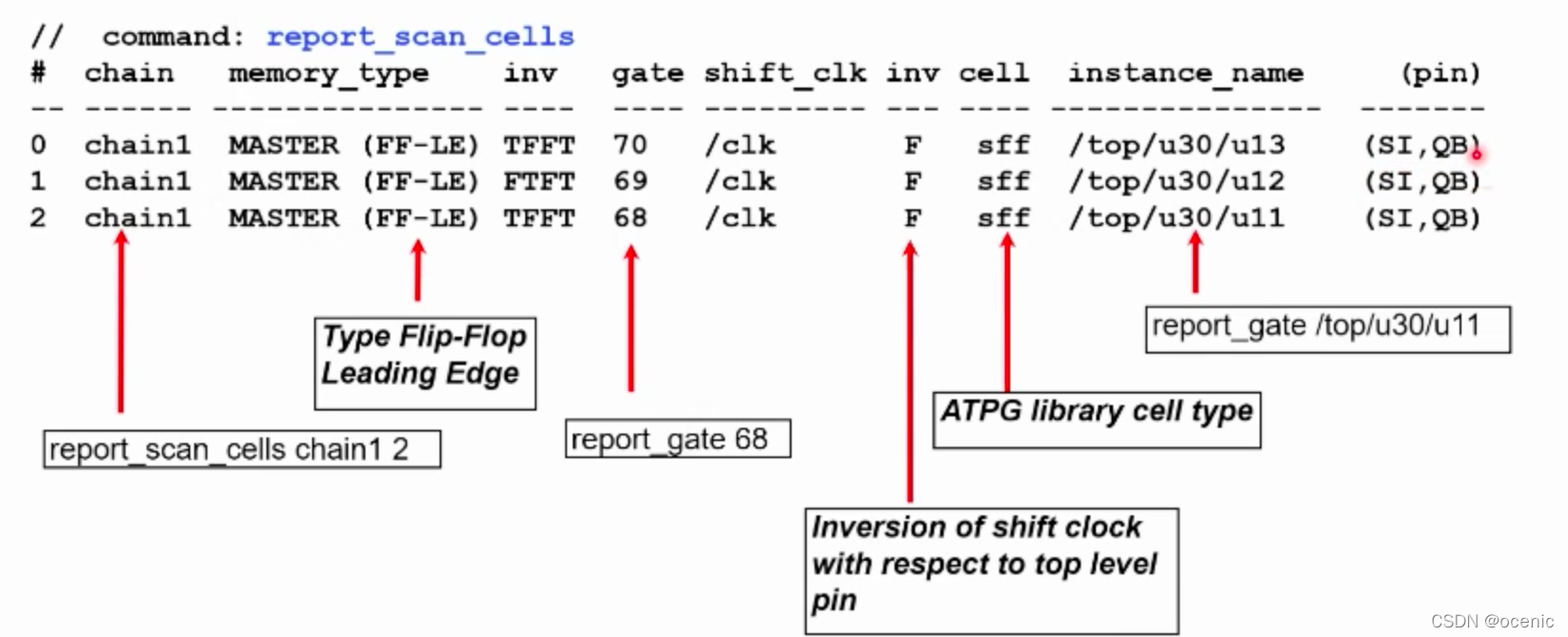

report_scan_cells

#去查看设计中scan_cell的信息

report_scan_cell中的memory_type分类

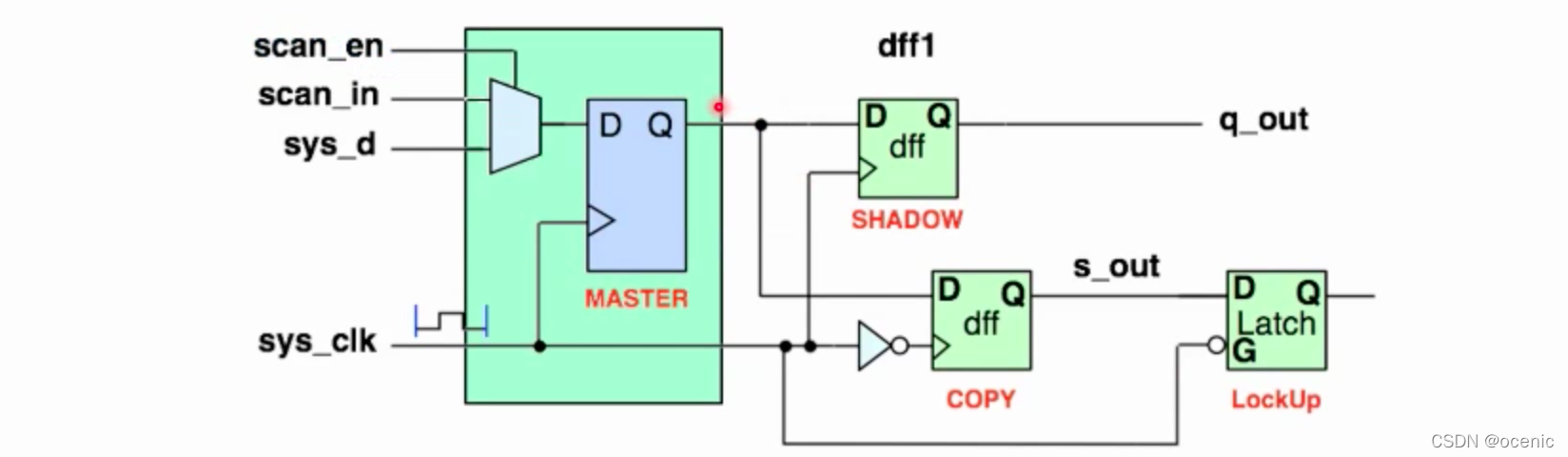

memory_type 是指memory element的分类包括: MASTER;SHADOW;COPY:LOCKUP;如图所示:

MASTER: 是指scan chain上的 用户hold shift过来的value的memory element;

SHADOW: (直接接在MASTER cell 后边 中间没有逻辑 COPY cell也一样)是指那些跟随 MASTER cell变化而变化的memory element;并且 SHADOW的输出并不是scan path 的一部分;

COPY: 和SHADOW一样是继承上一级MASTER的值(copy上一级的值)但是其输出为scan path的一部分;

LOCKUP:是指那些为了预防"shoot through(击穿??)"保持半个周期值memory element;一般是latch; 其输出也是scan path 的part(比如两个clock domain,中间有latency的问题 影响hold time 可能会插这种cell)

database的pattern进行reuse 和debugging

工具可以将pattern数据保存为不同的格式 主要分三大类: database; verilog; WGL STil ; 其中 database的又分为 Asicii,binary ,PATDB;三种都是可以会读到工具中去做reuse 和debugging; verilog格式的pattern 是去做 Time-based verification的;Wgl 和STil是左后要放在ATE上做测试和分析的;

当然你可以指定将文件直接压缩为.gz或者.z;

pattern文件可以回读(read_back)到Tessent工具中, 方便我们去生成Top-off 的pattern;去debugging仿真的mismatching;去做其他格式的转换;去做tessent的诊断等;

我们也经常将flat model一同保存下来;

write_flat_model <filename>

#利于配合前面的pattern 做回读;

Ascii 是默认的pattern格式,有着完整的可读性和可运行指令性;包含测试的coverage的统计,test procedures 包括timeplate;每个pattern shift的pattern data(激励); 每个pattern的预期结果;以及scan memory elements;

Binary 和ASCII 包含的信息一样 但是以一种压缩的格式 对于非常大的设计采用;

PATDB, 建议用在 core-level的pattern上用于 hierarchical ATPG的时候 将pattern 重定向到top-level;

#使用

read_patterns <pattern_filename>

#来回读pattern

#如果要做 top-off 的pattern

#需要使用

simulate_patterns -store_patterns all

#将数据库中的pattern转化成工具的internal format

基于时序的验证:testbench 的创建;

pattern 其实还分 chain test pattern和scan test pattern??

scan chain还要分两半 就离谱??

pattern 也分 parallel 和 serial ;

Time-based verification ;

AT-speed patterns & On-Chip clock controllers(OCC)

了解 如何生成at_speed 的pattern;二就是在ATPG阶段使用内部OCC的选项去定义内部时钟的控制;

review

at-speed fault主要包括: Transition 和 path delay 两种;

Transition的fault location在 每个instance 的pin /port上;而path delay 考虑的是整条path的 slow-to-rise/fall的累积;

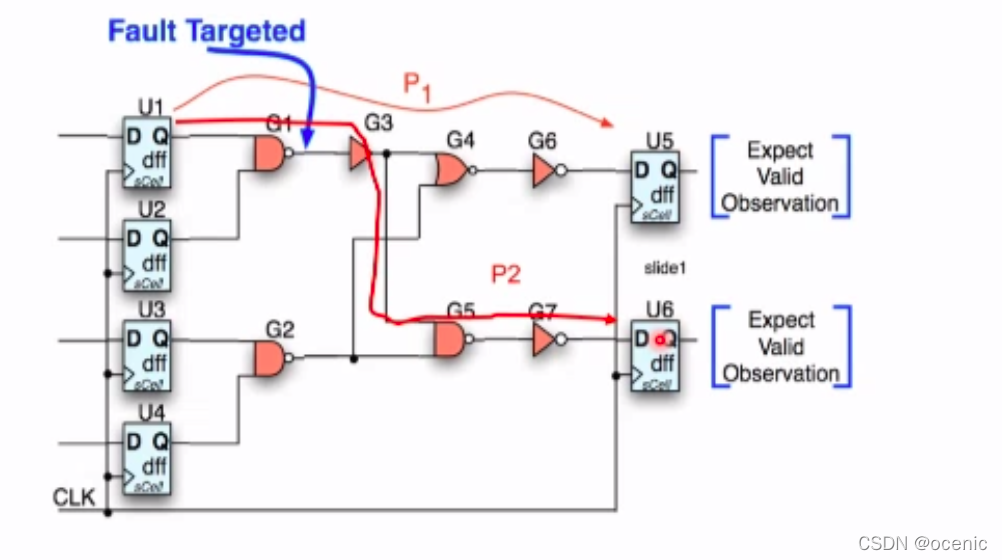

transition fault的观测

默认 工具会为每一个可能的观测点 设置一个期望值;作为fanout tree一部分的所有scan cell都会被附上期望值 capture的时候用;path的选择是随机的,但是如果存在不可预测的长的路径 可能就会在造成pattern验证时的mismatch 或者在ATE上的失败;

可以通过设计false path的方式 去限制工具可用的观测点;

#指定false path的方式有两种:

#1. 在SDC中添加约束

set_false_paths -from -to -through

#2. 直接在ATPG工具中

add_false_path

# 例如要将 途中的P2定义为false path ,可以将U6 mask掉然后U5声明一个期望值;

multicycle path

信号的传播延迟多于一个时钟周期的path;时钟周期可以被定义为 launch clock 以及capture clock; multicycle path的定义一般在 SDC中;

对于 multicycle path 上fault的detect ,是基于SDC中定义的时钟周期数的;(在PT输出SDC文件时 需要加上 transform_exception before write_sdc)

path delay fault

path delay的fault是针对 静态时序分析出来的 critical path 来说的, 是A到B上element 的transition 的累积,会有指定的launch 和 observation点;

会有path definition files(为ASCII文件); 将path load 进去; 然后工具会看path 是否可以走通;

set_fault_type path_delay -mask_noobservation_points

read_fault_sites paths_file.txt

at_speed pattern的生成

at_speed 的pattern需要去产生一个transition (1->0/0->1 的transition) 使用的方法:

broadside/launch-off-capture method或者 launch-off-shift method

默认优先产生boardside pattern; 当没有解决方案时,才会长生launch-off-shift的pattern;(当然用户可以指定工具产生何种类型的pattern)

两种方法都需要CCD(clock control definition)去配置 at-speed pattern的 launch 和capture;

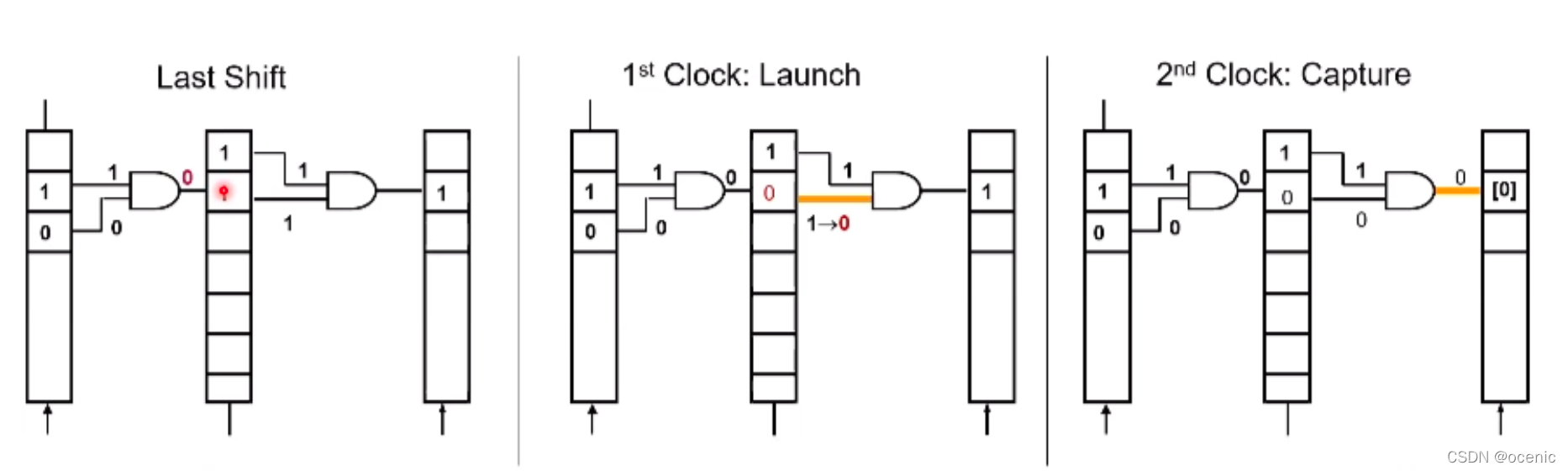

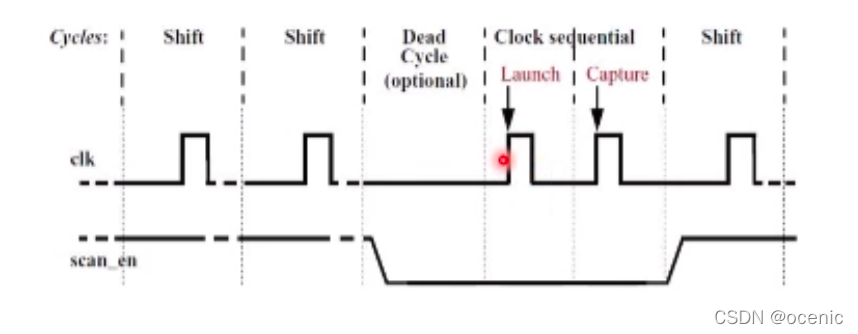

Broadside

clock sequential pattern

-

在最后一次shift之后,当clock pulse来临,transition随即发生;第一个时钟沿 launch the transition;第二个时钟沿 capture;

-

在capture 阶段(clock sequential cycle)是由两个快速的时钟沿在的,如图是检测点是否有slow to fall的fault ; 如果存在fault, 快速时钟沿检测的是原来的1 而不是更新后的0;

-

可选择性的加入 Dead cycle 等待足够长的时间 scan_en 拉低

broadside 的好处就是: -

scan enable并不在时序路径里面

-

支持多级的non-scan luoji

-

memories pin上的时序的fault也是可以被测试的;

-

支持 false path和multicycle path的标记

缺点就是: 在pattern生成的时候会比较复杂;

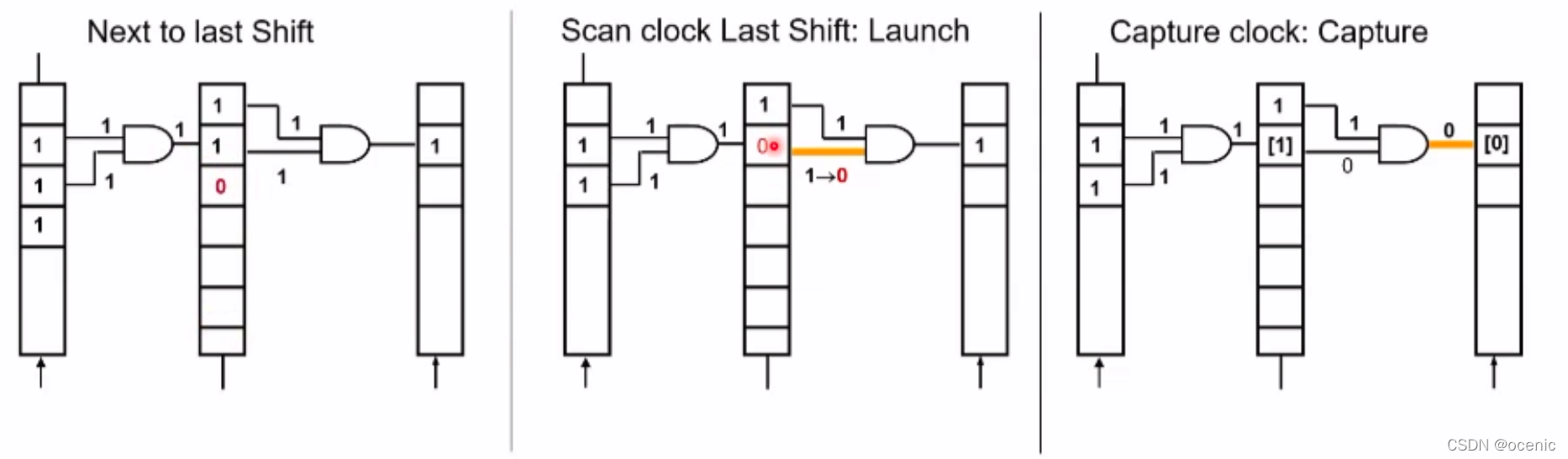

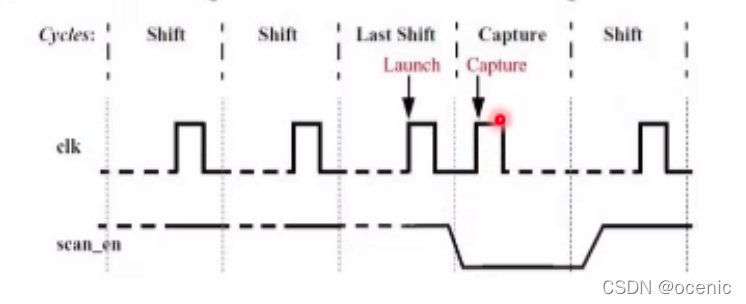

launch-off-shift

顾名思义,就是将transition的launch 作为最后一次shift;在capture 阶段直接capture transition;

所以broadside 和launch-off-shift 的区别就在于,broadside pattern transition的产生在capture阶段 也就是transition是上级电路运算来的,而launch-off-side pattern中transition是直接shift进去的;

缺点就是: scan_en 无法快速切换到0 时序要求太高(要对scan enable 的布线和时序上的平衡 使它的transition time 能够满足条件)

缺点就是: scan_en 无法快速切换到0 时序要求太高(要对scan enable 的布线和时序上的平衡 使它的transition time 能够满足条件)

优点就是 生成pattern会更容易一些,能够跨 false path 进行测试;

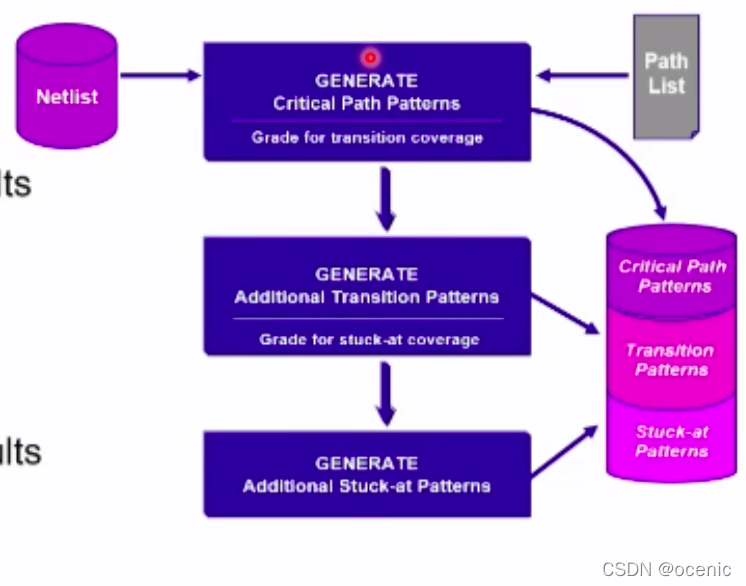

创建单个 test_pattern 文件

这里的单个应该是一类 fault’的pattern吧??

在生成单个fault 类型的pattern时(transition.pathdelay,stuckat),pattern之间可能会重合,所以需要做pattern的合并;

通过fault grade 的方式,先将上次的pattern读入, 做fault grade 看里面是否已有覆盖到的pattern 然后再TOP-up 相对应的pattern;

一般会先测stuck@的fault 再测transition;(先将覆盖率高的 stuck@ pattern生成出来 下面at_speed fault 被覆盖的数量也会增加)

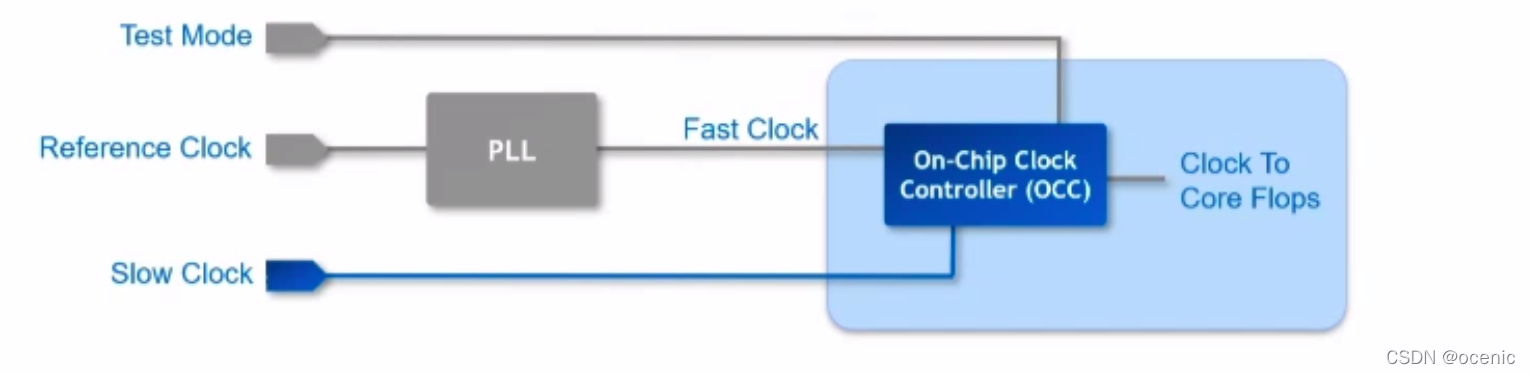

at-speed test:生成快速时钟

at_speed 测试需要工具在慢时钟(shift阶段)和快时钟(capture阶段)进行切换(对于broadside 的方式);默认 片上的PLL 会被用来生成快时钟;但是用MUX 做门控不足以提供对两个时钟的充足的控制,MUX只能在scan clock 和 fast clock之间做switch 但是不能控制 fast clock生成的脉冲数;

为了控制fast clock 我们加入了OCC (on-chip clock control)模块,他的作用如下:

- 为每个clock domain提供独立的控制

- 根据pattern的情况 为 capture cycle分发正确数量的脉冲

- 更加干净的在shift clock和fast clock之间进行切换;

- 根据测试的类型,判断capture阶段是使用slow clock还是 fast clock;

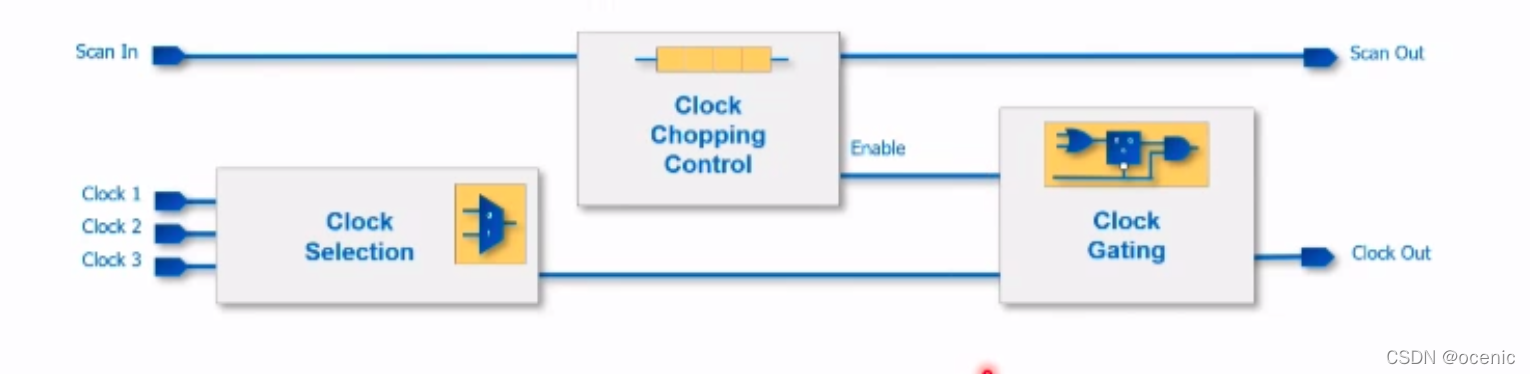

OCC 功能结构

重点看 clock chopping control; 里面应该是有 scan-programmable shift register 通过控制clock gate 控制pulse的数量;这里的 scan-programmable shift register 就是scan chain结构,以sub-chain的方式串到scan-chain上 通过shift 出来的布尔变量控制clock chain;

在ATPG中定义OCC

方式1:(建议的)

CCD(clock control definition)

用户定义ATPG能怎样控制时钟;(具体ATPG如何控制 产生多少个pulse 是由ATPG工具在推pattern的时候决定的)

并不会定义特定的时序;所以并不能配置复杂的clock schemes;

对每一个内部时钟做单独的definition;工具会自动决定在capture cycle 使用哪个clock,去detect更多的faults;

DRC的时候会验证 test procedure文件中时钟第一的语法;

方式2:(历史上曾用)

NCP(named capture procedure)

用户指定外部信号和内部生成时钟的关系, 好处是用户可以控制capture cycle全部的失踪时序;

前提是你得先写好procedure;

CCD

两种定义:

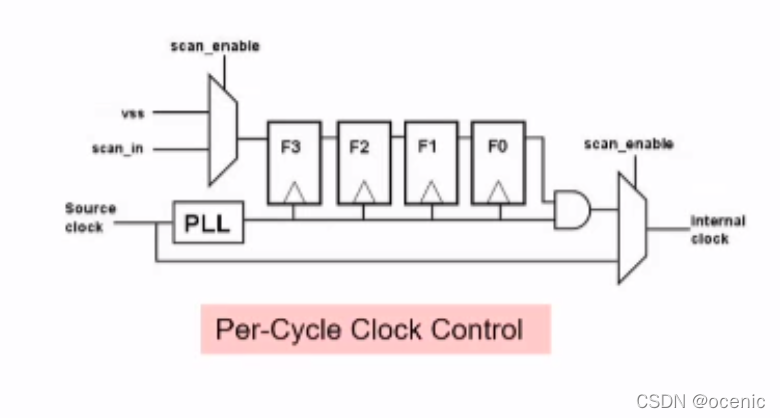

per-cycle clock control (最常用的)

允许你使用scan cell的值基于单个的capture cycle 去定义内部时钟的输出;

使用 基于流水线的时钟生成,每个cycle 使用一bit(scan cell里的值 sub-chain里面的值)去控制时钟;

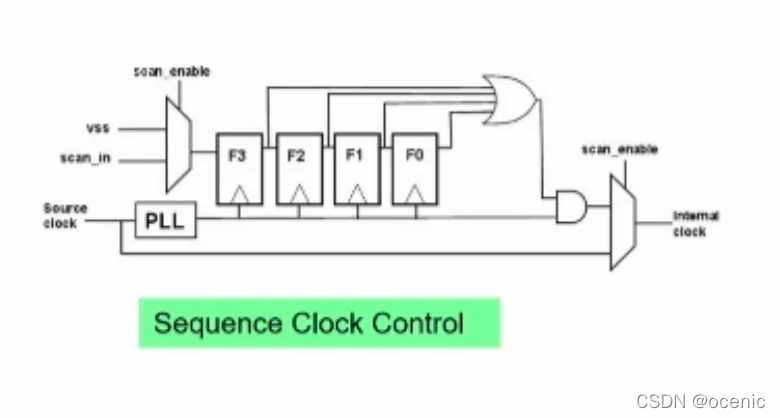

sequence clock control

使用 scan_cell里的值 基于capture cycle的时序去定义内部时钟; 使用基于计数器的时钟生成电路;不能被用来生成 launch-off-shift’的pattern;

(两个比较着来看 就可以可以很容易的理解 pre-cycle使用sub-chain 直接去存储pulse; 而sequence clock control 使用sub-chain去控制pulse的出现时间)

Example: pre-cycle clock control

ATPG_cycle

需要在 procedure文件中定义 ATPG_cycle 定义内部时钟在特定的capture cycle 如何做pulse;

CLOCK_CONTROL /clk_ctrl/int_clk1 =

SOURCE_CLOCK ref_clk;

ATPG_CYCLE 0 =

CONDITION /clk_ctrl/F0/q 1;

END; #分别定义的是 sub-chain中的每个scan cell的值;

ATPG_CYCLE 1 =

CONDITION /clk_ctrl/F1/q 1;

END;

ATPG_CYCLE 2 =

CONDITION /clk_ctrl/F2/q 1;

END;

ATPG_CYCLE 3 =

CONDITION /clk_ctrl/F3/q 1;

END;

Example: Sequence clock control

ATPG_sequence

与pre-cycle 的clock control 不同, 这里需要定义的是atpg_sequence;

#实现和上例相同的4个脉冲

CLOCK_CONTROL /clk_ctrl/int_clk1 =

SOURCE_CLOCK ref_clk;

ATPG_SEQUENCE 0 0 = #两个value 指定开始的cycle 和结束的cycle; 如果不指定的会在每个capture cycle 都会pulse clock;

CONDITION /clk_ctrl/F0/q 1;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

END;

ATPG_SEQUENCE 0 1 =

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 1;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

END;

ATPG_SEQUENCE 0 2 =

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 1;

CONDITION /clk_ctrl/F0/q 0;

END;

ATPG_SEQUENCE 0 3 =

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 0;

CONDITION /clk_ctrl/F0/q 1;

END;

#不完整的表述会告诉工具 未指定的状态将会关闭CLOCK;

在ATPG中使用CCD

整个flow可以分以下几步:

1. 将 clock control的definition 写入你的test procedure文件中

2. 启动Tessent shell pattern产生的设置

3. 退出 setup mode 然后运行DRC

check_design_rules

- 改正DRC上的违例;

- 验证 clock control的配置

report_clock_controls

6.开始生成pattern

7. 保存生成的pattern

write_procedure_testbench

创建一个 verilog的testbench 去验证你的 procedure文件中定义的internal signal与你预期的是否一致;

write_procedure_testbench <test_bench_filename> [-replace] \

[-all | -capture capture_name | -load_unload]

这个步骤 写完procedure 之后就可以执行,

NCP (Named Capture Procedure)

同样是描述OCC的一种方式; 与CCD 平行的概念

除了用于ATPG的OCC之外 还可以用于其他的on-chip 或者internal 的clock;

他与上面的描述方式有所不同:

使用复杂的时钟的schemes定义详细的时钟周期;需要详细的描述每个周期发生的events;

允许用户指定确切的launch capture的时序 包括multiple load patterns中的load points;所以塔索覆盖的pattern类型会更全 包括stuck@ ;path delay ;broadside transitionpatterns; 不能用于 launch-off-shift pattern的生成

为什么叫NCP? 一般我们在Procedure定义的时候 后边直接跟一个capture就好了, 而NCP 有自己独一无二的capture name ;

example : NCP

如生成一个iclk1 0011 的capture cycle;

首先要定义 external signal 和internal signal 之间的关系

#定义 timeplate

timeplate tp_ext_cap = #外部

force_pi 0;

measure_po 10;

pulse refclk 20 10;

period 40;

end;

timeplate tp_int_cap = #内部

force_pi 0;

measure_po 10;

pulse iclk1 20 10;

pulse iclk2 20 10;

period 40;

end;

## 定义procedure

procedure capture clk_2pulse =

#配置 sub-chain的值

condition /condition0/Q 1;

condition /condition1/Q 1;

condition /condition2/Q 0;

condition /condition3/Q 0;

mode external = #外部refclk 的event

cycle =

force_pi;

force testclk 0;

force refclk 0;

force ScanEn 0;

pulse refclk ;

end;

cycle =

pulse refclk;

end;

cycle =

pulse refclk;

end;

cycle =

measure_po;

pulse refclk;

end;

end;

#内部的clk1 clk2的event

mode internal =

timeplate tp_int_cap;

cycle slow =

force_pi;

force testclk 0;

force iclk1 0;

force iclk2 0;

force refclk 0;

force ScanEn 0;

end;

cycle =

force iclk1 0;

end;

cycle =

pulse iclk1;

end

cycle =

measure_po;

pulse iclk1;

end

NCP 的一些规则

- internal mode和external mode 所用的cycle 的数量 以及他们的timeplate大多数情况下都是不同的 但是他的总的时钟周期需要一致;

- 对于那些non-clock的event 他们,嗯发生的顺序在总的周期中应该是相同的;

- measure PO只能出现在最后一个cycle;

- Force PI 也必须出现在第一个cycle 而且要在 pulse 第一个clock之前发生;

- 在external mode下 是不能控制任何internal的signal 的;但是internal mode可以

使用ATPG引擎其定义NCP

使用ATPG 帮助我们写NCP 可以先使用CCD的方式;

- 创建一个所有时钟的时序图 方便你理解时钟之间的关系

- 设置ATPG工具 为transition pattern的生成

- 设置时钟约束,

set_clock_restrictions - 生成pattern

- 使用create_capture_procedure 创建 NCPs的timeplate(工具自己写的NCP timeplate)

- 使用 write_procfile 保存procedure 文件

pattern verification

会将 OCC 的结构先排除出去,

557

557

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?