做DFT的配置,这里的配置主要就是系的设计里面需要做什么,怎么做;然后tessent会根据文件或者string之中的信息 创建一系列的instruments 并将他们插入到设计中;

当然 specification 有特定的格式:

DFTSpecification(module_name,id){#module的名字与current的design 相匹配 /Id是为了在process_dft_specification的时候 加入ID选项对specification进行选择

rtl_extension : string; //default: v #当要输出verilogRTL格式的创建的那些个instrument的描述时 可以指定这个选线;

gate_extension : string; //default: vg #当输出文件中包含门级的verilog 模型时,这个选项 在 no_rtl的context下会使用;

reuse_modules_when_possible : on | off | auto ; # 是否尽可能重用instrument module,或者对于每一个实例来说创建不同的module; 设置为了auto 的时候, 会根据context的情况而变化 当在rtl context 为On 当在no_rtl context 为off;这里的重用,也并非物理上的重用,当我们向网表中插入instrument 的时候,会习惯性的避免出现重复的实例,也是时序优化需要uniquified

use_rtl_cells : on | off | auto ;#控制器需要实例化一个instrument的时候 是使用RTL 还是 门级网表,例如一个控制器需要一个时钟倍频器,工具并不会用RTL写一个出来而是直接实例化一个,当选项为ON时,工具会创建为指定的RTL cell,并将这个cell实例化到项目中,你可以控制cell 的ports的名字 ,之后你可以使用replace_instances命令替换RTL cell为a real cell;当选项为off时就是选择cell library中的单元并实例化到设计中 ;现在在任何context下都不建议使用 rtl cell,他会在综合时存在 设计模型边界保护上的缺陷;

use_synchronizer_cell_with_reset : on | off ; //default: on *DefSpec #是否使用带复位的时序单元;

use_rtl_synchronizer_cell : on | off | auto ; //default: auto *DefSpec #强制工具创建实例化 RTL的同步单元;即使use_rtl_cell被设置为off 或者context为-no_rtl的时候,有啥好处不知道哎;

dft_cell_selection_name : string ; #只有以下几种情况需要指定这个属性: RTL cell没有被使用;你的 cell library 存在多于一个 的dft_cell_selection wrapper; 你没有使用 set_cell_library_options -default_dft_cell_selection_name 指定默认的dft_cell_selection wrapper;

persistent_clock_cell_prefix : string ; //default: tessent_persistent_cell_ persistent_cell_prefix : string ; //default: tessent_persistent_cell_

add_persistent_buffers_in_scan_resource_instruments : on | off ; //default: on *DefSpec

force_creation_of_rtl_cells : cell_type, ... ;

// legal : And2 Or2 Buf

// Inv Mux2 ClkAnd2

// ClkOr2 ClkBuf ClkInv

// ClkMux2 ClkGateAnd

// ClkGateOr PosedgeDff

// PosedgeDffReset

// PosedgeDffSet

// NegedgeDff

// NegedgeDffReset

// NegedgeDffSet

// PosedgeSynchronizerReset

// PosedgeSynchronizer

RtlCells { }

BoundaryScan { }

EDT { }

EmbeddedBoundaryScan { }

IjtagNetwork { }

InSystemTest { }

LogicBist { }

LpctType3 { }

MemoryBisr { }

MemoryBist { }

OCC { }

}

上面的文件是加载tessent DFTspecification文件读入的; 需要通过create_dft_specification;才能将配置信息存入变量中,方便之后进行修改和配置;

create_dft_specification,会找出当前设计中所有需要连接到 Ijtag网络上的Ijtag的实例,并自动创建Ijtag wrapper 去连接它们.如果 ICL文件被加载进来 ICL module与设计中的module 在 elaboration的时候已经做的了match,会被这么命令作为已经连接到网络上的部件自动排除出去,可以使用 report_ijtag_instance 或者 get_ijtag_instance 去查看 那些和ICL module陪陪的instance;

此命令也会创建必要的IJTAG网络去控制已经创建的MBIST 和 memory BISR以及 提供一个 boundary scan host port 到我们的Boundary scan中;

Ijtagnetwork 的specification 是如何创建的:

当你的set_design_level 指令将当前设计设置为 sub_block 或者 physical_block的时候, create_dft_specification 命令创建的IJTAG 接口为 client IJTAG interface 而 设置为 Chip 时 为client TAP interface;

在第一次包含IJTAG的这种dft insertion 的过程里, 工具会创建一个包含 两个SIB元件的 root level的IJTAG 环 这两个SIB分别叫做 SIB(sti)和 SIB(sri),当然 这是在没有 prior insertion pass 提前插入的前提下的; SIB(sti)是提供当前设计与 IJTAG网络的选通,这些器件将通过 logic testmode与其他功能逻辑一起进行scan test. 缩写sti 参考scan test instrument; SIB 提供 host port 到client之间的隔离

SIB(sri)

用于将 child physical blocks 逻辑测试的元件以及 用于配置逻辑测试模式的TDRs 接入到 IJTAG网络中; SRI的缩写于 Scan resource instrument (扫描用资源元件) 这些IJTAG 节点必须在 logictest mode下保持 active 且不被干扰,还要排除在 logic 扫描链之外.

ICL module 当它具有 keep_active_during_sca_test ICL模型属性为true时会被识别为 scan resource instrument 然后布局在SIB(sri)的下面,如果你想将一个instrument 像其他functional logic一样被scan test测试到 就必须将他的ICL module中keep_active_during_scan 设置为false;

在chip level上,在第一次的插入过程中会插入一个TAP controler 除非-exiting_ijta_host_scan_in 被指定了;

这个选项是在创建的DFTspecification中定义一个已经存在的host scan 接口,整个 ijtag 网络都依附于这个接口,

IJTAG wrapper

下面又包含4个wrapper:

分别是: dataoutport datainports implementationOption HostScanInterface

hostscaninterface

定义了一个扫描接口,在这个接口下 可以连续的 串行的访问下面的IJTAG 节点;

IJTAG的元件能够用来配置电路的多种 scan mode,使用TDR产生多种SCAN mode 的信号;在这个例子中,提供访问此TDR的网络部分必须在scan test期间保持活跃,且像其他test_setup 的硬件一样不会受扫描模式的影响;如果属性 keep_active_during_scan_test 被设置到一个ijtag节点上,那么从host到节点的路径将会被追踪,并且所有在这条路径上的其他节点也会被标记 keep_active的属性;

带这条属性的ICL moudle将会在 ICL extract 的时候产生并且merge到总的ICL文件中;你可以之后在scan insertion的时候,使用这些信息将这些modules声明为 no_scan cell ,强制他们保留在graybox中在graybox产生的时候;

当 TDR 的wrapper 为 scan_mode的时候, keep_active的属性默认就是打开的,所以 这会强制所有从 host 访问他的节点 拥有 keep_active的属性

SIB

是一个指定IJTAG中 SIB 的创建和插入的 wrapper;

SIB是 IJTAG中特殊的节点 其包含一个单比特的移位寄存器,当bit为0时 SIB会绕开client node直接连至 host ports 当bit为1时 则会将client node 作为 scan path的一部分和host port相连 ;

移位寄存器的值还将会在 TCK的下降沿 传至update_stage 当update_enable有效的时候, delay stage 则会将 select_en 延迟一个周期输出;

当 reuse_module_when_possible的书香设置为on 时 SIB 模块名称将硬编码为 design_name_design_id_tessent_sib_#,其中 # 是从 1 递增的整数。

如create_dft_specification 所描述的 ,在scan test期间需要保持活跃的器件放在一个SIB下 而像memory BIST controller这样 需要被scan测试的 放在另一个SIB中;

这个SIB 会被标记为 scan_tested_instrument_host, 通常称为 SIB(STI),当有此种属性时,SIB还会配备附加逻辑去保证 那些学要被scan test的IJTAG网络 完全由 scan 来测试,需要注意的是 SIB(STI)还会配备一个 mini-OCC 用来控制ATPG和logic bist 以确定扫描测试的 TCK domain 何时接收 clock pulse;

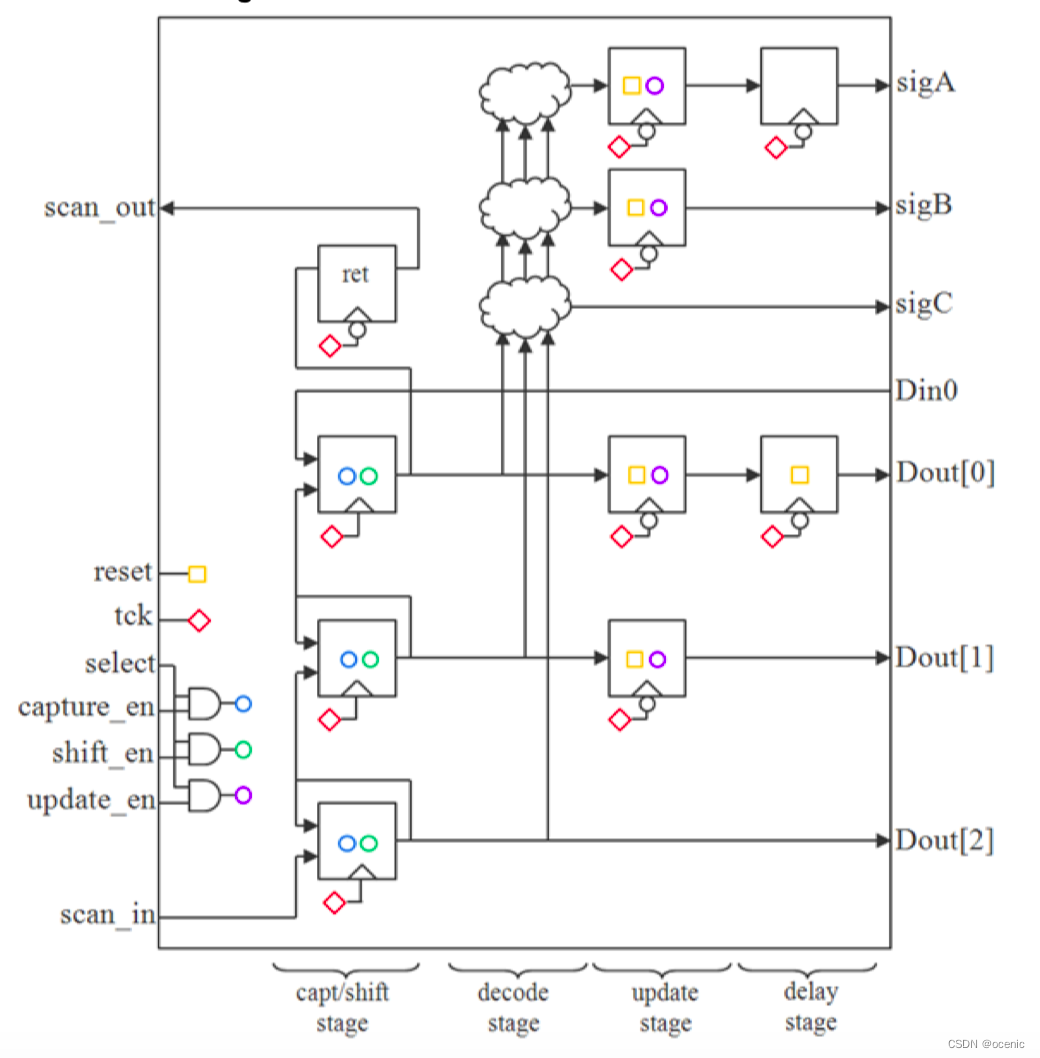

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-KIhu7lgW-1661908629623)(evernotecid://B004F96B-9AA0-47D6-BD23-E56FA9C545DF/appyinxiangcom/12890172/ENResource/p399)]](https://i-blog.csdnimg.cn/blog_migrate/b6192fbf5341287022922dbddb6db31a.png)

如上图所示例子: TOP 设置三个SIB 其中

TDR

先来看结构:

如图所示 为一个三bit的TDR,接口部分主要由 data_in data_out 以及译码后的信号;

parent_instance 就是例化 TDR module的parent instance;

501

501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?