此题需要注意的地方有三个:

1)水位监测器的输入是状态跳转的条件

2)assign {fr3,fr2,fr1} = {!s[1],!s[2],!s[3]};//不能根据输入判断否则会提前一会时钟

3)assign dfr = (state < next_state) ? 1’b0 : 1’b1; //使用组合逻辑电路结果结果不正确

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

parameter A = 3'b000,B = 3'b001,C = 3'b011,D = 3'b111;

reg [2:0] next_state;

wire [2:0] state;

//状态跳转

always@(posedge clk)

begin

if(reset)

state <= A;

else

state <= next_state;

end

//状态跳转条件

always@(*)

begin

case(state)

A:

begin

if(s == 3'b111)

next_state = D;

else if(s == 3'b011)

next_state = C;

else if(s == 3'b001)

next_state = B;

else if(s == 3'b000)

next_state = A;

else

next_state = A;

end

B:

begin

if(s == 3'b111)

next_state = D;

else if(s == 3'b011)

next_state = C;

else if(s == 3'b001)

next_state = B;

else if(s == 3'b000)

next_state = A;

else

next_state = B;

end

C:

begin

if(s == 3'b111)

next_state = D;

else if(s == 3'b011)

next_state = C;

else if(s == 3'b001)

next_state = B;

else if(s == 3'b000)

next_state = A;

else

next_state = C;

end

D:

begin

if(s == 3'b111)

next_state = D;

else if(s == 3'b011)

next_state = C;

else if(s == 3'b001)

next_state = B;

else if(s == 3'b000)

next_state = A;

else

next_state = D;

end

default : next_state = A;

endcase

end

//状态输出

always@(*)

begin

case(state)

A: {fr3,fr2,fr1} = 3'b111;

B: {fr3,fr2,fr1} = 3'b011;

C: {fr3,fr2,fr1} = 3'b001;

D: {fr3,fr2,fr1} = 3'b000;

default: {fr3,fr2,fr1} = 3'b000;

endcase

end

//assign {fr3,fr2,fr1} = {!s[1],!s[2],!s[3]};//不能根据输入判断否则会提前一会时钟

// dfr信号:需使用时序逻辑电路,使用组合逻辑电路结果将提前一拍,结果不正确

// assign dfr = (state < next_state) ? 1'b0 : 1'b1; //使用组合逻辑电路结果不正确

always@(posedge clk)

begin

if(reset)

dfr <= 1;

else begin

if(next_state < state) //下一个状态next_state如果小于state,则代表水位减小,因此dfr增加

dfr <= 1;

else if(next_state > state)

dfr <= 0;

else

dfr <= dfr;

end

end

endmodule

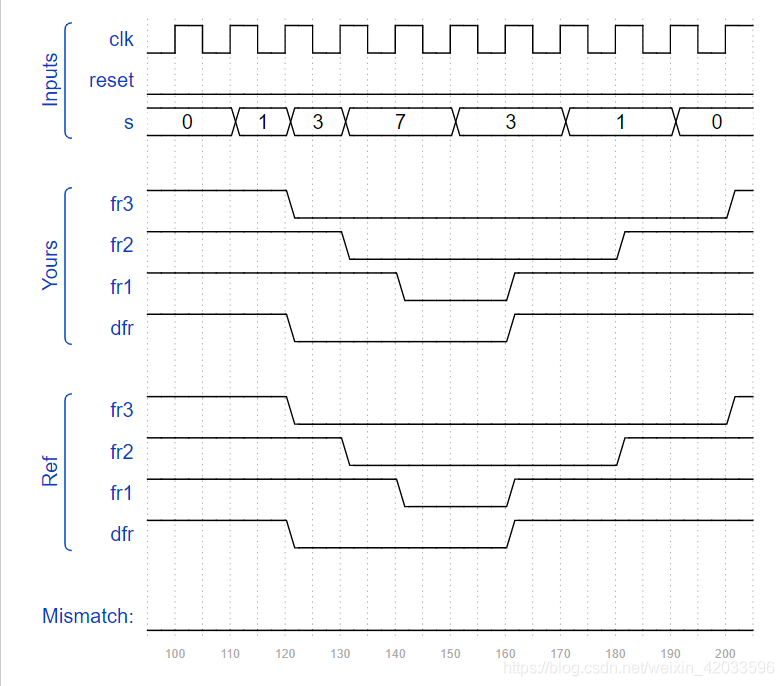

仿真结果如下:

如果 使用assign {fr3,fr2,fr1} = {!s[1],!s[2],!s[3]};则不{fr3,fr2,fr1}的结果提前一会时钟,图片如下

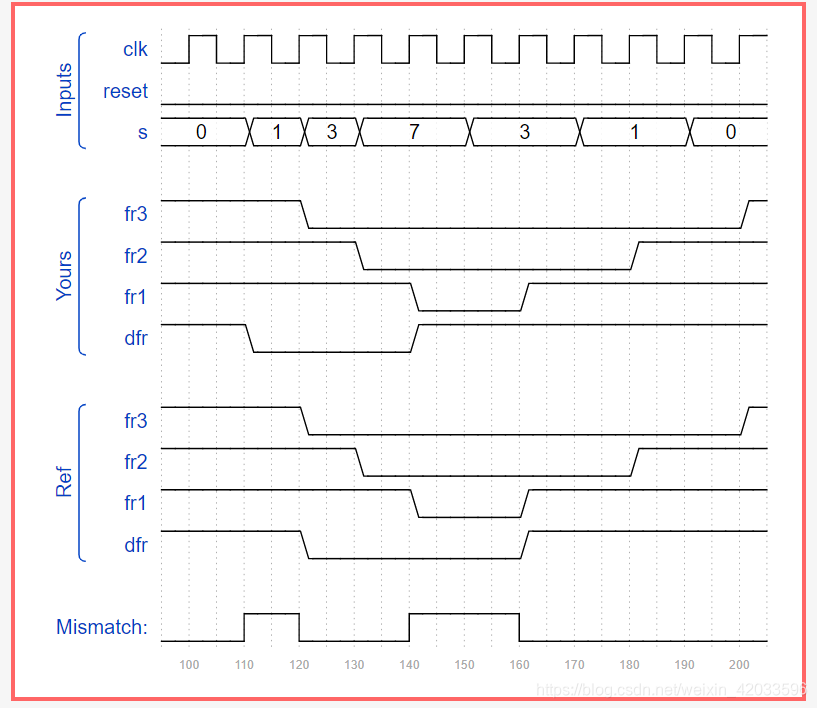

如果使用assign dfr = (state < next_state) ? 1’b0 : 1’b1; 使用组合逻辑电路dfr结果不正确图片如下:

872

872

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?