作者:OpenS_Lee

1背景知识

在我们的FPGA设计项目中,硬件的诊断和校验可能会占去超过30%—40%的FPGA开发时间,FPGA的debug也是FPGA设计中重要的一环。掌握并灵活运用FPGA设计工具的debug功能也是加快FPGA设计的关键。

1.1 ILA(Integrated Logic Analyzer)

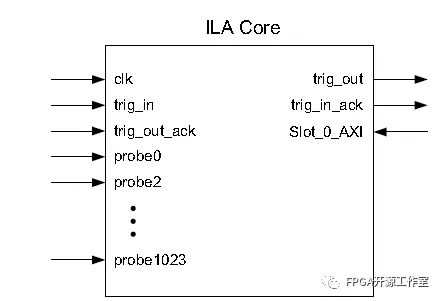

FPGA设计中的信号连接到ILA核的时钟和探针输入如图1。这些信号附加到探针输入,以设计速度采样,并使用片上块RAM(BRAM)存储。核参数指定探针的数量、跟踪样本深度和每个探针输入的宽度。使用与FPGA的JTAG接口连接的自动实例化调试核心集线器与ILA核进行通信。

图1 ILA Core

1.2 VIO (Virtual Input/Output core)

VIO核是一个可定制的核,可以实时监控和驱动内部FPGA信号。不像ILA核,不需要片上或片外RAM。

VIO核有两种类型的信号:

. Input probes

.Output probes

本文介绍了如何在FPGA设计中使用Xilinx Vivado的ILA和VIO核进行硬件诊断。ILA用于实时采样并存储内部信号,而VIO则能监控和驱动内部信号。通过ILA观察UART接收数据,通过VIO驱动UART发送数据,实现实时调试。文章提供了创建和配置ILA、VIO的步骤,并展示了调试过程。

本文介绍了如何在FPGA设计中使用Xilinx Vivado的ILA和VIO核进行硬件诊断。ILA用于实时采样并存储内部信号,而VIO则能监控和驱动内部信号。通过ILA观察UART接收数据,通过VIO驱动UART发送数据,实现实时调试。文章提供了创建和配置ILA、VIO的步骤,并展示了调试过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5112

5112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?