0 文章目录

1)MMCM/PLL简介

2)MMCM/PLL IP核定制

3)MMCM/PLL IP调用

4)结束语

1 MMCM/PLL简介

1)锁相环是什么?

锁相环作为一种反馈控制电路,其特点是利用外部输入的参考信号控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

2)xilinx 7系列FPGA时钟单元

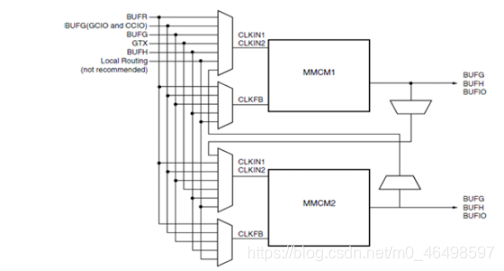

Xilinx 7 系列器件中具有时钟管理单元CMT 时钟资源,为设备提供强大的系统时钟管理以及高速I/O 通信的能力。时钟管理单元CMT如图1所示。

图1 时钟架构

说明:MMCM主要用于驱动器件逻辑(CLB、DSP、RAM 等)的时钟。PLL 主要用于为内存接口生成所需的时钟信号,但也具有

本文详细介绍了Xilinx 7系列FPGA中MMCM/PLL IP核的使用,包括锁相环的基本原理、时钟管理单元CMT的结构,以及如何在Vivado中定制和调用MMCM/PLL IP,提供了详细的配置步骤和例化模板操作指南。

本文详细介绍了Xilinx 7系列FPGA中MMCM/PLL IP核的使用,包括锁相环的基本原理、时钟管理单元CMT的结构,以及如何在Vivado中定制和调用MMCM/PLL IP,提供了详细的配置步骤和例化模板操作指南。

订阅专栏 解锁全文

订阅专栏 解锁全文

953

953

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?