今天紧接着上一篇博文继续介绍单比特信号跨时钟域的方法。

1.电平展宽(开环法)

电平展宽方法应用于快到慢场合,核心思想就是将输入信号持续时间拉长,以确保能够被接收时钟采样到。这里的开环是指由源时钟域决定输入信号究竟该展宽到何种程度。比如源时钟是100MHz,接收时钟是200MHz,那么对于源时钟域的任意单脉冲信号,只需要将其展宽到两个源时钟周期的长度即可。

2.电平展宽(闭环法)

输入信号何时结束展宽不由源时钟域决定,而是基于接收时钟域的反馈信号。有点像握手机制。

①源时钟域检测到输入信号后,将产生输入信号的映射sig_a,使之有效。sig_a不随输入信号的失效而失效。

②使用两级同步,将a时钟域的输入信号sig_a同步到b时钟域,产生同步信号sig_b

③sig_b再同步回a时钟域,产生反馈同步信号sig_b_a

④a时钟域接收到sig_b_a,将最原来的输入信号sig_a拉低。

推荐阅读“杰克淡定”的博文:Verilog基本电路设计之一(单bit跨时钟域同步) - 数字IC设计讨论(IC前端|FPGA|ASIC) - EETOP 创芯网论坛 (原名:电子顶级开发网) -

3.结绳法

结绳法分为三种:数据驱动结绳、数据SR结绳、握手协议结绳。

结绳法实现复杂,效率不高,对于高速率数据跨时钟域慎用。但是适用范围广,慢到快,快到慢都可以。

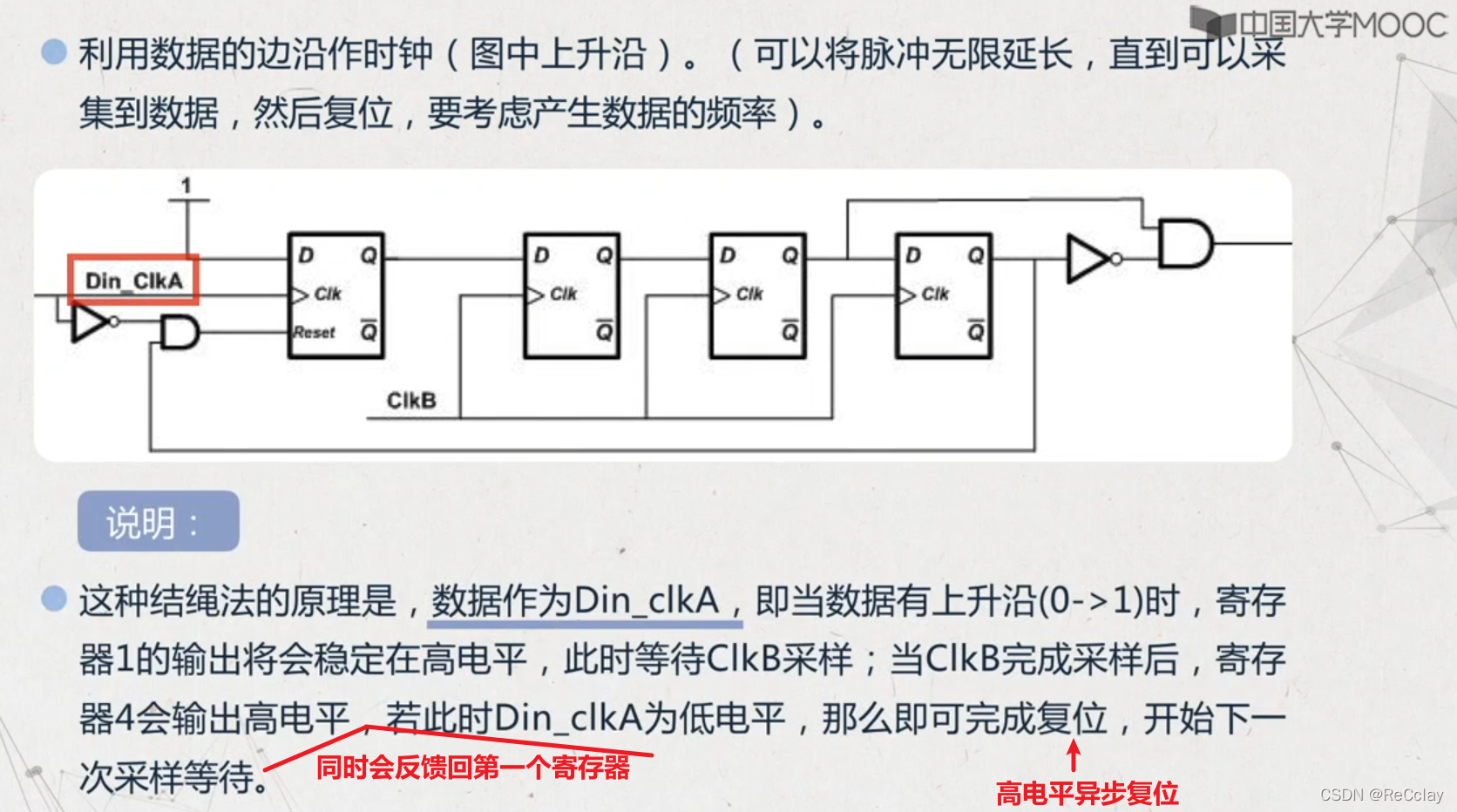

3.1数据驱动结绳

注意事项:输入信号的的翻转不能过快(最小电平宽度=3倍接收时钟周期),否则将丢失数据。

module data_clk(

input clk2,

input rst2,

input data,

output pluse_out

);

//-----------------clk1---

reg pluse_reg1;

reg clk2_r1,clk2_r2,clk2_r3;

wire rst1;

assign rst1 = clk2_r3 & ~data;

always @ (posedge data or posedge rst1)

if(rst1)

pluse_reg1 <= 1'b0;

else

pluse_reg1 <= 1'b1;

always@(posedge clk2 or negedge rst2 )

if(rst2)

{clk2_r1,clk2_r2,clk2_r3}<= 3'b000;

else

{clk2_r1,clk2_r2,clk2_r3} <= {pluse_reg1,clk2_r1,clk2_r2};

assign pluse_out = clk2_r2&&~clk2_r3;

endmodule

3.2数据SR结绳

参考文献:

(32条消息) 跨时钟域电路设计——结绳法_沧海一升的博客-CSDN博客_结绳法跨时钟域

抱歉,没看懂。引用一句我同学的话“对复位置位信号动手脚的都是瞎搞”。

3.3握手协议结绳。

本质上是两个脉冲同步器。源时钟域的单脉冲信号先同步到接收时钟域,然后又被同步回源时钟域,如此,源时钟域就知道自己发送的脉冲信号成功地被接收时钟域所接收。

如果只看上半部分,就是一个脉冲同步器了。

下一篇文章继续介绍跨时钟域的一种方法:握手法

6949

6949

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?